cpld的輸入電源電路

- cpld(168088)

相關推薦

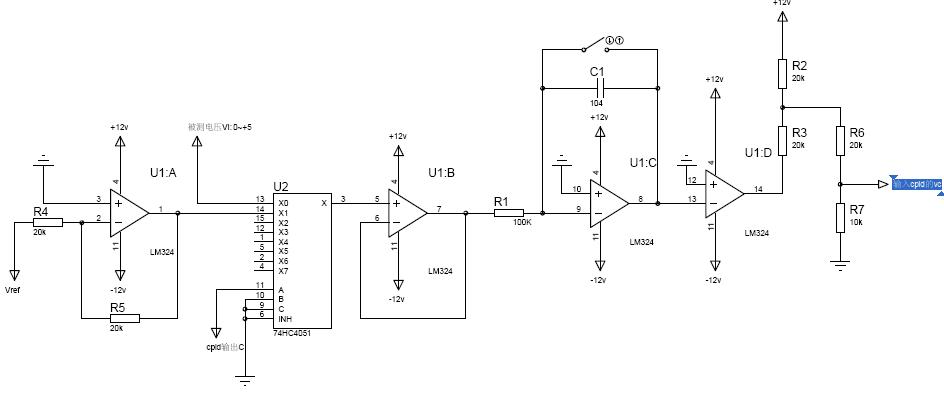

基于CPLD技術的MOSFET器件保護電路的設計方案

介紹了一種基于CPLD技術的MOSFET器件保護電路的設計與實現(xiàn)。該電路設計方案具有抗干擾能力強、響應速度快和通用性好的優(yōu)點。通過試驗驗證了該方案的正確性和可行性。##在功率MOSFET保護電路輸入

2014-04-25 11:15:47 1939

1939

1939

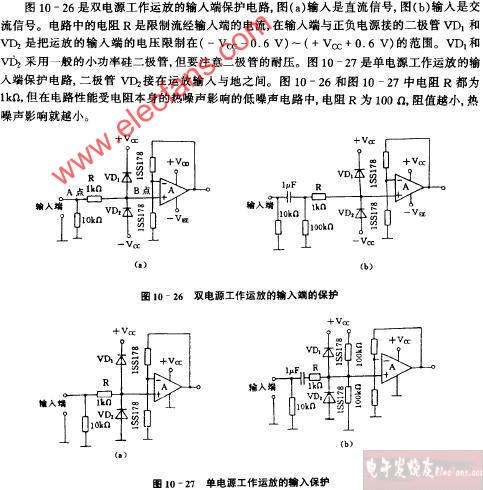

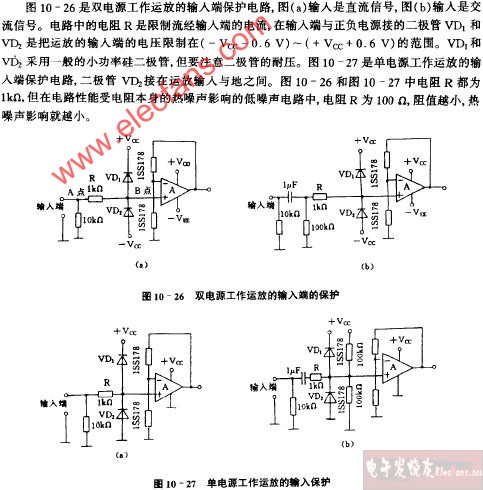

1939開關電源的電路組成、輸入電路的原理及常見電路

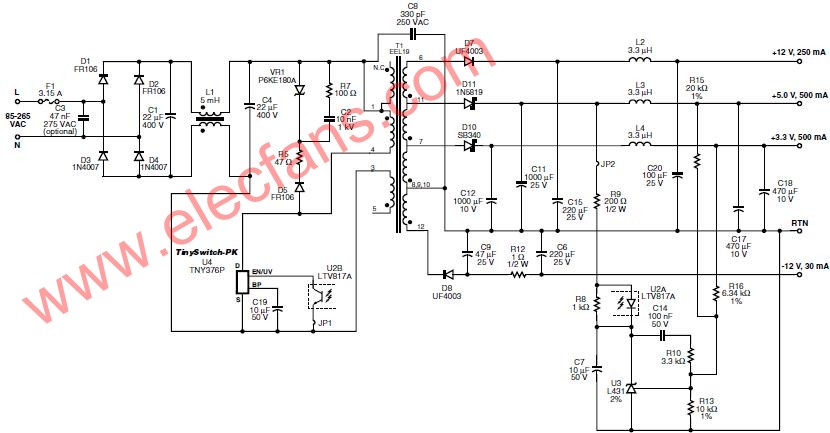

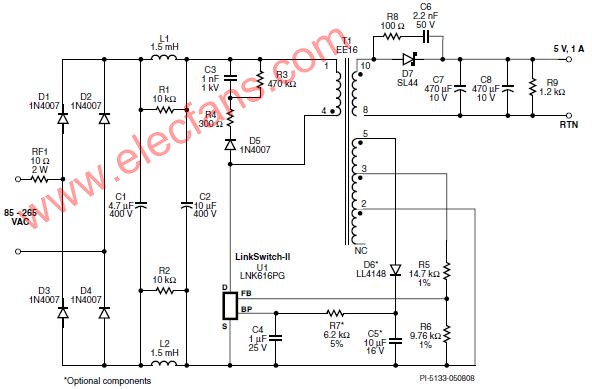

開關電源的主要電路是由輸入電磁干擾濾波器(EMI)、整流濾波電路、功率變換電路、PWM控制器電路、輸出整流濾波電路組成。輔助電路有輸入過欠壓保護電路、輸出過欠壓保護電路、輸出過流保護電路、輸出短路保護電路等。

2022-10-08 11:30:25 2044

2044

2044

2044CPLD加51單片機讓系統(tǒng)更高效

。 最容易的電路設計方法不外乎是直接繪制電路原理圖。采用原理圖輸入,初學者甚至不需要額外學習就可以從事CPLD 設計。我們只需要在軟件平臺上從集成器件庫調出對應的器件,繪制相同的電路原理圖即可,實現(xiàn)

2012-01-17 16:48:45

CPLD咨詢

有沒有哪位大俠搞過CPLD,我咨詢個問題,有個帶LCD彩色顯示的板子,基本電路情況是這樣的,由于當初設計的局限性,使用的32位單片機引腳不夠用,沒有使用單片機直接和LCD相連接,而是把單片機

2016-12-23 18:51:28

cpld大神看過來。。。。。

構建一個激光靶對目標位置的編碼識別電路,就是將激光接收器的接收到的電信號輸入到cpld中,通過程序來識別出電信號的0和1代碼,求問怎么搭建cpld電路和編程識別0和1代碼。謝謝啦

2016-04-25 10:35:03

電源輸入的防護電路

一般的產(chǎn)品用的都是直流電源,像手持產(chǎn)品多是5V電源,一些小設備也是5V,大一些的設備12V的稍多一些,車載電子產(chǎn)品有12V和24V兩種電源。 這些電源輸入的防護電路主要包括過壓保護,過流保護,防反

2021-11-17 08:27:52

FPGA CPLFPGA CPLD 數(shù)字電路設計經(jīng)驗分享

FPGA CPLFPGA CPLD 數(shù)字電路設計經(jīng)驗分享FPGA/CPLD數(shù)字電路設計經(jīng)驗分享摘要:在數(shù)字電路的設計中,時序設計是一個系統(tǒng)性能的主要標志,在高層次設計方法中,對時序控制的抽象度也相應

2012-08-11 10:17:18

FPGA/CPLD數(shù)字電路設計經(jīng)驗分享

本帖最后由 xianer317 于 2014-6-21 19:34 編輯

FPGA/CPLD數(shù)字電路設計經(jīng)驗分享

2014-06-21 19:33:20

FPGA與CPLD的區(qū)別

地說,F(xiàn)PGA就是將CPLD的電路規(guī)模,功能,性能等方面強化之后的產(chǎn)物。

一般而言,CPLD與FPGA之間的區(qū)別的如下所示(當然也有例外)。

PLD : Programmable Logic

2011-09-27 09:49:48

FPGA與CPLD的概念及基本使用和區(qū)別

/O單元互連結構,可由用戶根據(jù)需要生成特定的電路結構,完成一定的功能.由于 CPLD內(nèi)部采用固定長度的金屬線進行各邏輯塊的互連,所以設計的邏輯電路具有時間可預測性,避免了分段式互連結構時序不完全預測

2020-08-28 15:41:47

USB -CPLD開發(fā)板使用攻略

LDO:ASM1117-3.3 有源時鐘:50MHZ 全鉭電容電源濾波 本電路板適合人群: 1. 學習USB2.0通信技術的開發(fā)者 2. 學習CPLD 學習開發(fā)者 3. 高速數(shù)據(jù)采集開發(fā)應用者 4.8051 單片機學習者

2012-08-15 14:44:47

xilinx XA2C128 CPLD其他通用IO是否可以用作CPLD的時鐘輸入?

/置位,GCK =全局時鐘,CDRST =時鐘分頻復位等。我的問題是 - 1)我知道GSR,GCK,GTS引腳可以用作通用IO。但我想知道其他通用IO是否可以用作CPLD的時鐘輸入?或者是否存在一些限制

2019-04-12 06:09:36

供電電源對CPLD的輸出波形影響

本人自己設計了一個3.3V的直流電源,給CPLD供電會出現(xiàn)輸出波形雜亂的現(xiàn)象,但是使用外接移動電源輸出波形就會正常,設計的電路圖和輸出的波形圖如圖。想問一下供電電源對芯片輸出的影響,是否有大神遇到類似的情況。

2018-01-09 09:43:20

基于CPLD的數(shù)據(jù)采集與顯示接口電路仿真設計

/模轉換器DAC0832構成一個數(shù)據(jù)采集系統(tǒng),并用CPLD/FPGA實現(xiàn)數(shù)據(jù)采樣、D/A轉換輸出、有關數(shù)據(jù)顯示的控制,單片機完成對A/D轉換數(shù)據(jù)運算。電路如圖1所示。系統(tǒng)功能如下:系統(tǒng)按一定速率采集輸入

2018-12-10 10:18:34

基于CPLD的時柵位移傳感器應用

作者:陳春生基于CPLD的數(shù)字信號處理電路 智能時柵位移傳感器內(nèi)部基于CPLD的數(shù)字信號處理電路。電路采用雙MCU+CPLD結構設計,內(nèi)部嵌入主從式兩塊單片機,副MCU負責數(shù)據(jù)采集與預處理工作,主

2019-07-17 07:01:38

基于CPLD節(jié)省電池能量的系統(tǒng)斷電電路設計

的應用邏輯以外(圖中未畫),CPLD的電源控制邏輯增加了一對標準參數(shù)的庫宏電路,它由Altera的Quartus II開發(fā)工具生成。內(nèi)部的4.4MHz±25%振蕩器Altufm_osc驅動一個模塊化44

2018-09-26 17:29:24

如何利用CPLD器件設計單穩(wěn)態(tài)電路?

隨著電子技術特別是數(shù)字集成電路技術的迅猛發(fā)展,市面上出現(xiàn)了FPGA、CPLD等大規(guī)模數(shù)字集成電路,并且其工作速度和產(chǎn)品質量不斷提高。利用大規(guī)模數(shù)字集成電路實現(xiàn)常規(guī)的單穩(wěn)態(tài)集成電路所實現(xiàn)的功能,容易

2019-08-16 06:12:46

如何將LPC2114連接到CPLD再連接到其它電路呢?

現(xiàn)在數(shù)字電路除 LPC2114 使用 3.3V 電壓外,其余的大部分是 5V 的.我想先將 LPC2114連接到 cpld,再連接到其它電路(CPLD 的 I/O 口可以輸出或輸入 5V)不知道行不行。謝謝

2023-02-27 10:00:18

怎么利用FPGA和CPLD數(shù)字邏輯實現(xiàn)ADC?

數(shù)字系統(tǒng)的設計人員擅長在其印制電路板上用FPGA和CPLD將各種處理器、存儲器和標準的功能元件粘合在一起來實現(xiàn)數(shù)字設計。除了這些數(shù)字功能之外,F(xiàn)PGA和CPLD還可以使用LVDS輸入、簡單的電阻電容(RC)電路和一些FPGA或CPLD的數(shù)字邏輯單元實現(xiàn)共模功能,從而構建模數(shù)轉換器(ADC)。

2019-08-19 06:15:33

請問如何使用CPLD和STM32單片機設計一個具有12路信號輸入接口的板卡?

最近有一個小題目:使用CPLD和STM32單片機設計一個具有12路信號輸入接口的板卡(每一個接口都是獨立的,具有自己的固定地址),當隨機接入1~4路方波信號時,CPLD可以快速判斷是12路接口

2018-06-27 15:24:06

運放輸入端浮空的問題

CPLD的輸入。懷疑是哪里短路了,就開始測試電壓和各種關聯(lián)信號,沒有發(fā)現(xiàn)問題。那就繼續(xù)向前找,2410的輸入是一個運放芯片(雙電源供電+-15V),用萬用表測試,當時驚呆了,在沒有接輸入的情況下,運放居然

2016-03-04 21:15:17

CPLD在多路高速同步數(shù)據(jù)采集系統(tǒng)中的應用

采用VHDL 語言設計,用CPLD 控制模/ 數(shù)轉換電路, 完成多路模擬輸入的高速同步數(shù)/ 模轉換,具有容錯和自檢能力。CPLD 與處理器之間采用并行接口,具有很好的移植性、可靠性。

2009-04-16 10:44:25 7

7

7

7CPLD 在多路高速同步數(shù)據(jù)采集系統(tǒng)中的應用

采用VHDL 語言設計,用CPLD 控制模/ 數(shù)轉換電路, 完成多路模擬輸入的高速同步數(shù)/ 模轉換,具有容錯和自檢能力。CPLD 與處理器之間采用并行接口,具有很好的移植性、可靠性。

2009-05-15 13:10:35 18

18

18

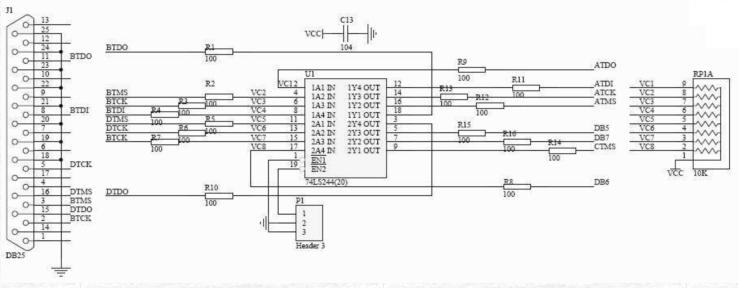

18基于ARM9 和CPLD 的輸入輸出系統(tǒng)設計

介紹了一種基于ARM9 和CPLD 架構的嵌入式輸入輸出系統(tǒng)的軟硬件設計。系統(tǒng)以工業(yè)級EP9315 為核心,擴展了LCD、觸摸屏、以太網(wǎng)、串口和USB 等控制接口;以MAX2_EPM240為核心,進行了

2009-06-01 10:55:12 21

21

21

21基于CPLD的計算機接口電路設計技巧

本文介紹了利用計算機ISA、PCI總線和打印機接口設計密碼電路。基于CPLD設計密碼電路,具有加密性能好的特性。通過并行打印機接 口設計一個密碼電路,密碼存儲在電路中,通過操

2009-06-12 15:00:58 28

28

28

28基于CPLD的計數(shù)及LED譯碼電路

本文采用VHDL語言設計了基于CPLD的計數(shù)及LED譯碼電路,該設計方法符合電子系統(tǒng)設計的發(fā)展方向。關鍵詞:計數(shù)器;LED譯碼;CPLD;VHDL在各種檢測與控制系統(tǒng)及儀表中,對發(fā)生的事

2009-08-24 08:32:39 28

28

28

28基于ARM9和CPLD的輸入輸出系統(tǒng)設計

介紹了一種基于ARM9 和CPLD 架構的嵌入式輸入輸出系統(tǒng)的軟硬件設計。系統(tǒng)以工業(yè)級EP9315 為核心,擴展了LCD、觸摸屏、以太網(wǎng)、串口和USB 等控制接口;以MAX2_EPM240為核心,進行了

2009-12-22 11:33:23 30

30

30

30嵌入式CPU外圍接口電路的CPLD實現(xiàn)

摘要:介紹了一種采用CPLD實現(xiàn)嵌入式CPU外圍電路的方法,將數(shù)據(jù)總線、譯碼單元、分頻電路及邏輯電路集成于一片CPLD,大大縮小了印制板的面積并提高了系統(tǒng)可靠性,同時,由于CPLD

2010-05-10 09:23:49 29

29

29

29基于CPLD的數(shù)字觸發(fā)電路的設計

摘要:利用大規(guī)模可編程控制器(Complex Programmable Logic Device)CPLD.針對靜止補償器(STATCOM)對觸發(fā)脈沖信號的要求.設計一種基于CPLD的正弦脈寬調制(SPwM)數(shù)字觸發(fā)電路。正弦調制波的產(chǎn)

2010-05-14 09:33:55 21

21

21

21CPLD器件的配置與編程下載

當利用CPLD/FPGA開發(fā)系統(tǒng)完成數(shù)字電路或系統(tǒng)的開發(fā)設計并仿真校驗通過之后,就需要將獲得的CPLD/FPGA編程配置數(shù)據(jù)下載到CPLD/FPGA芯片中,以便最后獲得所設計的硬件數(shù)字電路或系

2010-06-01 10:14:46 23

23

23

23ADS8323與高速FIFO接口電路的CPLD實現(xiàn)

以CPLD為邏輯控制核心實現(xiàn)了ADS8323與高速FIFO的接口電路,該電路具有可靠性高、通用性強、易于移植等特點。在設計過程中,以QuartusII作為開發(fā)環(huán)境,采用圖形輸入和Verilog HDL語言輸

2010-08-06 14:25:53 22

22

22

22換體DMA高速數(shù)據(jù)采集電路的CPLD實現(xiàn)

換體DMA高速數(shù)據(jù)采集電路的CPLD實現(xiàn)

介紹了換體DMA高速數(shù)據(jù)采集電路原理及其CPLD實現(xiàn)。用CPLD設計雙端口RAM緩存、控制譯碼、時序邏輯電路,很好地解決了電路元件所占體積

2009-03-28 15:09:18 666

666

666

666

什么是CPLD?CPLD是什么意思?

什么是CPLD

CPLD(Complex Programmable Logic Device)是Complex PLD的簡稱,一種較PLD為復雜的邏輯元件。CPLD是一種用戶根據(jù)各自

2009-03-30 13:40:43 3143

3143

3143

3143VHDL語言在FPGA/CPLD開發(fā)中的應用?

【摘 要】 通過設計實例詳細介紹了用VHDL(VHSIC Hardware DescriptionLanguage)語言開發(fā)FPGA/CPLD的方法,以及與電路圖輸入和其它HDL語言相比,使用VHDL語言的優(yōu)越性。

2009-05-10 19:47:30 1111

1111

1111

1111

基于CPLD技術的看門狗電路的設計

【摘 要】 介紹了一種基于CPLD器件設計看門狗電路的方法。 關鍵詞:CPLD,看門狗,計數(shù)器

1 引 言 隨著現(xiàn)代電子技

2009-05-16 19:18:28 700

700

700

700

換體DMA高速數(shù)據(jù)采集電路原理及其CPLD實現(xiàn)

摘要:介紹了換體DMA高速數(shù)據(jù)采集電路原理及其CPLD實現(xiàn)。用CPLD設計雙端口RAM緩存、控制譯碼、時序邏輯電路,很好地解決了電路元件所占體積大、電路復雜、不能實現(xiàn)在線

2009-06-20 15:12:07 878

878

878

878

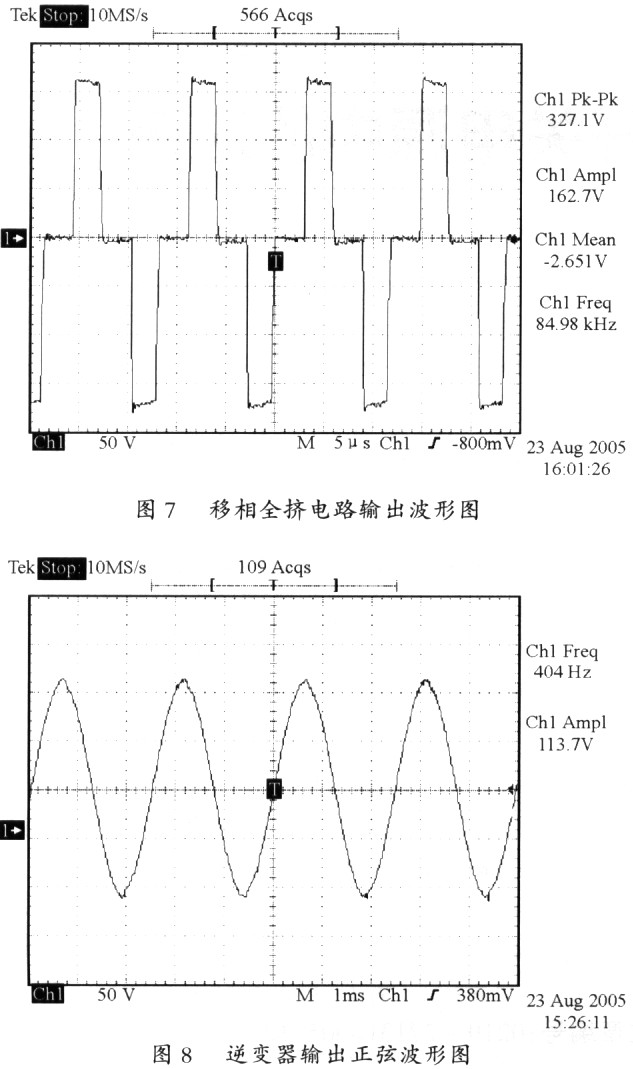

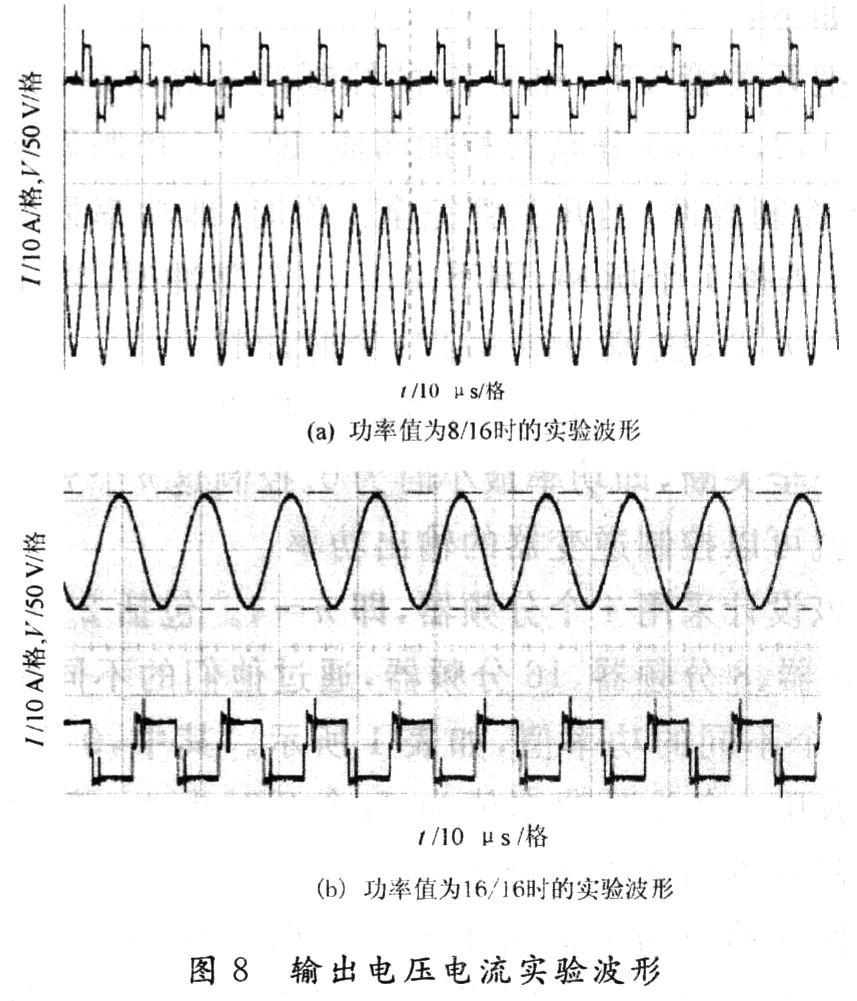

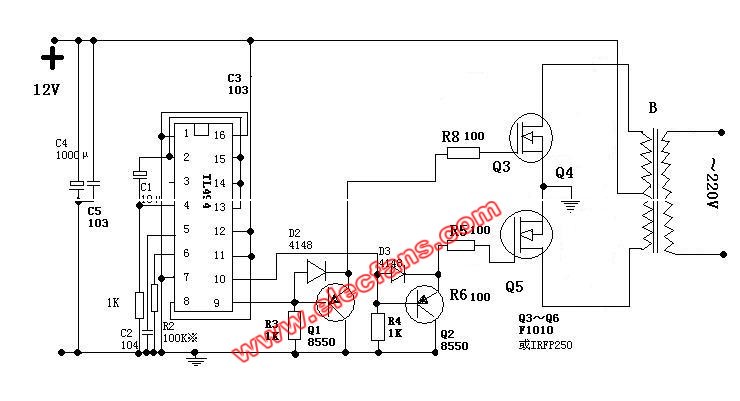

CPLD在航空15V/400Hz高頻鏈逆變電源中的應用

CPLD在航空15V/400Hz高頻鏈逆變電源中的應用介紹了一種基于CPLD的,用于大功率航空逆變電源的,觸發(fā)電路的設計原理和設計方法。實

2009-10-09 09:29:48 826

826

826

826

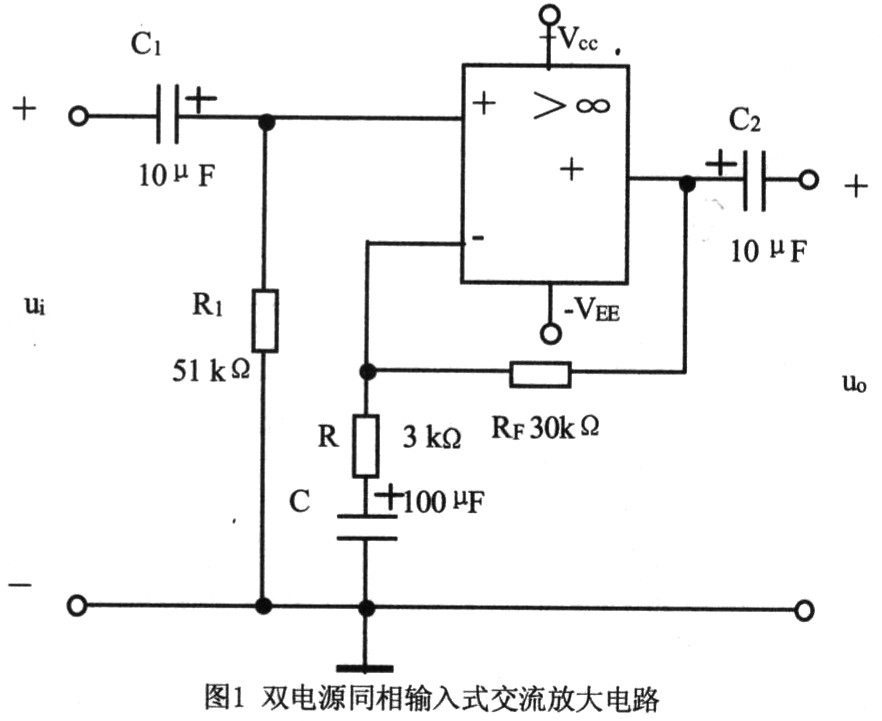

雙電源同相輸入式交流放大電路

雙電源同相輸入式交流放大電路

圖1是使用雙電源的同相輸入式交流放大電路。兩組電源電壓VCC和VEE相等。C1和C2為輸入和輸出耦合電容;R1使運放同相輸入端

2009-10-25 10:42:03 4718

4718

4718

4718

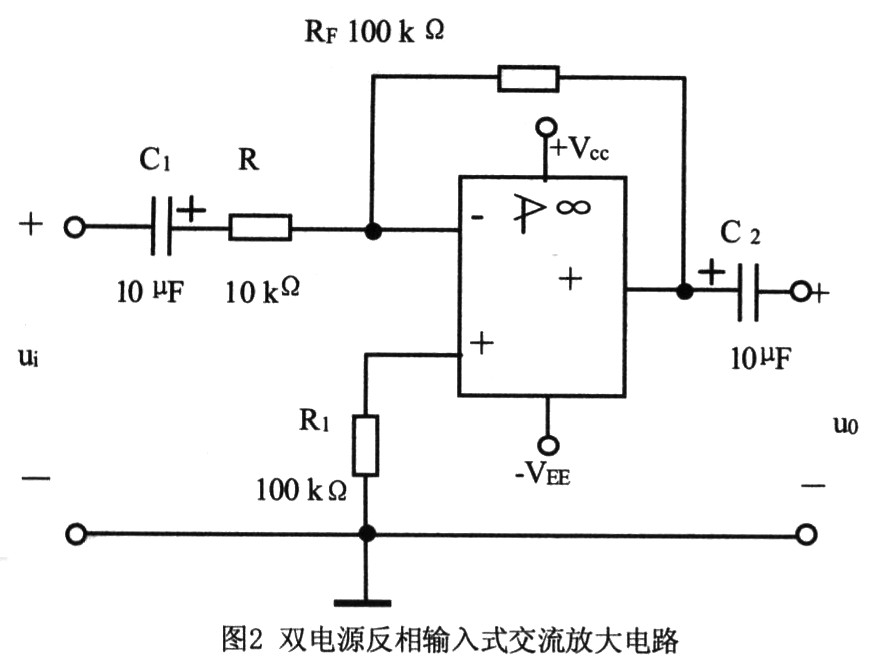

雙電源反相輸入式交流放大電路

雙電源反相輸入式交流放大電路

圖2是使用雙電源的反相輸入式交流放大電路。兩組電源電壓VCC和VEE相等。RF引入直流和交流負反饋,C1隔直流,使直流形成全反饋

2009-10-25 10:42:32 2829

2829

2829

2829

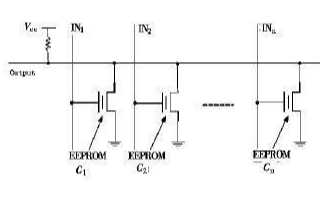

CPLD邏輯電路

CPLD邏輯電路 圖6是CPLD內(nèi)部邏輯電路,CPLD選用的是LATTICE公司的ispLSI1016E,邏輯設計采用原理圖輸入法,主要功能是對MUX的通道進行選擇、對A/D轉換器進

2009-11-13 12:04:13 2502

2502

2502

2502

基于CPLD的脈沖密度功率調節(jié)高頻逆變電源

基于CPLD的脈沖密度功率調節(jié)高頻逆變電源

0 引 言 目前,高頻感應加熱電源的輸出功率調整主要是通過改變逆變器的輸出頻率或改變逆變器的輸入直流

2009-11-18 16:20:02 1271

1271

1271

1271

采用CPLD的光伏逆變器鎖相及保護電路設計

采用CPLD的光伏逆變器鎖相及保護電路設計

0 引言

在光伏并網(wǎng)系統(tǒng)的逆變器電路中,對電網(wǎng)電壓的鎖相是一項關鍵技術。由于電力系統(tǒng)在

2010-03-03 10:53:16 1573

1573

1573

1573

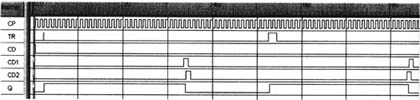

基于CPLD器件設計的單穩(wěn)態(tài)電路

隨著電子技術特別是數(shù)字集成電路技術的迅猛發(fā)展,市面上出現(xiàn)了FPGA、CPLD等大規(guī)模數(shù)字集成電路,并且其工作速度和產(chǎn)品質量不斷提高。利用大規(guī)模數(shù)字集成電路實現(xiàn)常規(guī)的

2010-07-16 11:06:27 1698

1698

1698

1698

基于MAX7000系列CPLD的數(shù)據(jù)采集系統(tǒng)

CPLD是復雜的PLD,專指那些集成規(guī)模大于1000門以上的可編程邏輯器件。它由與陣列、或陣列、輸入緩沖電路、輸出宏單元組成,具有門電路集成度高、可配置為多種輸入輸出形式、多

2010-10-21 10:15:43 3038

3038

3038

3038

CPLD實現(xiàn)線陣CCD驅動電路

采用MAXⅡ器件的EPM240T100C5N為控制核心,以TCD1500C為例,設計了基于CPLD的線陣CCD驅動電路,完成了硬件電路的原理圖的設計,并實現(xiàn)了軟件調試。通過QuartusⅡ軟件平臺,對其進行了模擬仿真。實

2011-11-03 15:24:40 129

129

129

129基于CPLD器件的單穩(wěn)態(tài)脈沖展電路

具體介紹了基于CPLD 器件設計單穩(wěn)態(tài)窄脈沖展寬電路的詳細過程和這種單穩(wěn)態(tài)窄脈沖展電路的特點,給出了相應的時序仿真波形,提出了提高展寬脈沖寬度精確度的方法。

2011-12-17 00:23:00 35

35

35

35DC 輸入濾波電路原理圖

DC 輸入濾波電路原理圖如下所示: ① 輸入濾波電路:C1、L1、C2組成的雙型濾波網(wǎng)絡主要是對輸入電源的電磁噪聲及雜波信號進行抑制,防止對電源干擾,同時也防止電源本身產(chǎn)生的高頻

2012-05-31 10:37:22 9224

9224

9224

9224

輸入過欠壓保護電路原理圖

輸入過欠壓保護電路原理圖如下所示: 1、 原理圖: 2、 工作原理: AC輸入和DC輸入的開關電源的輸入過欠壓保護原理大致相同。保護電路的取樣電壓均來自輸入濾波后的電壓。 取樣電

2012-05-31 11:16:15 20964

20964

20964

20964

FPGA和CPLD的區(qū)別及其用途介紹

FPGA/CPLD能完成任何數(shù)字器件的功能,上至高性能CPU,下至簡單的74電路,都可以用FPGA/CPLD來實現(xiàn)。 FPGA/CPLD如同一張白紙或是一堆積木,工程師可以通過傳統(tǒng)的原理圖輸入

2017-10-09 09:52:20 14

14

14

14基于CPLD的振蕩器實現(xiàn)設計應用

CPLD內(nèi)部施密特觸發(fā)器電器特性見表1。目前大部分使用的CPLD都需要兩個電源VCC和VCCIO,VCC就是CPLD內(nèi)部的核電壓,VCCIO是CPLD所有I/O 引腳電壓。

2018-05-11 08:22:00 1256

1256

1256

1256

基于fpga和cpld低頻/最小邏輯ADC實現(xiàn)

數(shù)字系統(tǒng)的設計人員擅長在其印制電路板上用FPGA和CPLD將各種處理器、存儲器和標準的功能元件粘合在一起來實現(xiàn)數(shù)字設計。除了這些數(shù)字功能之外,F(xiàn)PGA和CPLD還可以使用LVDS輸入、簡單的電阻電容(RC)電路和一些FPGA或CPLD的數(shù)字邏輯單元實現(xiàn)共模功能,從而構建模數(shù)轉換器(ADC)。

2018-04-26 11:53:00 1121

1121

1121

1121

基于CPLD的看門狗電路電路設計實現(xiàn)

隨著CPLD器件被廣泛應用于各種儀器、儀表設備的設計中,而且CPLD幾乎可模擬任何一種邏輯電路,所以,現(xiàn)在在設計時已完全沒有必要再放置一片獨立的看門狗器件,而完全可以將硬件看門狗電路整合于CPLD器件中,從而節(jié)省成本,降低系統(tǒng)的設計風險。下面具體介紹這種基于CPLD技術的看門狗電路的設計。

2018-03-05 16:58:01 2420

2420

2420

2420

在嵌入式設計中如何降低CPLD的功耗與電源電壓管理技術分析

我們首先來了解在嵌入式設計中如何降低CPLD的功耗、電路板的面積和元器件成本。下一步,我們將看到在待機模式下如何盡量降低CPLD的功耗,不僅要仔細地選擇器件,而且還要選擇一個合適的總線駐留方案。器件工作期間,我們對節(jié)省功耗的探討將包括選擇邏輯門、智能I/O設計和精密的電源電壓管理技術。

2018-12-04 09:09:00 2142

2142

2142

2142

基于CPLD的測試系統(tǒng)接口設計

介紹了一種用CPLD(復雜可編程邏輯器件)作為核心控制電路的測試系統(tǒng)接口,通過時cPLD和竹L電路的比較及cPLD在系統(tǒng)中實現(xiàn)的強大功能,論述了CPLD在測試系統(tǒng)接口中應用的可行性和優(yōu)越性,簡單介紹

2019-01-01 16:18:00 1472

1472

1472

1472

你需要知道基于CPLD節(jié)省電池能量的系統(tǒng)斷電電路的設計

元件,實現(xiàn)一個節(jié)省電池能量的系統(tǒng)斷電電路。在本例中,使用的CPLD是Altera EPM570-T100。使用一只外接P溝道MOSFET Q1和一只國際整流器公司 的IRLML6302(或等效器件),構成IC1 CPLD的一個電源控制開關。

2019-04-18 16:00:42 516

516

516

516

采用5管單元的SRAM結構實現(xiàn)CPLD可編程電路的設計

顯然,設計基于SRAM編程技術的CPLD可以很好解決上述應用問題。CPLD的設計和實現(xiàn)的關鍵問題是核心可編程電路結構的實現(xiàn)。因此,本文主要探討針對CPLD的核心可編程結構,如何設計具有相似功能且基于SRAM編程技術的電路結構,從而更好滿足動態(tài)重構系統(tǒng)中實現(xiàn)復雜狀態(tài)機和譯碼電路的應用。

2020-04-25 10:21:00 1687

1687

1687

1687

Altera FPGA CPLD學習筆記

Altera FPGA CPLD學習筆記(肇慶理士電源技術有限)-Altera FPGA CPLD學習筆記? ? ? ? ? ? ? ? ?

2021-09-18 10:54:41 79

79

79

79FPGA CPLD數(shù)字電路設計經(jīng)驗分享.

FPGA CPLD數(shù)字電路設計經(jīng)驗分享.(電源技術發(fā)展怎么樣)-FPGA CPLD數(shù)字電路設計經(jīng)驗分享? ? ? ? ? ? ? ? ? ??

2021-09-18 10:58:03 51

51

51

51FPGA CPLD中的Verilog設計小技巧

FPGA CPLD中的Verilog設計小技巧(肇慶理士電源技術有限)-FPGA CPLD中的Verilog設計小技巧? ? ? ? ? ? ? ? ?

2021-09-18 16:49:18 35

35

35

35cpld和單片機在脈沖開關電源中的應用

cpld和單片機在脈沖開關電源中的應用(通用電源技術_深圳有限公司)-cpld和單片機在脈沖磁鐵開關電源中的應用.pdf

2021-09-29 16:39:06 20

20

20

20輸入電源AD采樣電路誤差大及溫度影響分析

輸入電源AD采樣電路誤差大及溫度影響分析一、 問題點軟件實際測試過程中發(fā)現(xiàn),16V時,測試到的IO口處的電壓偏離理論最小值,不符合理論,導致電源管理功能異常。二、 電路三、 理論計算分析通過建立

2022-01-07 11:37:33 15

15

15

15輸入電路的原理及常見電路

輸入濾波電路:C1、L1、C2、C3組成的雙π型濾波網(wǎng)絡主要是對輸入電源的電磁噪聲及雜波信號進行抑制,防止對電源干擾,同時也防止電源本身產(chǎn)生的高頻雜波對電網(wǎng)干擾。當電源開啟瞬間,要對C5充電,由于瞬間電流大,加RT1(熱敏電阻)就能有效的防止浪涌電流。

2023-04-16 10:26:29 1708

1708

1708

1708UPS電源的輸入整流電路是啥,成分有很大改善

,而且又采用移相式控制,所以輸入諧波電流較大,功率因數(shù)一般只有0.65左右。這種輸入電路一般用在10kVA以下的UPS中。UPS電源的輸入整流電路介紹另一種輸入電路

2023-04-04 15:30:13 1005

1005

1005

1005

FPGA/CPLD數(shù)字電路設計經(jīng)驗分享

電子發(fā)燒友網(wǎng)站提供《FPGA/CPLD數(shù)字電路設計經(jīng)驗分享.pdf》資料免費下載

2023-11-21 11:03:12 3

3

3

3 電子發(fā)燒友App

電子發(fā)燒友App

評論