基于VHDL語(yǔ)言的智能撥號(hào)報(bào)警器的設(shè)計(jì)

介紹了以EDA技術(shù)作為開發(fā)手段的智能撥號(hào)報(bào)警系統(tǒng)的實(shí)現(xiàn)。本系統(tǒng)基于VHDL語(yǔ)言,采用FPGA作為控制核心,實(shí)現(xiàn)了遠(yuǎn)程防盜報(bào)警。該報(bào)警器具有體積小、可靠性高、靈活性強(qiáng)等特點(diǎn)。

關(guān)鍵詞:VHDL語(yǔ)言 FPGA ASIC DTMF

目前,智能撥號(hào)報(bào)警器大多采用單片機(jī)作為控制核心,這種傳統(tǒng)設(shè)計(jì)方法的特點(diǎn)是硬件和軟件截然不同,設(shè)計(jì)中不可相互替代;而且硬件連線復(fù)雜,可靠笥較差。

硬件描述語(yǔ)言(VHDL)和可編程ASIC器件的廣泛應(yīng)用第一次打破了硬件和軟件的屏障。基于VHDL語(yǔ)言、以EDA技術(shù)作為開發(fā)手段、采用現(xiàn)場(chǎng)可編程門陣列FPGA(Field Porogrammable Gate Array)作為控制核心實(shí)現(xiàn)的與電話線連接的智能撥號(hào)遠(yuǎn)程報(bào)警器,與傳統(tǒng)設(shè)計(jì)相比較,不僅簡(jiǎn)化了接口和控制,提供了系統(tǒng)的整體性能和工作可靠性,也為進(jìn)一步提高系統(tǒng)集成創(chuàng)造了條件。

1 系統(tǒng)原理及組成

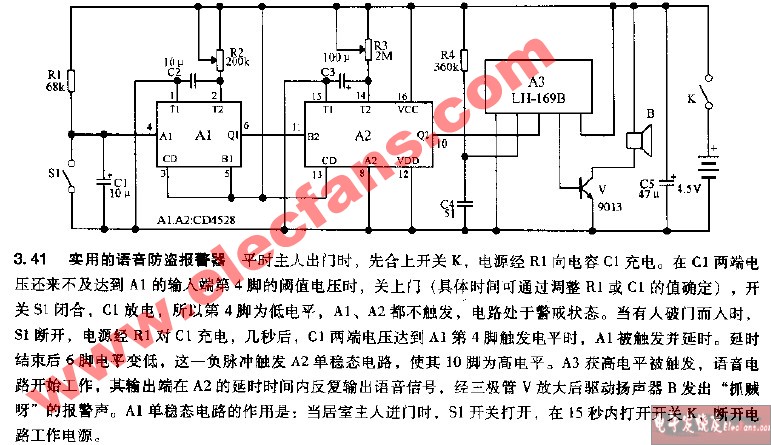

系統(tǒng)組成原理框圖如圖1所示。系統(tǒng)的控制核心是一片F(xiàn)PGA芯片,它由3個(gè)功能模塊構(gòu)成:電話信號(hào)音識(shí)別模塊,DTMF收發(fā)時(shí)序仿真模塊和摘機(jī)/掛機(jī)控制模塊。3個(gè)模塊的功能分別為識(shí)別電話系統(tǒng)送來(lái)的信號(hào)音、控制DTMF撥號(hào)電路自動(dòng)撥號(hào)、控制摘掛機(jī)電路完成摘掛機(jī)操作。

?

2 PFGA功能模塊設(shè)計(jì)

智能撥號(hào)報(bào)警器的控制核心FPGA的三個(gè)功能模塊皆用VHDL語(yǔ)言編程實(shí)現(xiàn),下面主要介紹FPGA的三個(gè)功能模塊的設(shè)計(jì)。

2.1 電話信號(hào)音識(shí)別模塊JUDGE

信號(hào)音判斷的實(shí)現(xiàn)原理是:由于電話系統(tǒng)信號(hào)音的撥號(hào)音、回鈴音和忙音的音源頻率均為450Hz(±25Hz)的正弦波,只是斷續(xù)比不同且在時(shí)間上有明顯的差異(撥號(hào)音為450Hz±25Hz連續(xù)信號(hào),忙音為 0.35s通0.35s斷,回鈴音為1s通4s斷)。要判斷信號(hào)音,首先應(yīng)將處理DTMF信號(hào)的MT8880芯片設(shè)置為呼叫處理模式,使電話呼叫過(guò)程中的各種信號(hào)音經(jīng)MT8880濾波、限幅后得到方波,并由MT8880的IRQ端輸出。然后對(duì)MT8880輸出的IRQ信號(hào)計(jì)數(shù)5秒,撥號(hào)音的計(jì)數(shù)下限為(450-25)×5=2125,計(jì)數(shù)上限為(450+25)×5=2375,即計(jì)數(shù)范圍為2125~2375。同理,忙音的計(jì)數(shù)范圍為 1041~1212,回鈴音的計(jì)數(shù)范圍為425~475,無(wú)信號(hào)音的計(jì)數(shù)應(yīng)為零。但在實(shí)際編程中,需要考慮一定的計(jì)時(shí)計(jì)數(shù)誤差,并且使程序簡(jiǎn)化,因此采用不同信號(hào)音相鄰計(jì)數(shù)界限的中間值為區(qū)分不同的信號(hào)音。同時(shí),為合理利用FPGA硬件資源,中間值應(yīng)盡量選為2的n次方(整數(shù))。最后設(shè)定為計(jì)數(shù)值大于 1792為撥號(hào)音,在1024~1791之間的忙音,在256~1023之間的回鈴音,小于255為無(wú)信號(hào)音。

基于此原理設(shè)計(jì)的信號(hào)音識(shí)別模塊JUDGE如圖2所示。

CLK為時(shí)鐘信號(hào)輸入端;IRQ與MT8880芯片的IRQ輸出端相連接,是IRQ信號(hào)的計(jì)數(shù)輸入端;PICK是摘機(jī)信號(hào)輸入端;BUSY為電話忙狀態(tài)標(biāo)志信號(hào)輸出端;DIAL是撥號(hào)使能信號(hào)端。該模塊的功能為:在摘機(jī)信號(hào)PICK產(chǎn)生大約1s后,即 MT8880芯片被設(shè)置為呼叫處理模式后啟動(dòng)該模塊。在該模塊的內(nèi)部,設(shè)置了兩個(gè)計(jì)數(shù)器。一個(gè)為對(duì)CLK時(shí)鐘信號(hào)進(jìn)行計(jì)數(shù),產(chǎn)生5s控制信號(hào);另一個(gè)對(duì) IRQ送來(lái)的脈沖進(jìn)行計(jì)數(shù)。兩個(gè)計(jì)數(shù)器由摘機(jī)信號(hào)PICK啟動(dòng),5s后判斷第二個(gè)計(jì)數(shù)器的計(jì)數(shù)值。如果計(jì)數(shù)值大于1792,則說(shuō)明電話交換機(jī)系統(tǒng)處于可撥號(hào)的狀態(tài),DIAL置為有效、BUSY置為無(wú)效,以觸發(fā)DTMF收發(fā)時(shí)序仿真模塊進(jìn)行撥號(hào)操作。否則,電話處于不可撥號(hào)的狀態(tài),DIAL無(wú)效、BUSY有效,驅(qū)動(dòng)摘/掛機(jī)模塊產(chǎn)生掛機(jī)信號(hào)。撥號(hào)音識(shí)別的部分VHDL程序如下:

process(irq,pick,stop)

variable cnt:integer;

constant lm_1792:integer:=1792;

begin

if(pick=‘0’);

dial<=‘0’;

cnt:=0;

elsif(stop and cnt<=lm_1792) then

dial<=‘0’;/*電話遇忙,發(fā)忙狀態(tài)標(biāo)志*/

busy<=‘1’;

elsif(stop and cnt>=lm_1792) then

dial<=‘1’;/*電話通,撥號(hào)使能有效*/

busy<=‘0’;

elsif(irq)'event and irq=‘1’) then

cnt:=cnt+1;/*電話音檢測(cè)計(jì)數(shù)*/

end if;

end process;

2.2 DTMF收發(fā)時(shí)序仿真模塊RECEI-SEND

MITEL 公司生產(chǎn)的集成芯片MT8880是專門用于處理DTMF信號(hào)的專用集成電路,具有接受和發(fā)送DTMF信號(hào)的雙重功能。在本系統(tǒng)中,MT8880的作用是:把電話系統(tǒng)送來(lái)的DTMF信號(hào)處理成FPGA能夠識(shí)別的邏輯信號(hào);將FPGA送出的用于撥號(hào)的TTL邏輯信號(hào)轉(zhuǎn)換成電話系統(tǒng)能夠識(shí)別的DTMF信號(hào)。

RECEI -SEND用于控制MT8880以實(shí)現(xiàn)按DTMF方式自動(dòng)撥預(yù)定的電話號(hào)碼。RECEI-SEND模塊與MT8880芯片的互連接口如圖3所示。二者的接口信號(hào)線直接連接并由RECEI-SEND模塊模擬產(chǎn)生MT8880芯片的各個(gè)接口信號(hào),完成DTMF信號(hào)的接收以及對(duì)電話線路撥號(hào)。MT8880的工作模式由內(nèi)部寄存器(CRA、CRB、SR、TDR和RDR)中的控制字決定,內(nèi)部寄存器的數(shù)據(jù)寫入和讀出都由R-W、CS、CP、RS。信號(hào)控制。當(dāng)MT8880芯片被訪問(wèn)時(shí),CP腳應(yīng)出現(xiàn)一次帶上升沿的高電平,其周期應(yīng)為1μs~1000μs。這是關(guān)鍵信號(hào),其它信號(hào)均以此信號(hào)作為依據(jù)。因此,F(xiàn)PGA的RECEI-SEND模塊模擬產(chǎn)生CP及其它信號(hào)的時(shí)序。圖4為RECEI-SEND模塊寫MT8880內(nèi)部寄存器CRA、CRB的時(shí)序。圖5是RECEI-SEND模塊控制MT8880發(fā)送DTMF信號(hào)時(shí)序。RECEI-SEND模塊的VHDL程序結(jié)構(gòu)如圖6所示。

2.3 摘/掛機(jī)控制模塊PICK

電話摘/掛機(jī)的實(shí)現(xiàn)是由摘/掛機(jī)控制模塊PICK控制摘/掛機(jī)電路來(lái)完成的。設(shè)計(jì)的PICK模塊如圖7所示。CLK是系統(tǒng)時(shí)鐘輸入;EN是人體檢測(cè)傳輸器采集的盜竊信號(hào)輸入;RESET是系統(tǒng)復(fù)位信號(hào)輸入;STOP為撥號(hào)完成的掛機(jī)控制信號(hào)輸入;BUSY為遇忙信號(hào)輸入;PICK為摘/掛機(jī)信號(hào)輸出。當(dāng)有盜竊發(fā)生時(shí),EN輸入信號(hào)有效,該模塊使摘機(jī)輸出信號(hào)PICK有效,從而驅(qū)動(dòng)摘/掛機(jī)電路產(chǎn)生摘機(jī)動(dòng)作。如果摘機(jī)后電話信號(hào)音識(shí)別模塊JUDGE送來(lái)的是系統(tǒng)忙的信號(hào),即UBSY輸入信號(hào)有效時(shí),輸出掛機(jī)信號(hào)PICK。兩秒鐘后重新啟動(dòng)摘機(jī),直到電話信號(hào)音為可撥號(hào)狀態(tài)。撥號(hào)完成后,STOP信號(hào)有效, PICK模塊產(chǎn)生掛機(jī)信號(hào)。當(dāng)RESET有效時(shí),掛機(jī)輸出信號(hào)有效。摘/掛機(jī)控制模塊PICK的部分VHDL程序如下:

process(clk,stop,busy,en,delay)

begin

if(clk'event and clk='1') then

if(reset='1' or stop='1') then

/*復(fù)位或撥號(hào)完成后掛機(jī)*/

pick<='0';

elsif(en='1') then /*報(bào)警信號(hào)觸發(fā)摘機(jī)*/

if(busy='0') then

pick<='1';

elsif(delay='1') then /*遇忙延時(shí)后重新摘機(jī)*/

pick<='1';

else

pick<='0'; /*遇忙掛機(jī)*/

end if;

end if;

end if;

end process;

3 系統(tǒng)設(shè)計(jì)和邏輯仿真

FPGA 中的3個(gè)功能模塊用VHDL語(yǔ)言描述進(jìn)行綜合仿真后,連接起來(lái)的系統(tǒng)電話原理圖如圖8所示。系統(tǒng)的工作過(guò)程:STEAL報(bào)警信號(hào)輸入PICK模塊,產(chǎn)生 PICK摘機(jī)信號(hào),控制摘機(jī)/掛機(jī)電路。摘機(jī)后,RECEI-SEND模塊將呼叫處理控制字寫入MT8880芯片中,將MT8880設(shè)置為叫處理模式。然后電話信號(hào)音識(shí)別模塊JUDGE對(duì)MT8880芯片的輸出信號(hào)IRQ計(jì)數(shù),判別電話音是否為撥號(hào)音。若非撥號(hào)音,產(chǎn)生電話忙信號(hào)BUSY至PICK模塊,輸出掛機(jī)信號(hào)PICK,電話掛機(jī)。然后摘機(jī)后重判,若為撥號(hào)音,則JUDGE模塊輸出撥號(hào)信號(hào)DIAL至RECEI-SEND模塊,RECEI-SEND 模塊模擬與MT880直接接口進(jìn)行數(shù)據(jù)通訊的DTMF收發(fā)時(shí)序,控制MT8880按預(yù)先設(shè)置的電話進(jìn)行自動(dòng)撥號(hào)。撥號(hào)后延時(shí),由JUDGE模塊判別電話音是否為電話回鈴音,若為電話回鈴音電話回鈴音,則延時(shí)掛機(jī)。若不是電話回鈴音,則掛機(jī)重?fù)堋?

本系統(tǒng)采用的FPGA芯片為XILINX公司的XCS30/XL,邏輯門數(shù)為1.3萬(wàn)門,用FOUNDATION2.1軟件工具開發(fā)。設(shè)計(jì)輸入完成后,進(jìn)行整體的編譯和邏輯仿真,然后進(jìn)行轉(zhuǎn)換、布局、布線、延時(shí)仿零點(diǎn)生成配置文件,最后下載至FPGA器件,完成結(jié)構(gòu)功能配置,實(shí)現(xiàn)其硬件功能。FPGA的系統(tǒng)邏輯功能仿真波形如圖9所示。各信號(hào)的邏輯功能和時(shí)序配合完全達(dá)到設(shè)計(jì)要求。

本系統(tǒng)是用FPGA實(shí)現(xiàn)的智能報(bào)警器,全部通過(guò)編譯仿真和系統(tǒng)測(cè)試。由于系統(tǒng)的很多邏輯功能由一片F(xiàn)PGA實(shí)現(xiàn),外圍器件很少,所以系統(tǒng)體積小、可靠性高,且器件的可編程性使得系統(tǒng)功能易于完善。隨著可編程ASIC器件的應(yīng)用范圍不斷擴(kuò)大,越來(lái)越多的產(chǎn)生在開發(fā)過(guò)程中都使用VHDL語(yǔ)言,綜使我們得以脫離底層電路,站在更高的層次上考慮各種邏輯和時(shí)序關(guān)系,從而快速完成設(shè)計(jì)。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論