基于CPLD的CCD驅(qū)動(dòng)電路自動(dòng)增益調(diào)整

ccd(charge couple device)是一種電荷藕合式光電轉(zhuǎn)換器件。在物體位移測量系統(tǒng)中,常常以ccd作為位移傳感器。當(dāng)一束曝光器發(fā)出的激光照射到被測物體上并發(fā)生漫反射時(shí),反射光將經(jīng)透鏡聚焦后成像在ccd上,以使ccd光敏單元感光,從而產(chǎn)生轉(zhuǎn)移電荷。這樣ccd驅(qū)動(dòng)電路就會(huì)產(chǎn)生一定頻率的驅(qū)動(dòng)脈沖以反映物體位移信息,輸出的信號(hào)為模擬信號(hào)。經(jīng)a/d轉(zhuǎn)換后,便可由后續(xù)處理電路采集和運(yùn)算。

實(shí)際測量工作中,由于工作環(huán)境、光照強(qiáng)度或被測物體的不同,會(huì)使得照射到被測物體表面的激光束的反射率變化比較大,因此,ccd上成像點(diǎn)的光強(qiáng)就會(huì)時(shí)強(qiáng)時(shí)弱。ccd光敏單元在過強(qiáng)或過弱光線照射下,會(huì)產(chǎn)生過飽和或不飽和的電荷,從而使輸出的模擬信號(hào)不能滿足數(shù)據(jù)采集要求,因而不能真實(shí)反映被測物體的位移信息,影響最后計(jì)算結(jié)果的準(zhǔn)確性,而產(chǎn)生了較大的誤差。鑒于以上原因,為了能夠得到準(zhǔn)確的被測物體的位移結(jié)果,應(yīng)使ccd測量系統(tǒng)輸出的模擬信號(hào)峰值盡量穩(wěn)定在某一范圍內(nèi)。

cpld復(fù)雜可編程邏輯器件具有集成度高,體積小,速度快等特點(diǎn)。通過cpld能夠以廠家提供的cad工具為開發(fā)平臺(tái),結(jié)合原理圖編輯與vhdl語言軟件編程,以在cpld中實(shí)現(xiàn)數(shù)字硬件中的大多數(shù)邏輯電路[1]。因此,本文所設(shè)計(jì)的ccd自動(dòng)增益系統(tǒng)的核心部分選用cpld來實(shí)現(xiàn)。

ccd信號(hào)的自動(dòng)增益調(diào)整

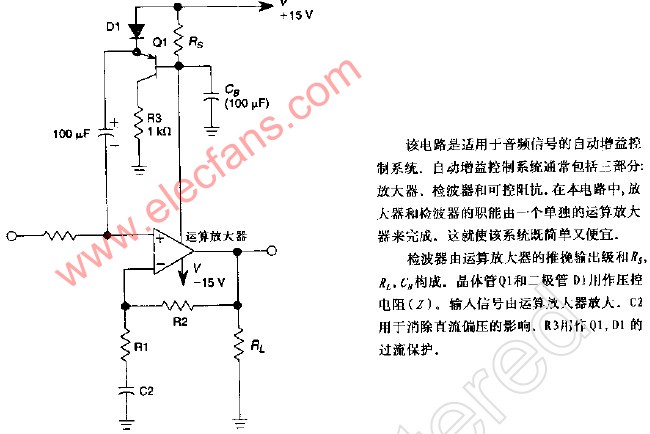

ccd傳感器輸出的模擬信號(hào)與入射光光強(qiáng)、幀轉(zhuǎn)移頻率有關(guān)。其大小隨入射光光強(qiáng)的增大而增大,隨幀轉(zhuǎn)移頻率的增大而減小,因此,通過改變?nèi)肷涔獾墓鈴?qiáng)或幀轉(zhuǎn)移頻率就可以調(diào)整輸出的模擬信號(hào)峰值。本系統(tǒng)就是采用調(diào)節(jié)幀轉(zhuǎn)移頻率來達(dá)到自動(dòng)增益調(diào)整的目的。

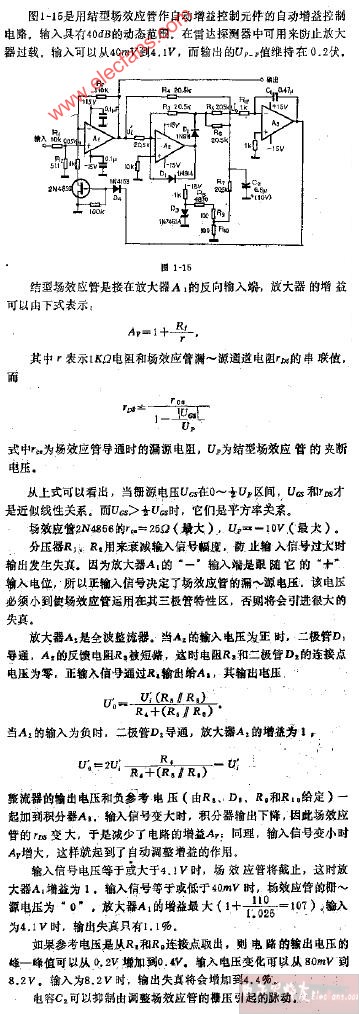

一般情況下,幀轉(zhuǎn)移脈沖由ccd驅(qū)動(dòng)電路輸出,其頻率大小直接影響ccd傳感器的積分時(shí)間。幀轉(zhuǎn)移頻率越小,傳感器積分時(shí)間越長,相應(yīng)地,ccd傳感器曝光時(shí)間也越長,光敏單元捕捉到的光量也越多。當(dāng)幀轉(zhuǎn)移頻率過小時(shí),光敏單元所產(chǎn)生的光電電荷就會(huì)達(dá)到過飽和狀態(tài),輸出的模擬電壓峰值將會(huì)超過所要求的范圍。反之,輸出的模擬電壓峰值將會(huì)低于所要求的范圍。因此,可設(shè)計(jì)一個(gè)ccd輸出電壓峰值的采樣、保持電路,再對(duì)此峰值進(jìn)行a/d轉(zhuǎn)換,同時(shí)與所要求的范圍進(jìn)行比較。當(dāng)其超出范圍值時(shí),可增大幀轉(zhuǎn)移頻率;而當(dāng)其值低于范圍時(shí),則可減小幀轉(zhuǎn)移頻率[2]。

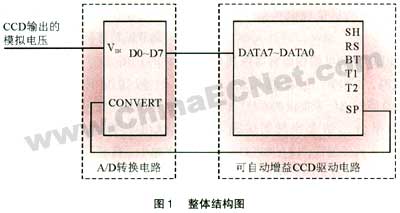

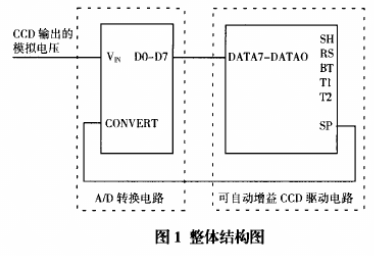

系統(tǒng)整體結(jié)構(gòu)

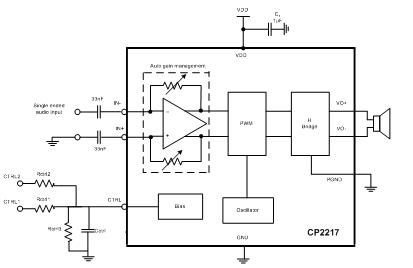

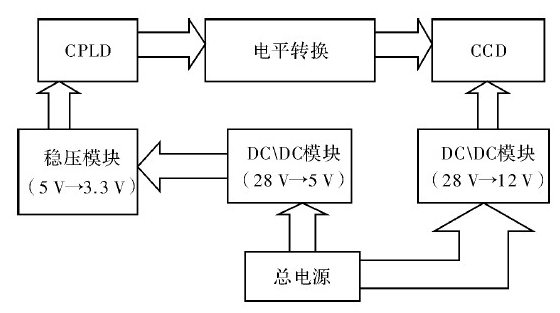

這種基于cpld的ccd自動(dòng)增益調(diào)整驅(qū)動(dòng)電路的整體結(jié)構(gòu)如圖1所示,該系統(tǒng)共分為兩部分。第一部分為模擬/數(shù)字轉(zhuǎn)換電路,該部分采用一個(gè)轉(zhuǎn)換精度為8位的a/d轉(zhuǎn)換器來將ccd輸出的模擬電壓值轉(zhuǎn)換為數(shù)字量。第二部分為可自動(dòng)調(diào)整增益的ccd驅(qū)動(dòng)電路,此部分采用cpld進(jìn)行配置,可自動(dòng)完成增益調(diào)整及ccd驅(qū)動(dòng)信號(hào)的輸出,并可為a/d轉(zhuǎn)換器提供轉(zhuǎn)換控制脈沖。

a/d轉(zhuǎn)換部分

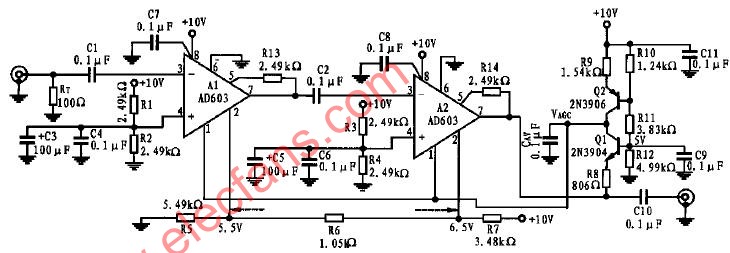

ccd的輸出信號(hào)為模擬量,故須經(jīng)a/d將其轉(zhuǎn)換成數(shù)字量,以便cpld進(jìn)行處理。在本設(shè)計(jì)中,a/d轉(zhuǎn)換器采用的ad9048可工作在35msps的高速上,由cpld產(chǎn)生的單位轉(zhuǎn)移脈沖sp可為其提供轉(zhuǎn)換控制脈沖convert。在convert的上升沿到來后,a/d9048對(duì)ccd相應(yīng)象素點(diǎn)上輸出的模擬電壓值進(jìn)行采樣,并在convert下降沿到來之前輸出轉(zhuǎn)換結(jié)果,該結(jié)果由cpld寄存并最終得到一幀中ccd輸出的模擬電壓峰值的大小。

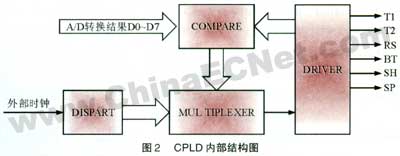

可自動(dòng)增益的ccd驅(qū)動(dòng)電路設(shè)計(jì)

此電路利用cpld設(shè)計(jì),其內(nèi)部可劃分為四個(gè)模塊(如圖2所示),整個(gè)芯片所需的時(shí)鐘由外部晶振或振蕩電路提供。

第一個(gè)分頻模塊dispart用于對(duì)外部時(shí)鐘進(jìn)行一到八倍的分頻。第二個(gè)模塊mul tiplexer是一個(gè)多選一模塊,由compare控制。第三個(gè)模塊compare用于對(duì)a/d轉(zhuǎn)換的結(jié)果進(jìn)行寄存,并將一幀結(jié)束后得到的ccd輸出電壓峰值與所設(shè)定的閾值進(jìn)行比較,若超出閾值上限則輸出結(jié)果減一,multiplexer選出頻率較高的一路時(shí)鐘作為driver的輸入時(shí)鐘脈沖;反之,則對(duì)compare的輸出結(jié)果加一,multiplexer選出頻率較低的一路時(shí)鐘作為driver的輸入時(shí)鐘脈沖。第四個(gè)模塊driver用來產(chǎn)生驅(qū)動(dòng)ccd的信號(hào)及一位單位轉(zhuǎn)移信號(hào)。

當(dāng)multiplexer選出頻率較高的一路脈沖作為driver的輸入時(shí)鐘,再由driver產(chǎn)生ccd驅(qū)動(dòng)信號(hào)時(shí),驅(qū)動(dòng)信號(hào)中的幀轉(zhuǎn)移脈沖sh頻率就會(huì)增加,從而使ccd傳感器的曝光時(shí)間變短,ccd輸出的模擬電壓峰值降低;反之,sh頻率減小,曝光時(shí)間變長,ccd輸出的模擬電壓峰值升高。這樣,通過以上過程,便可調(diào)節(jié)ccd模擬電壓峰值的范圍。

本設(shè)計(jì)應(yīng)用的ccd器件為tcd1201d,采用二相驅(qū)動(dòng)脈沖工作,驅(qū)動(dòng)電路要產(chǎn)生六路工作脈沖,其中五路用作ccd提供工作脈沖,分別為幀轉(zhuǎn)移脈沖sh、電荷轉(zhuǎn)移脈沖t1、t2、復(fù)位脈沖rs、補(bǔ)償脈沖bt;另一路為單元轉(zhuǎn)移脈沖sp。此六路脈沖由cpld中的driver部分產(chǎn)生,此部分可用硬件描述語言vhdl進(jìn)行設(shè)計(jì)。

產(chǎn)生補(bǔ)償脈沖bt和單元轉(zhuǎn)移脈沖sp時(shí),由于bt占空比為2:1,因此應(yīng)對(duì)輸入的時(shí)鐘脈沖三分頻,低電平占時(shí)鐘脈沖一個(gè)周期,高電平占時(shí)鐘脈沖兩個(gè)周期,其具體的程序部分如下:

process(clk)

begin

if(clk’event and clk=‘1’)then

counter1<=counter1+1;

if counter1=2 then

mbt<=‘0’;

counter1<=0;

else mbt<=‘1’;

end if;

end if;

bt<=mbt;

sp<=mbt and(not msh2);

end process;

該器件有2048位有效像元,工作時(shí)還要有46位啞像元輸出,一個(gè)掃描周期至少應(yīng)有2094個(gè)像元時(shí)鐘周期,由于該器件兩并行輸出,因此,一個(gè)幀轉(zhuǎn)移周期內(nèi)的t1、t2至少分別有1047個(gè)脈沖。由于t1、t2的周期相等,方向相反且周期為bt周期的二倍,因此,產(chǎn)生sh、t1、t2的程序進(jìn)程如下:

process(mbt,clk)

begin

if (mbtevent and mbt=‘1’)then

mt<=not mt;

end if;

if(clk’event and clk=‘1’)then

t1<=mt and (not msh2);

t2<=(not mt)or msh2;

end if;

end process;

process(mt)

begin

if(mt’event and mt=‘1’)

then

counter2<=counter2+1;

if counter2=1100 then

counter2<=0;

msh1<=‘1’;

msh2<=‘1’;

elsif(counter2<=3)then

msh1<=‘1’;

msh2<=‘1’;

elsif(counter2>3 and counter2<=5)then

msh1<=‘0’;

msh2<=‘1’;

else

msh1<=‘0’;

msh2<=‘0’;

end if;

end if;

sh<=msh1;

end process;

產(chǎn)生rs的程序進(jìn)程如下:

process(mbt,clk)

begin

if(clk’event and clk=‘0’)then

rs<=not mbt;

ned if;

end process;

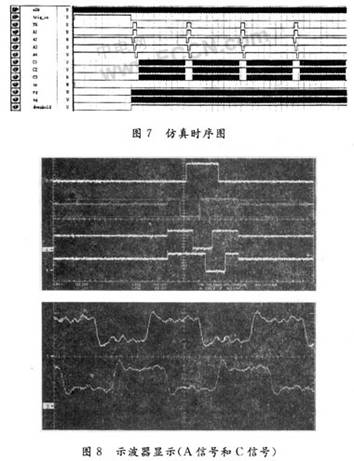

至此,這樣ccd驅(qū)動(dòng)電路的六路信號(hào)均產(chǎn)生完畢,可以進(jìn)行仿真,其結(jié)果如圖3所示。

由圖3可看出,所產(chǎn)生的驅(qū)動(dòng)信號(hào)滿足tcd1201d所需驅(qū)動(dòng)時(shí)序關(guān)系。

dispart模塊是用來對(duì)外部時(shí)鐘進(jìn)行分頻的,可應(yīng)用vhdl語言描述。其中二、三分頻的程序如下:

process(clk)

begin

if(clk’event and clk=‘1’)then

mf1<=not mf1;

end if;

f1<=mf1;

end process;

process(clk)

begin

if(clk’event and clk=‘1’)

then

counter2<=counter2+1;

if counter2=2 then

mf2<=‘1’;

counter2<=0;

else

mf2<=‘0’;

end if;

end if;

f2<=mf2;

end process;

其他分頻數(shù)與之類似,這里不再贅述。

compare模塊是用來對(duì)a/d的轉(zhuǎn)換結(jié)果進(jìn)行寄存,并在一幀結(jié)束后,對(duì)得到的電壓峰值進(jìn)行判斷以確定其是否在所規(guī)定的閾值范圍內(nèi),從而控制多選一模塊multiplexer。應(yīng)用vhdl語言描述時(shí),其程序的主要部分如下:

process(clk)

begin

if(clk’event and clk=‘0’)then

if data>reg_data then

reg_data<=data;

end if;

end if;

end process

process(sh)

begin

if(sh’event and sh=‘1’)

then

if(reg_data>200)then

if(reg_q(2)or reg_q(1)or reg_q(0)=‘1’ then

reg_q<=reg_q-1;

end if;

elsif(reg_data<150)then

if(reg_q(2)and reg_q(1)

and reg_q(0)=‘0’ then

reg_q<=reg_q+1;

end if;

else reg_q<=reg_q;

end if;

end if;

q<=reg_q;

end process;

這里,第一個(gè)進(jìn)程的作用是得到ccd輸出電壓的峰值,data為a/d轉(zhuǎn)換的結(jié)果。第二個(gè)進(jìn)程的作用是判斷峰值是否在閾值范圍內(nèi),以調(diào)整輸出q,去控制多選一模塊選擇相應(yīng)的時(shí)鐘脈沖來作為driver的輸入。

將設(shè)計(jì)好的各個(gè)模塊應(yīng)用原理圖進(jìn)行連接,然后進(jìn)行器件選擇,本設(shè)計(jì)選cpld芯片為epm7128slc84-15,然后編譯,再進(jìn)行仿真,即可所得,如圖4所示的時(shí)序圖。

觀察該時(shí)序圖中可以看到,如cpld的工作與最初的設(shè)計(jì)意圖相符,即可將程序下載到epm7128slc-15芯片中。

實(shí)驗(yàn)結(jié)果

進(jìn)行電路的原理圖設(shè)計(jì),制成電路板,與ccd傳感器連接。將光束打在一反射物體上,反射光為ccd傳感器所接受,然后調(diào)節(jié)光照強(qiáng)度,利用示波器觀察sh,可以看到sh的頻率隨光強(qiáng)的增大而增大。

結(jié)束語

本文所設(shè)計(jì)的帶的ccd驅(qū)動(dòng)電路,可集成于一片cpld芯片中,較過去的由幾十片芯片組成的驅(qū)動(dòng)電路,其面積大大減小了,而且?guī)в凶詣?dòng)增益調(diào)整功能,對(duì)頻率的選出采用逐次逼近的方式。因此,采用適當(dāng)?shù)牟介L,就可以將sh的變化控制在比較合適的范圍內(nèi),從而使峰值的收斂達(dá)到較好的效果。此外,自動(dòng)增益調(diào)整也避免了人工調(diào)整的麻煩和誤差,提高了精度,降低了勞動(dòng)強(qiáng)度。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論