1 引言

數控振蕩器是數字通信中調制解調單元必不可少的部分,同時也是各種數字頻率合成器和數字信號發生器的核心。隨著數字通信技術的發展。對傳送數據的精度和速率要求越來越高。如何得到可數控的高精度的高頻載波信號是實現高速數字通信系統必須解決的問題。可編程邏輯器件和大容量存儲器的發展為這一問題的解決帶來了曙光。本文介紹如何用FPGA(現場可編程邏輯門陣列)和SRAM(靜態隨機存儲器)實現高精度數控振蕩器。

2 NCO概述

NCO(Numerical Controlled Oscillator)即數控振蕩器用于產生可控的正弦波或余弦波。其實現的方法目前主要有計算法和查表法等。計算法以軟件編程的方式通過實時計算產生正弦波樣本.該方法耗時多且只能產生頻率相對較低的正弦波.而需要產生高速的正交信號時,用此方法無法實現。因此,在實際應用中一般采用最有效、最簡單的查表法,即事先根據各個NCO正弦波相位計算好相位的正弦值。并以相位角度作為地址把該相位的正弦值數據存儲在表中,然后通過相位累加產生地址信息讀取當前時刻的相位值在表中對應的正弦值,從而產生所需頻率的正弦波。

用查表法實現NCO的性能指標取決于查表的深度和寬度,即取決于表示相位數據的位數(查表存儲器地址線的位數)和表示正弦值數據的位數(查表存儲器數據線的位數)。改善NCO性能最簡單和最根本的方法是加大查找表的深度和寬度。目前,用查找表法實現NCO的普遍做法是用片內ROM作為查找表,由于片內資源的限制,查找表的深度和寬度一般不會很大(通常為256x8 bits),大大限制了NCO性能的提高。用獨立的大容量SRAM作為查找表,把查找表從片內移到片外,可以較好解決這個問題。基于這種思想,筆者成功地用FPGA(Xilinx公司的XC2V1000型門陣列)和SRAM(Cypress公司的CY7C1021型存儲器)實現了NCO。

3 NCo的實現

3.1 結構設計

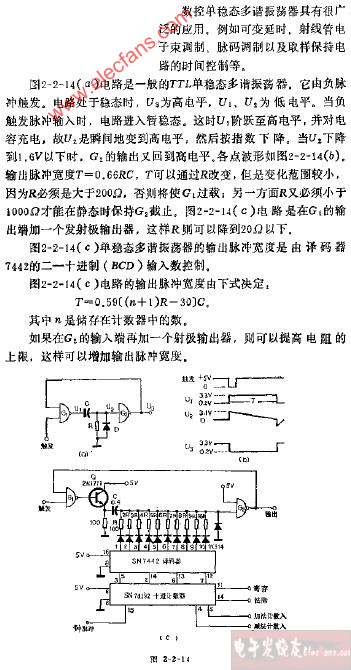

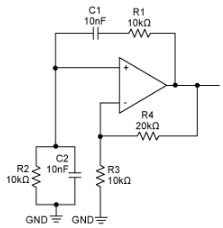

用FPGA和SRAM實現的NCO的結構如圖1所示。大框內部分是由FPGA完成.主要部件分為頻率控制字寄存器、相位控制字寄存器、通道控制字寄存器、累加器、加法器、通道選擇器和鎖存器等。微處理器對NC()進行控制,可用單片機或DSt,(數字信號處理器)實現。

3.1.1 頻率控制字寄存器、相位控制字寄存器、累加器和加法器

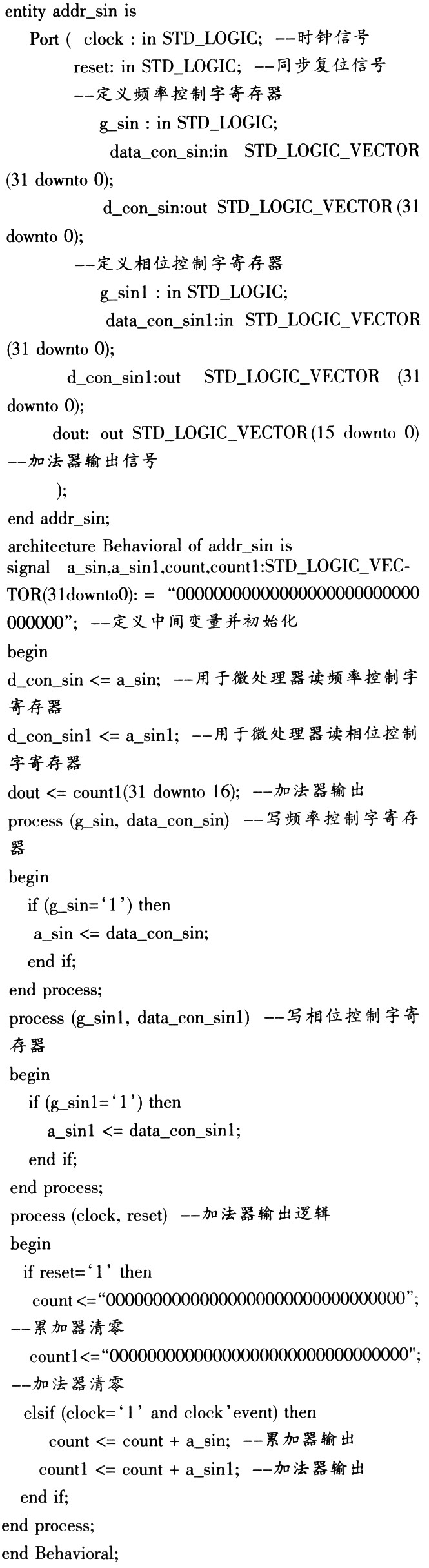

頻率控制字寄存器和相位控制字寄存器都是32位并行輸入,并行輸出寄存器,它們通過微處理器接口進行讀寫。頻率控制字寄存器確定載波的頻率.相位控制字寄存器確定載波的初始相位。32位累加器對代表頻率的頻率控制字進行累加運算,累加結果與代表初始相位的相位控制字通過32位加法器進行相加運算.相加結果的高16位數據讀取查找表的地址信息。頻率控制字寄存器、相位控制字寄存器、累加器和加法器可以用VHD[.語言描述,集成在一個模塊中,其VHDL源程序如下:

3.1.2通道控制字寄存器和通道選擇器

通道控制字寄存器和頻率控制字寄存器與相位控制字寄存器的結構完全一樣.都是32位并行輸入/并行輸出寄存器,通過微處理器接口進行讀寫。通道控制字寄存器僅用最后一位對通道選擇器進行控制。通道選擇器是二選一復用器.當Sel控制端為O時選擇通道l,當Sel控制端為1時選擇通道2。通道選擇器作為SRAM與FPGA的接口.每個通道不僅包括16條地址線,而且還有3條控制線和32條數據線。在圖l中,為了使NCO的結構更加清晰,通道選擇器的控制線和數據線沒有表示出來。

3.1.3 SRAM和鎖存器

SRAM是64Kx32的高性能靜態RAM.由2個CY7C102l(64KXl6)并聯構成,用作查找表。SRAM通過微處理器進行配置,直接存放2路、1個周期、65 536個16位載波樣本(高16位存放正弦波,低16位存放余弦波)。雖然SRAM是異步器件,但由于工作速度極高,在簡單控制邏輯配合下完全可以工作在同步模式下。NCO工作時.控制邏輯(用VHDL語言描述)通過通道l使SRAM的控制信號線處于讀有效電平,用相位地址直接驅動SRAM.從SRAM讀出的數據進入32位鎖存器.分2路直接輸出.不需要任何地址和數據轉換邏輯。用于鎖存器的時鐘和用于累加器、加法器的時鐘在相位上相差180°,這是由SRAM的開關特性決定的。

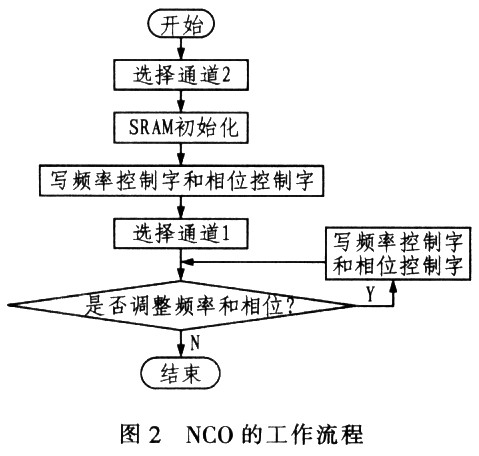

3.2 NCO的工作過程

NCO工作前必須對SRAM進行初始化.圖2示出NCO的工作流程。首先,微處理器向通道控制字寄存器寫入1,使通道選擇器選擇微處理器接口。然后.微處理器對SRAM進行配置.向SRAM中寫入載波樣本.接著,微處理器向頻率控制字寄存器和相位控制字寄存器寫入頻率控制字和相位控制字,確定載波的頻率和初始相位.最后,向通道控制字寄存器寫入0.通道選擇器選擇通道l,使NCO處于工作狀態。此時微處理器可以對頻率控制字寄存器和相位控制字寄存器進行動態讀寫,實現對NCO的動態實時控制.完成NCO頻率與初始相位的調整。

? ?

?

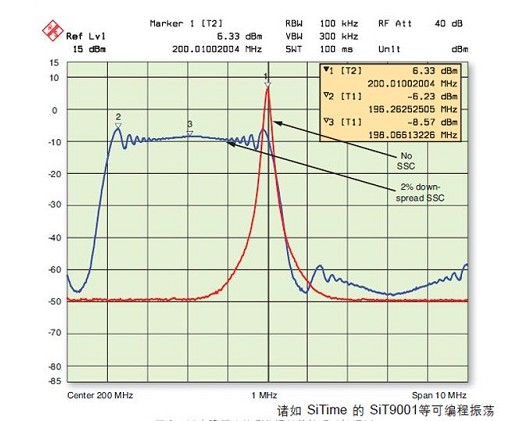

3.3 NCO性能評估

按照上述結構.筆者設計了一種NCO系統。該系統的工作時鐘為80MHz.用DSP作為微處理器。通過系統測試.該NCO的性能指標達到了設計要求,頻率分辨率△f=O.0186Hz,信噪比(SNR)在100dB以上.圖3示出NCO的典型特性曲線。

4 結構特點

用FPGA和SRAM實現數控振蕩器有許多特點。

首先,查找表的容量可以進一步加大。此設計的結構把相位累加部分和查找表分開單獨實現.由于FPGA具有可重復編程性且有豐富的I/O資源,因此只要稍加改動FPGA內的邏輯設計就可以外掛更大容量的SRAM。

其次,載波樣本的數據位數可以靈活控制。在查找表容量一定的情況下,可以根據具體應用調整載波樣本的數據寬度。實現的手段有二:一是在對SRAM配置時通過微處理器以軟件編程的方式直接調整SRAM的數據寬度:二是在FPGA內對SRAM輸出數據的位數進行截位處理.可通過調整FPGA中鎖存器的輸出實現。

第三,能夠靈活應用到其他領域中。該NCO只消耗FPGA中6%的Slices資源,大量資源包括片內RAM和硬件乘法器都沒有用到,利用這些資源可以對NCO進行功能擴展,實現數字下變頻器(Digital Down Converter-DDC)、數字頻率合成器(Direct Digital Synthesizer-DDS)和調制解調器等。

5 結束語

本文介紹了一種新的NCO實現方法,用該方法設計的NCO可實現對載波的頻率、相位和幅度的完全控制。由于用獨立的大容量SRAM作為查找表,使得NCO有較高的精度。同時該NCO有很大的發揮空間,能夠靈活地運用到其他領域。

電子發燒友App

電子發燒友App

評論