?? 在信息信號處理過程中,如對信號的過濾、檢測、預測等,都要使用到濾波器,數字濾波器是數字信號處理中使用最廣泛的一種方法,常用的數字濾波器有無限長單位脈沖響應(IIR)濾波器和有限長單位脈沖響應(FIR)濾波器兩種[1]。對于應用設計者,由于開發速度和效率的要求很高,短期內不可能全面了解數字濾波器相關的優化技術,需要花費很大的精力才能使設計出的濾波器在速度、資源利用、性能上趨于較優。而采用調試好的IP核需要向Altera公司購買。本文采用了一種基于DSP Builder的FPGA設計方法,以一個低通的16階FIR濾波器的實現為例,通過生成的濾波器頂層模塊文件與A/D模塊文件設計,在聯星科技的NC-EDA-2000C實驗箱上驗證了利用該方法設計的數字濾波器電路工作正確可靠,能滿足設計要求。

1 FIR濾波器的參數設計

1.1 設計要求

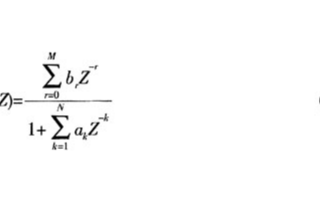

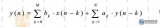

???? 數字濾波器實際上是一個采用有限精度算法實現的線性非時變離散系統,它的設計步驟為先根據需要確定其性能指標,設計一個系統函數H(z)逼近所需要的技術指標,最后采用有限精度算法實現。本系統的設計指標為:設計一個16階的低通FIR濾波器,對模擬信號的采樣頻率Fs為48KHz,要求信號的截止頻率Fc=10.8kHz,輸入序列為寬為9位(最寬位為符號位)。

?1.2 FIR濾波器的參數選取

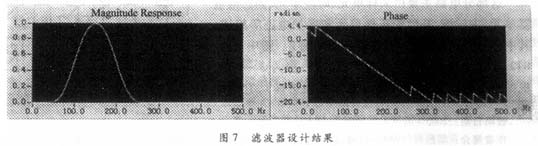

??? 設計頻率選擇性數字濾波器時,通常希望能有近似恒定的頻響幅度,并盡量減小通帶內的相位失真,斜率為整數的線性相位對應于時域中簡單的延時,他在頻域中可將相位失真降低到最小的程度[2],用Matlab提供的濾波器設計的專門工具箱--FDAtool仿真設計濾波器,滿足要求的FIR濾波器幅頻特性,如圖1所示。

?

2 數字濾波器的DSP Builder設計

2.1 DSP Builder介紹

?? DSP Builer是Altera推出的一個數字信號處理(DSP)開發工具,他在Quartus II FPGA設計環境中集成了Mathworks的Matlab和Simulink DSP開發軟件[3]。對DSP Builder而言,包括DSP系統的建模,系統級仿真、設計模型向VHDL硬件描述語言代碼的轉換、RTL(Register Transfer Level,邏輯綜合)級功能仿真測試、編譯適配和布局布線、時序實時仿真直至對DSP目標器件的編程配置,整個開發流程幾乎可以在頂層的開發工具Matlab/Simulink同一環境中完成。

2.2 FIR 濾波器算法模型建立

??? 根據FIR濾波器原理,可以利用FPGA來實現FIR濾波電路,DSP Builder設計流程的第一步是在Matlab/Simulink中進行設計輸入,即Matlab的Simulink環境中建立一個MDL模型文件,用圖形方式調用Altera DSP Builder和其他的Simulink庫中的圖形模塊,構成系統級或算法級設計框圖(或稱Simulink建模)。

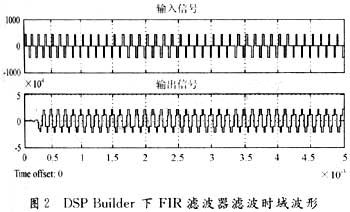

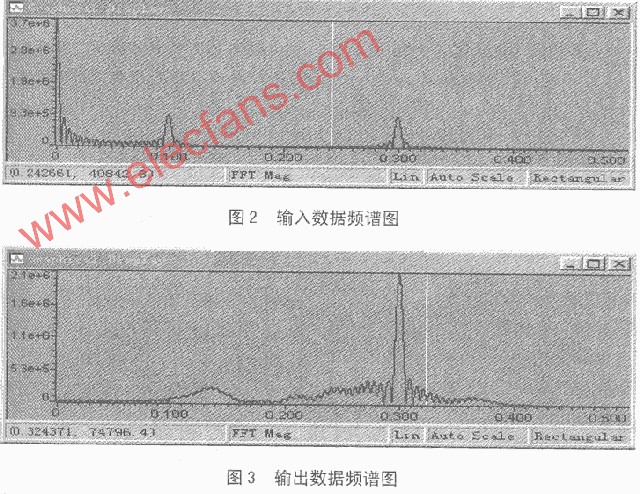

2.3 基于DSP Builder的系統級仿真

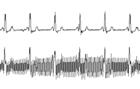

??? 輸入信號采用頻率分別為f1=8KHz和f2=16KHz的兩個正弦信號進行疊加,其中的仿真波形如圖2所示,從FIR濾波電路的仿真結果看出,輸入信號通過濾波器后輸出基本上變成單頻率的正弦信號,至此完成了模型仿真。

3 基于 FPGA的數字濾波器的實現

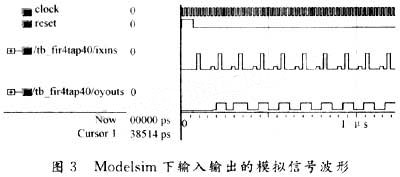

3.1 運用Modelsim進行功能仿真

?????? 在DSP Builder中進行的仿真是屬于系統驗證性質的,是對MDL文件進行的仿真,并沒有對生成的VHDL代碼進行過仿真。事實上,生成VHDL描述是RTL級的,是針對具體的硬件結構的,這兩者之間有可能存在軟件理解上的差異,轉換后的VHDL代碼實現可能與MDL模型描述的情況不完全相符,這就需要針對生成的RTL級VHDL代碼進行功能仿真。

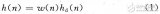

??? 我們利用Modelsim來對生成的VHDL代碼進行功能仿真。設置輸入輸出信號均為模擬形式,出現如圖3所示的仿真波形,可以看到這與Simulink里的仿真結果基本一致。即可在Quartus II環境下的硬件設計[4]。

?

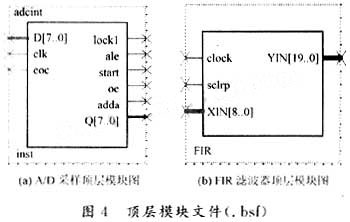

3.2 在FPGA器件中實現FIR濾波器

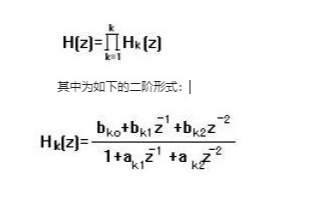

?? 用FPGA實現的數字濾波器處理的是數字信號,在實際應用中,首先就要用A/D轉化器對模擬信號進行采樣與量化。傳統的方法多數是用CPU或單片機完成的,缺點是控制周期長,速度慢。而利用同步時序狀態機來控制A/D采樣是一種既簡單可靠,又能顯著提高采樣周期的行之有效的方法。

?? 在Quartus II環境通過VHDL語言按要求設計該狀態機并轉換為.bsf文件;打開DSP Builder建立的Quartus II項目文件fir.qpf及fir.vhd并轉換為相應的.bsf文件,由此可以得到對應設計的模塊,如圖4所示,調用這兩個模塊建立新的頂層原理圖文件,在軟件環境里通過時序仿真,指定器件管腳、進行編譯、最后下載到實驗箱的EP1K10TC100-3器件中。

4 結語

?? 用信號發生器產生所要求的兩個不同頻率的正弦信號,就可以示波器上看到濾波以后的結果,需要設計不同的濾波電路時,僅修改濾波器模型文件就可以實現。可見在利用FPGA進行數字濾波器的開發時,采用DSP Builder作為設計工具能快捷、可靠地設計實用濾波系統。

電子發燒友App

電子發燒友App

評論