? 摘要:溫度的監(jiān)測與控制,對于工業(yè)生產(chǎn)的發(fā)展有著非常重要的意義。分析并設(shè)計了基于數(shù)字化一線總線技術(shù)的智能溫度測控系統(tǒng)。本系統(tǒng)采用FPGA實現(xiàn)一個溫度采集控制器,用于傳感器和上位機的連接,并采用微軟公司的Visual C++作為開發(fā)平臺,運用MSCOMM控件進行串口通信,進行命令的發(fā)送和接收。

關(guān)鍵字:一線總線;異步通訊;FPGA;MSCOMM

1引言

?? 目前基于智能溫度傳感器DS18B20的測溫設(shè)計大多是單片機程序。本課題嘗試使用FPGA芯片進行設(shè)計。FPGA內(nèi)部有豐富的觸發(fā)器和I/O引腳,同時具有靜態(tài)可重復(fù)編程和動態(tài)在系統(tǒng)重構(gòu)的特性,極大地提高了設(shè)計的靈活性和通用性,更適用于電子系統(tǒng)的開發(fā)。如果用戶需求量非常大,采用ASIC流片能極大地節(jié)省成本,經(jīng)濟效益十分顯著。FPGA可做其它全定制或半定制ASIC電路的中試樣片。鑒于此,本課題使用硬件描述語言設(shè)計FPGA控制器來實現(xiàn)傳感器控制,同時用VC來實現(xiàn)用戶控制界面。

?? 一線總線(l-wire)傳感器的出現(xiàn)(如DS18B20),使得在倉庫、工廠、樓宇等需要實時測溫的網(wǎng)絡(luò)布線得以大大改善。在大體積混凝土的建造過程中,為了防止混凝土的開裂而造成工程的失敗,需要對若干點的溫度進行實時監(jiān)控。由于施工現(xiàn)場的限制,使得可利用的布線區(qū)域越簡單越好。與此同時,現(xiàn)場溫度的采集與控制也有一定的要求。這時就可以在需要的測溫點橫向或縱向構(gòu)成多層網(wǎng)絡(luò),而各個一線總線傳感器直接掛接在上面即可。而對于每層的溫度采集和控制則可以由“FPGA控制器”去實現(xiàn),使用和拆卸都很方便。并且由于FPGA移植性好、升級方便,對于各企業(yè)的成本也可以大大降低。隨著FPGA的進一步發(fā)展,此溫度采集控制器的應(yīng)用范圍將不斷擴大,所體現(xiàn)的價值也將越來越高。

?? 現(xiàn)場可編程門陣列(Field Programmable Gate Array,F(xiàn)PGA)是當(dāng)今應(yīng)用最廣泛的一類可編程專用集成電路(ASIC)。FPGA作為專用集成電路(ASIC)領(lǐng)域中的一種半定制電路而出現(xiàn)的,既解決了定制電路的不足,又克服了原有可編程器件門電路數(shù)有限的缺點。電子設(shè)計工程師利用它可以在辦公室或?qū)嶒炇依镌O(shè)計出所需的專用集成電路,從而大大縮短了產(chǎn)品上市時間,降低了開發(fā)成本。此外,可編程邏輯器件還具有靜態(tài)可重復(fù)編程和動態(tài)在系統(tǒng)重構(gòu)的特性。這使得硬件的功能可以像軟件一樣通過編程來修改,極大地提高了電子系統(tǒng)設(shè)計的靈活性和通用性。

2智能溫度采集器的設(shè)計

?? 在FPGA的設(shè)計中一般有兩種方法:自上而下和自下而上。任何復(fù)雜的數(shù)字系統(tǒng),都可以按層次細(xì)分,一直分到對每個部分都有比較明確而簡單的設(shè)計方案為止。這就是常常說的分而治之的方法。自上而下的方法之所以重要,就在于只有在上面的層次上才能全面確定下面模塊的輸入輸出和功能行為的規(guī)格。而自下而上有時也行得通的原因是有些模塊的規(guī)格本身是就是事先確定的或者基本可以確定的。

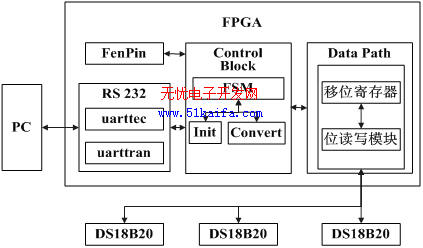

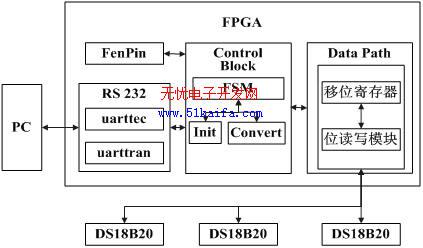

?? 針對溫度采集控制器系統(tǒng)的特點,決定采用自上而下的設(shè)計方法,并將整個系統(tǒng)分為Control Unit和Data Path來進行設(shè)計(圖1)。這樣實現(xiàn)有以下優(yōu)點:(1)Control Unit在內(nèi)部FSM的控制下,在每一個State會有Outputs,控制Data Path中數(shù)據(jù)的傳輸,滿足DS18B20的時序要求;(2)Data Path則完成了所有的數(shù)據(jù)流傳輸,并實時的反饋給Control Unit一些Inputs,從而使其State轉(zhuǎn)換能夠正確完成;(3)如果要有附加的控制流和數(shù)據(jù)流要添加進整個FPGA系統(tǒng),則只要在Control Unit中更改相應(yīng)的State和Data Path中做相應(yīng)修改就可。這樣設(shè)計出來的系統(tǒng)穩(wěn)定、擴展性好。

圖1、智能溫度采集器的系統(tǒng)結(jié)構(gòu)框圖

?? 在設(shè)計Control Block的時候一般采取有限狀態(tài)機(FSM)的方法。FSM分兩大類:米里型(Inputs對輸出邏輯和下一狀態(tài)邏輯有影響)和摩爾型(Inputs只對下一狀態(tài)邏輯有影響)。FSM設(shè)計中首要的是確定狀態(tài)變量。這是以對設(shè)計問題的深入了解為基礎(chǔ)的。每一個狀態(tài)都有可以實現(xiàn)的進入條件,每個狀態(tài)在所有輸入條件下都有明確的下一狀態(tài),包括下一狀態(tài)和目前狀態(tài)相同的狀態(tài)的情況。顯然,如果下一狀態(tài)只有和目前狀態(tài)相同的狀態(tài)才是可實現(xiàn)的,那么FSM一旦進入這個狀態(tài)就不會再改變了,這種“死機”狀態(tài)當(dāng)然是要避免的。在此系統(tǒng)的 Control Block中的FSM采用摩爾型,設(shè)計出“下一狀態(tài)邏輯”從而使得“狀態(tài)寄存器”能在每一個時鐘沿正確的進行狀態(tài)轉(zhuǎn)換,并確定好“輸出邏輯”,在每一個狀態(tài)都能輸出正確的控制流來對 Data Path中的數(shù)據(jù)流進行正確的控制,保證整個系統(tǒng)能夠正確的工作。

?? 數(shù)據(jù)通道實現(xiàn)的是數(shù)據(jù)間的運算和傳輸。數(shù)據(jù)可能是8/16/32/64位的,一般所有位的運算并沒有太大的不同。但是,它又要同時實現(xiàn)Control Block中的FSM的功能,其設(shè)計是要和 Control Block中的FSM的結(jié)構(gòu)一起考慮的。一旦FSM確定了,數(shù)據(jù)通道的計劃就要著手進行。由于數(shù)據(jù)通道的性能決定了整個系統(tǒng)的性能的高低,所以它又非常的關(guān)鍵。以往通用處理器因為生產(chǎn)數(shù)量大,數(shù)據(jù)通道用全定制的方法設(shè)計比較多,線路和版圖設(shè)計的精雕細(xì)刻,以求換得低的芯片生產(chǎn)成本和用其他方法難以達(dá)到的性能水平。這種情況在現(xiàn)代的SOC產(chǎn)品里有了很大的改變,因為SOC產(chǎn)品的產(chǎn)量一般都比較小,而且設(shè)計者都希望同一個處理器核的設(shè)計能夠用于不同工藝生產(chǎn)的產(chǎn)品。這樣,全定制的設(shè)計就不合適了。一般來說,數(shù)據(jù)通道是一定形式的流水線,因為數(shù)據(jù)的讀取、運算和結(jié)果的寫入都在同一個周期內(nèi)實現(xiàn),時鐘頻率就很難提高,所以高性能處理器的數(shù)據(jù)通道現(xiàn)在都采用流水線設(shè)計。數(shù)據(jù)通道和數(shù)據(jù)寄存器和數(shù)據(jù)存儲器的關(guān)系十分密切,這當(dāng)然是由處理器的結(jié)構(gòu)確定的。在此系統(tǒng)中的 Data Path的數(shù)據(jù)流處理功能并不是非常的復(fù)雜,可以不用采取流水線設(shè)計,并在FSM的控制下進行正確的數(shù)據(jù)流傳輸,同時會反饋給FSM中的“下一狀態(tài)邏輯”一些Inputs信號來使其能夠進行正確的狀態(tài)轉(zhuǎn)換。

3智能溫度采集器的實現(xiàn)

??? 系統(tǒng)開發(fā)環(huán)境。本課題硬件設(shè)計采用XILINX公司SPARTAN-3器件開發(fā)板進行編程驗證,其特性如下:(1)具有二十萬門,十二個嵌入式18x18乘法器支持高性能DSP應(yīng)用,216 Kbit的塊RAM,50 MHZ內(nèi)部時鐘晶振;(2)板上2Mbit Platform Flash;(3)八個開關(guān),四個按鈕,八個LED,四個七段顯示;(4)串口,VGA口,PS/兩個鼠標(biāo)/一個鍵盤口;(5)三組各40個引腳的擴展連接;(6)三個強電流的電壓整流器(3.3V,2.5V,1.2V);(7)配合JTAG3編程線和Xilinx的P4&MultiPRO線。系統(tǒng)硬件設(shè)計采用Verilog HDL設(shè)計語言,設(shè)計流程在Xilinx公司提供的開發(fā)工具ISE中完成,配合MODELSIM SE仿真工具。SPARTAN-3開發(fā)板上使用MAX3222電平轉(zhuǎn)換器,轉(zhuǎn)換RS-232C的EIA電平+12V與TTL電平+3.3V。在本系統(tǒng)中,由于串口通訊的雙方都是自訂制的,因此本課題中的RS-232C的串行傳輸波特率選擇使用了PC機所能達(dá)到的最快傳輸速度:115200 bit/s。上位機軟件編程采用VC++ 6.0。

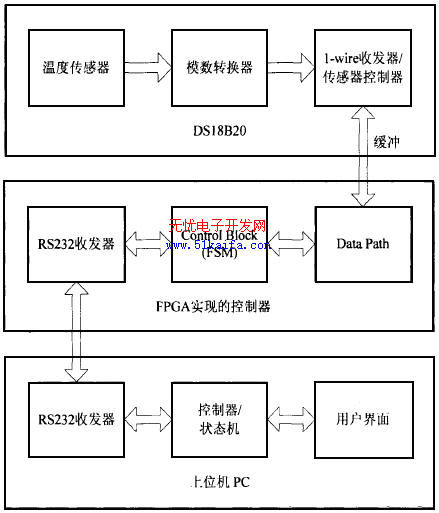

??? 控制器邏輯功能流程圖。首先設(shè)計各個硬件模塊,其中主控模塊狀態(tài)機先只實現(xiàn)一些基本功能指令的流程控制,仿真測試單獨的模塊。然后連接各個模塊組成完整的硬件電路并進行一些基本功能指令的測試。再利用串口調(diào)試助手及示波器檢驗硬件電路對一線總線上單個DS18B20的初始化(INITAILIZATION)、發(fā)送匹配ROM命令(MATCH ROM)、發(fā)送溫度轉(zhuǎn)換命令(CONVERT T)、發(fā)送引腳讀取命令(READ SCRATCHPAD)、發(fā)送讀時隙脈沖(READ TIMESLOTS)的操作結(jié)果。串口調(diào)試結(jié)果正確后聯(lián)合上位機程序?qū)崿F(xiàn)最基本的“Read Temperature”功能。上位機調(diào)試結(jié)果正確后硬件電路繼續(xù)添加其他功能,調(diào)試“搜索ROM命令(SEARCH ROM)和讀取ROM ID命令”,在FSM中實現(xiàn)搜索算法將溫度采集擴展至一線總線上多個DS18B20。整個系統(tǒng)邏輯框圖可見圖2。

圖2、智能溫度控制器邏輯功能流程圖

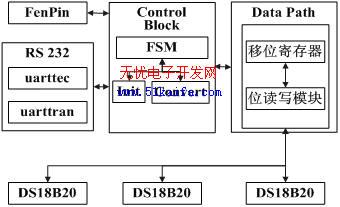

?? 控制器邏輯功能模塊。FPGA實現(xiàn)的控制器處于PC端上位機與溫度傳感器DS18B2O中間。FPGA的主要設(shè)計任務(wù)便是接收從串口得來的PC端上位機命令,通過內(nèi)部狀態(tài)機邏輯的判斷和控制,通過Data Path將命令傳達(dá)至溫度傳感器DS18B20,并將命令的執(zhí)行結(jié)果返回給上位機。FPGA主要實現(xiàn)1-wire收發(fā)器和RS232收發(fā)器,對兩邊起溝通作用。整個硬件模塊大致分成三層(圖3),第一層為RS232串行通信模塊和時鐘分頻模塊fenpin,第二層為主控模塊 Control Block,第三層為 Data Path部分:讀/寫模塊bytebit。

圖3、智能溫度控制器系統(tǒng)模塊層次結(jié)構(gòu)圖

l)RS232串行通信模塊。負(fù)責(zé)外部上位機串行bit與主控模塊Control Block并行byte間的數(shù)據(jù)傳輸。RS232串行通信速率采用 115200 bit/S。Uartrec從上位機接受一個字節(jié)com命令發(fā)給主控模塊Control Block,同時Uarttran從主控模塊Control Block接收一個字節(jié)result回應(yīng)發(fā)給上位機。

2)分頻模塊fenpin。由50 MHZ內(nèi)部晶振產(chǎn)生與DS18B20同步的1 MHZ時鐘。

3)主控模塊 Control Block。負(fù)責(zé)狀態(tài)轉(zhuǎn)化控制,實現(xiàn) Data Path和RS232收發(fā)器的溝通。通過內(nèi)部FSM邏輯的判斷和控制,將命令傳達(dá)至傳感器,并將命令的執(zhí)行結(jié)果返回給上位機。由兩個延時子模塊組成。初始化模塊init,負(fù)責(zé)初始化總線上所有DS18B20,并在初始化成功后報告主控模塊初始化狀態(tài)。若初始化失敗,將繼續(xù)初始化。若超過設(shè)定初始化時間仍不能成功初始化,將停止初始化并報警。溫度轉(zhuǎn)化等待模塊Convert,負(fù)責(zé)在讀/寫模塊bytebit向DS18B20發(fā)出convert命令后延時800 ms再報告主控模塊轉(zhuǎn)化完畢。根據(jù)DS18B20用戶手冊,溫度轉(zhuǎn)化最多用750 ms。所以采用800 ms的保守估算。

4)Data Path。由讀/寫模塊bytebit構(gòu)成,負(fù)責(zé)主控模塊Control Block和DS18B20之間的數(shù)據(jù)通信。由主控模塊Control Block的r_w信號決定是發(fā)WRITE TIME SLOTS還是發(fā)READ TIME SLOTS。

4結(jié)束語

本文作者的主要創(chuàng)新點:分析并設(shè)計了一個基于FPGA的智能溫度測控系統(tǒng)。本系統(tǒng)已經(jīng)廣泛地應(yīng)用到各種相關(guān)的實際系統(tǒng)。本項目已經(jīng)產(chǎn)生經(jīng)濟效益越230萬元。

電子發(fā)燒友App

電子發(fā)燒友App

評論