FPGA概述

現場可編程門陣列(FPGA)是一種可編程邏輯器件,由成千上萬個完全相同的可編程邏輯單元組成,周圍是輸入/輸出單元構成的外設。制造完成后,FPGA可以在工作現場編程,以便實現特定的設計功能。典型設計工作包括指定各單元的簡單邏輯功能,并選擇性地閉合互連矩陣中的一些開關。為確保正常工作,FPGA必須運用適當的電源管理技術。FPGA最初用于系統原型制作,最終量產時會用高速IC或ASIC代替。不過,近年來FPGA的性能有很大改善,成本則不斷下降,因此FPGA現已廣泛用于生產設計。

FPGA的功耗取決于許多不同因素,與設計密切相關。必須運用精確的功耗估算方法,才能確保電源系統符合FPGA要求。FPGA制造商會提供網絡工具,用于功耗計算。為了估算FPGA的功耗,計算程序需考慮設計資源運用、切換速率、工作時鐘頻率、I/O使用及其它許多因素。

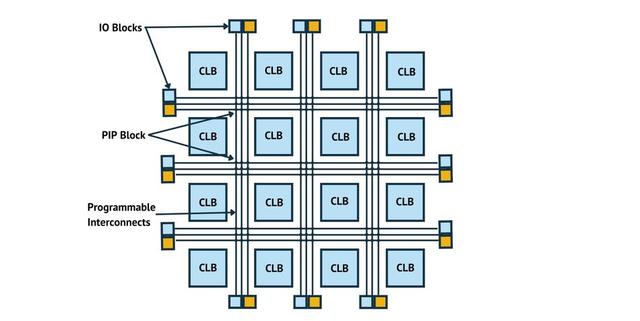

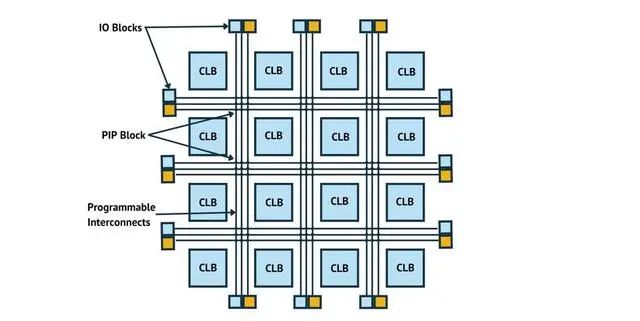

FPGA主要有三種可配置元件:可配置邏輯模塊(CLB)、I/O模塊(IOB)和互連。其中,CLB提供功能邏輯元件,IOB提供封裝引腳與內部信號線之間的接口,可編程互連資源提供路由路徑,將CLB和IOB的輸入和輸出與適合的網絡相連。CLB(或內核)上施加的電壓稱為VCCINT。VCCO是IOB的電源電壓。一些FPGA還有其它電壓輸入,稱為VCCAUX。VCCINT(用于CLB)的典型值為1.0V、1.2V、1.5V、1.8V、2.5V和3V,電流可達10A或更高。CLB數量越多,則電壓越低,電流越高。啟動時,VCCINT必須單調上升,不得下跌。最常用的VCCO電壓(用于IOB)為1.2V、1.5V、1.8V、2.5V、3.3V或傳統系統中的5V。電流范圍為1A至20A。輔助電壓(VCCAUX)典型值為3.3V或2.5V。它為FPGA中的時間關鍵資源供電,因此易受電源噪聲影響。VCCAUX可以與VCCO共用一個電源層,但前提是VCCO不會產生過大的噪聲。

FPGA使用的電源類型

FPGA電源要求輸出電壓范圍從1.2V到5V,輸出電流范圍從數十毫安到數安培。可用三種電源:低壓差(LDO)線性穩壓器、開關式DC-DC穩壓器和開關式電源模塊。最終選擇何種電源取決于系統、系統預算和上市時間要求。

如果電路板空間是首要考慮因素,低輸出噪聲十分重要,或者系統要求對輸入電壓變化和負載瞬變做出快速響應,則應使用LDO穩壓器。LDO功效比較低(因為是線性穩壓器),只能提供中低輸出電流。輸入電容通常可以降低LDO輸入端的電感和噪聲。LDO輸出端也需要電容,用來處理系統瞬變,并保持系統穩定性。也可以使用雙輸出LDO,同時為VCCINT和VCCO供電。

如果在設計中效率至關重要,并且系統要求高輸出電流,則開關式穩壓器占優勢。開關電源的功效比高于LDO,但其開關電路會增加輸出噪聲。與LDO不同,開關式穩壓器需利用電感來實現DC-DC轉換。

FPGA的特殊電源要求

為確保正確上電,內核電壓VCCINT的緩升時間必須在制造商規定的范圍內。對于一些FPGA,由于VCCINT會在晶體管閾值導通前停留更多時間,因此過長的緩升時間可能會導致啟動電流持續較長時間。如果電源向FPGA提供大電流,則較長的上電緩升時間會引起熱應力。ADI公司的DC-DC穩壓器提供可調軟啟動,緩升時間可以通過外部電容進行控制。緩升時間典型值在20ms至100ms范圍內。

許多FPGA沒有時序控制要求,因此VCCINT、VCCO和VCCAUX可以同時上電。如果這一點無法實現,上電電流可以稍高。時序要求依具體FPGA而異。對于一些FPGA,必須同時給VCCINT和VCCO供電。對于另一些FPGA,這些電源可按任何順序接通。多數情況下,先給VCCINT后給VCCO供電是一種較好的做法。

當VCCINT在0.6V至0.8V范圍內時,某些FPGA系列會產生上電涌入電流。在此期間,電源轉換器持續供電。這種應用中,因為器件需通過降低輸出電壓來限制電流,所以不推薦使用返送電流限制。但在限流電源解決方案中,一旦限流電源所供電的電路電流超過設定的額定電流,電源就會將該電流限制在額定值以下。

FPGA配電結構

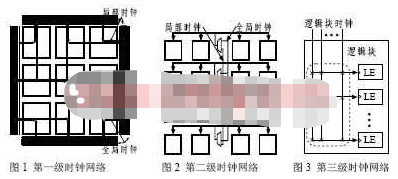

對于高速、高密度FPGA器件,保持良好的信號完整性對于實現可靠、可重復的設計十分關鍵。適當的電源旁路和去耦可以改善整體信號完整性。如果去耦不充分,邏輯轉換將會影響電源和地電壓,導致器件工作不正常。此外,采用分布式電源結構也是一種主要解決方案,給FPGA供電時可以將電源電壓偏移降至最低。

在傳統電源結構中,AC/DC或DC/DC轉換器位于一個地方,并提供多個輸出電壓,在整個系統內分配。這種設計稱為集中式電源結構(CPA),見圖1。以高電流分配低電壓時,銅線或PCB軌道會產生嚴重的電阻損耗,CPA就會發生問題。

CPA的替代方案是分布式電源結構(DPA),見圖2。采用DPA時,整個系統內僅分配一個半穩壓的DC電壓,各DC/DC轉換器(線性或開關式)與各負載相鄰。DPA中,DC/DC轉換器與負載(例如FPGA)之間的距離近得多,因而線路電阻和配線電感引起的電壓下降得以減小。這種為負載提供本地電源的方法稱為負載點(POL)。

圖1 集中式電源結構

圖2 分布式電源結構

當一個邏輯器件從邏輯1切換到邏輯0時,或者從邏輯0切換到邏輯1時,包括電源的輸出結構暫時變為低阻抗狀態。每次轉換均要求對信號線進行充電或放電,這就需要能量。旁路電容的功能是在本地儲存能量,以提供轉換所需的能量。

本地儲存能量必須在較寬的頻率范圍內可用。低串聯電感的非常小的電容用來為高頻轉換提供快速電流。高頻電容能量耗盡之后,較大、較慢的電容繼續提供電流。FPGA技術要求三種頻率范圍內的電容,即高、中、低頻率范圍。這些頻率的跨度為1kHz至500MHz。

正確放置對于高頻電容(1nF至100nF低電感陶瓷片式電容)非常重要;對于中頻電容(10μF至100μF鉭電容或陶瓷電容)和低頻電容(>470μF),這種重要性依次降低。之所以與放置有關,原因很簡單:從電容引腳到FPGA電源引腳的路徑電感必須盡可能低。這意味著該路徑必須盡可能短,哪怕要穿過實體接地層或電源層。1英寸實心銅層的電感約為1nH,因此距離極為重要。旁路電容過孔必須直接下行至接地層或VCC層。

高頻旁路電容,無論是在VCCINT還是VCCIO上,均應安裝在相關VCC引腳的1厘米范圍內;中頻旁路電容則應安裝在VCC引腳的3厘米范圍內。低頻旁路電容可以安裝在合理范圍內的電路板上任意位置。當然,離FPGA越近越好。

較新的FPGA有輸入/輸出旁路要求,因此以前用于低速或低密度設計的電容類型可能無效。根據所用材料、結構和值的不同,旁路電容在整個頻率范圍內有不同的串聯電抗。通過查看各種系列的數據手冊,可以得知某些電容更適合當前所考慮的應用。

圖3中顯示了電容阻抗隨頻率的變化曲線。阻抗最小值位于電容的自諧振頻率;超過此頻率后,寄生引線電感在“電容”的電抗特性中占據主導地位。圖中,業界標準型X7R單芯片、10nF陶瓷1206片式電容在50MHz時的阻抗為0.2Ω。然而,在500MHz時,該電容的阻抗約為3Ω。當有效阻抗增大,負載無法使用電容所儲存的能量時,電容即無效。同時還必須考慮溫度范圍和老化效應。一些電容在室溫時阻抗較低,但在極端溫度時則表現不佳。當電容值較大(100nF至330nF)時,Z5U電容在高頻時的ESR可能較低。不過,這種電容不宜在10℃以下使用。作為+20%、–80%額定器件,這種電容要求幾乎兩倍的設計值才能安全使用。選擇旁路電容系列時,最好查看電容制造商的數據手冊。

FPGA電源設計可能會涉及5A、10A甚至更高的電流在PCB走線中流動。當這種大電流存在并以開關模式(邊沿陡峭)隨時間變化時,顯而易見,噪聲、感應電壓和電磁輻射(EMI)很可能出現,并可能導致電源工作異常。與配線電感相關的快速開關電流也可能會產生電壓瞬變,并導致其它問題。為使電感和接地環路最小,傳導高電流的PCB走線應盡可能短。應采用接地層結構或單點接地,使外部元件盡可能靠近DC/DC轉換器,以實現最佳效果。使用開口鐵芯電感時,必須特別注意這種電感的位置和定位,避免電感通量與敏感的反饋接地路徑和COUT配線相交。使用具有可調輸出的開關穩壓器或控制器時,應將反饋電阻和相關配線置于IC附近,并遠離電感布置配線,尤其是開口鐵芯式電感。鐵氧體繞軸或鐵棒電感具有從繞軸一端經空氣到達另一端的磁力線。這些磁力線會在電感磁場范圍內的所有導線或PC板銅走線中產生感應電壓。銅走線中產生的電壓量由以下因素決定:磁場強度、PC銅走線相對于磁場的方向和位置,以及銅走線與電感之間的距離。

FPGA和穩壓器的可靠性取決于散熱問題。這些器件的溫度主要受待機功耗和總功耗、外部容性負載(僅FPGA)、熱阻、環境溫度以及氣流等因素控制。必須有效管理這些因素,使結溫(Tj)始終低于制造商規定的最高溫度。

ADP2114同步降壓開關穩壓器???ADP2114,pdf datasheet (Synchronous Step-Down DC-to-DC Regulator)

ADP2114(圖4)是一款功能多樣的同步降壓開關穩壓器,可滿足各種客戶負載點要求。兩個PWM通道既可以配置為分別提供2A和2A(或3A/1A)電流的兩路獨立輸出,也可以配置為提供4A電流的單路交錯式輸出。ADP2114可提供高功效,開關頻率最高可達2MHz。在輕負載時,該器件可以設置為脈沖跳躍模式工作,以便提高功效,或者設置為強制PWM模式工作,以便降低電磁干擾(EMI)。ADP2114還具有欠壓閉鎖(UVLO)、遲滯、軟啟動和電源正常輸出指示等特性;保護特性有輸出短路保護和熱關斷等。可以利用極小電阻和電容對輸出電壓、電流限制、開關頻率、脈沖跳躍工作模式和軟啟動時間進行外部編程。

圖3 電容阻抗隨頻率的變化曲線

圖4 ADP2114同步降壓開關穩壓器

該器件可用于多個終端市場,例如通信基礎設施、工業和儀器儀表、醫療保健以及高端消費電子市場。在這些終端市場的主要應用是分布式電源系統中的負載點穩壓器。

雖然DC-DC穩壓器的功效遠高于LDO,但通常認為其噪聲太高,無法在不顯著降低其它參數性能的情況下,直接為高性能模數轉換器供電。模數轉換器的噪聲至少有兩個來源:通過電源紋波直接耦合至轉換器中的噪聲,以及磁耦合效益引起的噪聲。

圖5所示為一種實驗室設置,針對采用低噪聲LDO供電和采用開關穩壓器ADP2114供電兩種情況,比較一個16位、125MSPS模數轉換器的性能。評估所用的AD9268可實現非常低的噪聲,信噪比(SNR)為78dB。DC-DC轉換器貢獻的額外噪聲或雜散成分很容易反映在該模數轉換器的輸出頻譜中,因此-152dBm/Hz的低本底噪聲使它非常適合評估開關電源。

圖5 開關電源供電測試

我們將ADP2114與低噪聲LDO穩壓器進行比較。高性能、16位、125MSPS AD轉換器AD9268的評估結果表明:采用開關穩壓器ADP2114供電與采用低噪聲LDO穩壓器供電相比,性能未受影響。

因此,ADP2114可以為用戶提供可配置能力、多樣化功能和靈活性,并且具有低噪聲特性和高轉換效率。同時能夠滿足各種客戶負載點電源要求,性價比高,是FPGA、ASIC、DSP和微處理器供電的理想選擇。ADI公司提供網絡工具可方便設計導入,同時提供評估板,有助于實現快速導入。

更多詳細內容,敬請登陸中電網在線座談網址:http://seminar.eccn.com

問答選編

問:印刷電路板中大電流供電,除加寬導電銅箔外,是否需要進一步采取鍍錫等措施?

答:加鍍錫一定程度上可以加大散熱面積,但是效果不一定特別明顯,最好還是加寬加厚導電銅箔。

問:在供電時,如果沒考慮上電順序,對整個系統的運行會有什么影響?

答:這個問題要針對系統的各個功能模塊對上電的要求,如果系統中的某些電路對上電有嚴格的順序,沒有考慮到的話,很可能導致系統不工作。

問:電源紋波對FPGA性能有何影響?

答:工作時期的電源紋波要求、供電系統的壓降、電源通路的等效阻抗設計等參數都是用戶要特別留意的。建議在做大設計的時候一定要做電源完整性仿真,且要嚴格滿足設計約束。

問:在IPTV系統中的FPGA供電電源有什么要求嗎?

答:IPTV系統中FPGA的電源需求比較復雜,多達三種供電要求:內核電壓、I/O電壓和輔助電壓。為了實現可靠的系統性,必須對這些排序,需要用電壓管理芯片。

問:I/O是否可以承受5V電壓?

答:這個取決于I/O的供電電壓。如果數字部分是5V供電,那么就可以。

問:ADP2118的輸出電感和電容如何選擇?它和負載電流、緩升時間有多大關系?

答:ADP2118為內部補償器件,因此對輸出電感電容有一定的限制,輸出電容一般不能小于47uF,輸出電感建議為0.8~3.3uH(針對頻率設置為1.4MHz)、1.5~3.3uH(針對頻率設置為700kHz)。輸出電感電容的選擇和負載電流、軟啟動時間并無太大關系。

問:ADP2114的PWM頻率是多大?都有什么封裝形式的?

答:有三種頻率可以選擇:300kH、600kHz、1.2MHz。封裝只有一種,即LFCSP,CP-32-2。

問:ADP2114強制PWM工作是如何降低EMI的?

答:ADP2114強制PWM工作時,將使芯片在整個負載范圍內始終工作在同一個恒定頻率,因此相比較PFM/PWM自動模式(開關頻率會在輕載時自動變化)來說,PWM工作能夠降低系統EMI以及系統噪聲。

問:FPGA電源的斜升時間(ramp-time)有哪些要求?

答:為確保供電,核心電壓VCCINT校正時間必須在一定范圍內。對于一些FPGA,過大的校正時間會產生更長時間的供電電流,由于在變壓器啟動treashold中VCCINT需要更長時間。開啟校正時間長會引起熱壓力,如果電源向FPGA提供大電流。一些DC/DC變壓器提供可調節軟啟動,允許通過一個外部電容器控制校正時間。校正時間取決于FPGA制造商,典型取值為50ms~100ms。

問:FPGA供電電源的電壓功耗如何估計?電源功耗取決于哪些因素?

答:可以根據公式:Pd=(Vin-Vout)(IL)+(VIn)(Iground),其中IL是負載電流,根據公式可以看出與輸入、輸出電壓、負載電流、對地電流有關。

問:電路如何設計才能得到低紋波、低EMI、低噪聲電源?

答:首先選擇的電源應該是低紋波、低噪聲的電源,其次就是布局布線要參考芯片資料給出的建議。

在線座談(Online Seminar)是中電網于2000年推出的創新服務,通過“視頻演示+專家解說+在線問答”三位一體相結合的形式,充分發揮網絡平臺的便捷性,實現了先進半導體技術提供商與系統設計工程師的實時互動交流,其形式和內容都廣受電子行業工程師的好評。本刊每期將挑選一些精華內容整理成文,以饗讀者

現場可編程門陣列的供電原理及應用

- 可編程門陣列(7736)

相關推薦

五大優勢凸顯 可編程邏輯或將呈現快速增長

可編程邏輯器件的兩種類型是現場可編程門陣列(FPGA)和復雜可編程邏輯器件(CPLD)。在這兩類可編程邏輯器件中,FPGA是在PAL、GAL、EPLD等可編程器件的基礎上進一步發展的產物。

2016-01-04 17:55:08 1404

1404

1404

1404如何使用可編程邏輯為按鈕輸入消抖:一個有效的消抖邏輯電路

可編程邏輯具有傳統分立 IC 無法提供的靈活性。 借助現成的開發工具,可輕松使用現場可編程門陣列和復雜可編程邏輯器件創建應用特定型功能。 按鈕開關輸入消抖便是此類功能的一個例子

2017-09-06 16:15:51 9262

9262

9262

9262

用于下一代汽車專用集成電路(ASIC)的嵌入式現場可編程邏輯門陣列(eFPGA)

用于下一代汽車專用集成電路(ASIC)的嵌入式現場可編程邏輯門陣列(eFPGA)

2020-07-24 11:26:52 1234

1234

1234

123410M04SCM153C8G現場可編程門陣列

`類別集成電路(IC)嵌入式 - FPGA(現場可編程門陣列)制造商Intel系列MAX? 10包裝托盤零件狀態在售電壓 - 供電2.85V ~ 3.465V安裝類型表面貼裝型工作溫度0°C

2021-04-28 15:40:58

10M40DAF484C8G現場可編程門陣列

`類別集成電路(IC)嵌入式 - FPGA(現場可編程門陣列)制造商Intel系列MAX? 10包裝托盤零件狀態在售電壓 - 供電1.15V ~ 1.25V安裝類型表面貼裝型工作溫度0°C ~ 85

2021-04-28 15:37:46

5AGXFA7H4F35I5G現場可編程門陣列

`類別集成電路(IC)嵌入式 - FPGA(現場可編程門陣列)制造商Intel系列Arria V GX包裝托盤零件狀態在售電壓 - 供電1.07V ~ 1.13V安裝類型表面貼裝型工作溫度-40°C

2021-04-28 15:32:26

可編程技術的引爆點

25年前,賽靈思(Xilinx)公司發明了FPGA(現場可編程門陣列)。如今,以FPGA為代表的可編程芯片應用已經成為勢不可擋的發展趨勢,尤其在ASSP和傳統ASIC之間出現的市場缺口上,FPGA將開辟出新的領域,而目前席卷全球的金融危機更是成為FPGA迅速發展的催化劑。

2019-07-25 08:05:19

可編程模擬的各種架構

是今天FPGA(現場可編程門陣列)流的混合信號版。可配置模擬IC已經出現了多年,表面看來對市場的影響不及其數字同胞FPGA(現場可編程門陣列)。不過,當前的經濟形勢卻使可編程模擬標準產品的概念突然顯現出

2019-07-05 07:51:19

可編程邏輯器件

完成乘法,實現3×4,只要通過寫程序讓3連續加4次就可以完成了。而可編程邏輯器件的兩種主要類型是現場可編程門陣列(FPGA)和復雜可編程邏輯器件(CPLD)。 在這兩類可編程邏輯器件中,FPGA提供了

2014-04-15 10:02:54

可編程邏輯器件和ASIC,兩者有什么不同區別?

ASIC。PLD的種類較多,目前廣泛使用的PLD器件主要是復雜可編程邏輯器件CPLD(Complex Programmable Logic Device)和現場可編程門陣列FPGA(Field

2021-07-13 08:00:00

現場可編程門陣列是...??

解答一些常見問題(FAQ)。問題1:什么是現場可編程門陣列??詳細解答如下:顧名思義,有人推斷它是可編程的邏輯門結構。這種解釋很接近,但又不太準確,因為內部邏輯陣列實際并不是利用門來實現的。相反,我們將

2019-08-08 09:13:00

電子發燒友App

電子發燒友App

評論