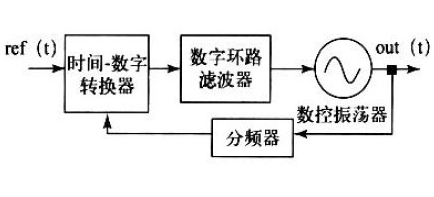

數控振蕩器(Numerically Controlled Oscillators,NCOs)是軟件無線電的重要組成部分和研究內容,它廣泛應用于DSP中,如通信領域的信號調制解調,蜂窩電話、基站、雷達系統、數字電視、GPS和無線LAN等。

NCOs可以通過各種方式實現:無限沖擊響應濾波器(IIR filters),坐標旋轉(CORDIC rotations),查找表技術(Lookup Tables,LUTs)。本文在Simulink軟件平臺仿真LUTs技術實現NCOs時,累加器步長、累加器控制字等參數對NCOs性能的影響。重點討論NCOs的頻譜純度問題,即如何抑制雜波分量,影響頻譜純度的因素以及如何提高無雜散動態范圍(SpuriousFree Dynamic Range,SFDR)。

1 NCOs的工作原理

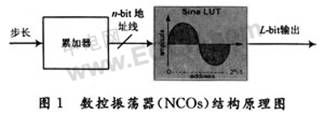

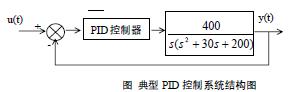

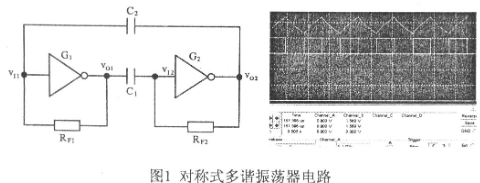

NCOs主要包括一個正弦波樣點查找表(LUTs)和一個產生地址的累加器,如圖1所示。

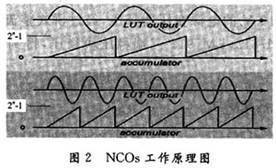

圖1中n為累加器產生的地址位數,則LUTs有N=2n個輸入。LUTs的輸出分辨率/精度為L位(該參數與n有關),其工作原理見圖2。

由圖2可以看出,累加器產生地址碼,循環從LUTs地址中取數正弦波的樣點數據,其取數的速率越快,即步長μ越大,則產生的正弦波頻率越高。

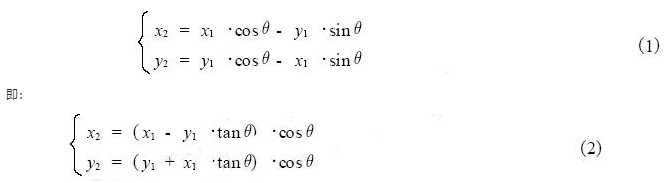

設步長參數μ由式(1)決定:

?

式中:N為LUTs的樣點數據總量;fs為系統采樣頻率;fd為期望的正弦波的頻率。

例如,累加器地址數據線寬度為8 b,則對應的LUTs的數據樣點數為N=2n=256。如果采樣頻率為10 MHz,期望頻率為2.5 MHz,則步長為:

2 提高NCOs的無雜散動態范圍

SFDR是無線系統設計中需要考慮的重要參數。如果振蕩器產生的信號包含過多的雜波(Spurs)頻率,這些干擾成分會使信號混頻的質量變差,特別是當雜波頻率接近中心頻率時,在后續的電路中很難去除。

2.1?相位截斷對頻譜純度的影響

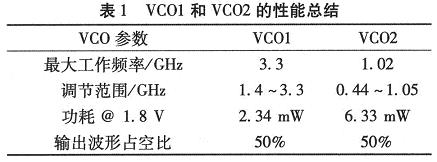

當LUT輸出正弦波樣點數據時,只有整數部分可以用于輸出,而小數部分則被忽略,這導致輸出相位部分有截斷。相位截斷(Phase Truncation)的情況決定了產生的正弦波的純度。如:當采樣頻率為100 kHz時,NCOs輸出的期望頻率為24.3 kHz,其NCOs設置參數見表1。從表1中可以看出,LUTs的分辨率為32 b,則可以忽略幅度值量化的影響,而雜波主要是由相位截斷產生的。?

?

2.2? 幅度值量化對頻譜純度的影響

將LUT的深度增大為12 b(4 096),則可以忽略相位舍去對頻譜純度的影響,而雜波主要由幅度值的量化(Amplitude Quantization)產生。同樣,當采樣頻率為100 kHz時,NCOs輸出的期望頻率24.3 kHz,NCOs設置參數見表2。

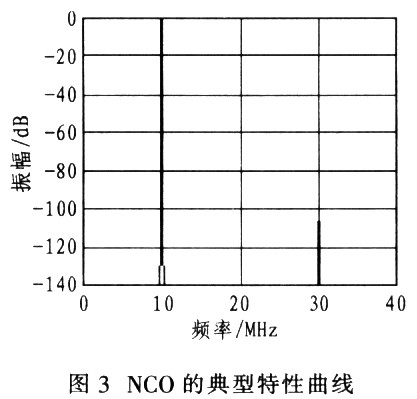

由圖3,圖4可以看出,相位截斷產生的雜波遠大于幅度值量化產生的雜波,是雜波的主要來源。

由以上的仿真波形可以看出,提高整數位的位數,雖然可以使相位截斷小,頻率雜波少,但要使用較大的LUTs容量。如整數位增加一位,即由n位增加n+1位,則LUTs的數據量會增加一倍。

提高小數位的位數可以有較高的步長精度和頻率分辨率,但需要更加多的累加器。如小數部分由b位增加到b+1位,雖然對LUTs無影響,但將累加器的加法器和延遲器分別增加1位,從而影響NCOs的輸出頻率。

提高LUTs輸出分辨率對正弦波樣點的幅度值量化影響小,但需要更多的LUTs存儲器。如LUTs輸出分辨率增加1位,由L位增加L+1位,LUTs所需的存儲容量擴大2n。

可見,采用傳統的設計方法要達到無相位截斷,則需要LUT的字長非常長,占用資源非常大,導致NCOs的成本很高,而這在實際實現過程中是不可行的。

2.3?相位加抖提高SFDR

通過以上的仿真研究可看出,雖然可以通過增加整數位和提高LUTs輸出分辨率的方法來提高SFDR,但因它們要占用大量的資源,因而不是經濟有效的方法。為有效解決雜波問題,必須考慮其他有效的方法。目前的主要技術手段有:

幅度加抖(Amplitude Dithering):在LUT的輸出中加入低水平的噪聲,以打散原有幅度值量化的噪聲結構。

相位加抖(Phase Dithering):在累加器的輸出中加入低水平的噪聲,以打散原有相位截斷的噪聲結構。

帶通濾波(Bandpass Filtering):在振蕩器輸出端加濾波器濾出毛刺頻率。但該方法很難濾出靠近中心頻率的雜波。

以上的仿真已經證明,相位截斷對SFDR的影響量是最大的,是提高SFDR的首選方法。

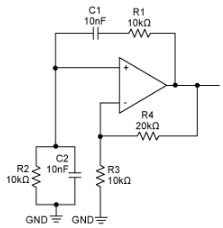

相位加抖的數學模型如圖5所示。在LUTs地址字截斷之前,在累加器的輸出中加入低水平的偽隨機噪聲(A Low-level of Pseudo Random Noise),其中抖動的位數d是可變的。

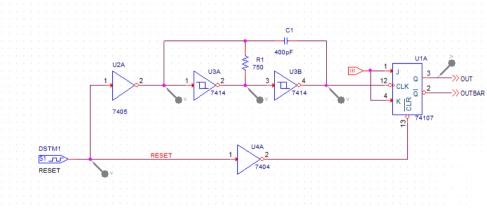

抖動(Dither)可以通過線性反饋移位寄存器(Linear Feedback Shift Register,LFSR)來實現,見圖6。LFSR有帶M個抽頭的移位寄存器,抽頭反饋通常由或門構成,以產生一個周期為2M-1的序列。因此,長偽隨機噪聲序列(Long Pseudo Random Noise Sequences)可以用很少的硬件資源實現。例如,一個由12個元件構成的LFSR能夠生成周期為4 095的PN序列。LFSR可以由M個D觸發器和很少的組合器件構成。

來自某位的抽頭,可以組合為一個矢量生成該位的抖動。實際實現時,可以采用較長的移位寄存器。移位寄存器越長,則輸出的抖動越接近隨機的性質。

下面分析相位加抖數據位數d對SFDR的影響。圖7~圖9分別為d=b-3,b+3,b三種情況的仿真波形,其中b為累加器控制字小數部分的位數。

加抖位數d=6-3時,僅對整數位產生0~1/8的影響。此時將SFDR提高了1 dB。可見,增加過少位數的抖動,僅對相位的截斷有很小的影響,對改變雜波極為有限。

加抖位數d=b+3時,可以對整數位產生0~8的影響。此時將SFDR提高了9 dB。但同時可以看到,由于增加抖動的位數過多,雖然消除了雜波,但同時也提高了整個頻譜的噪聲電平。

加抖位數d=b時,可以對整個整數位產生0~1影響。此時將SFDR提高到106 dB。同時可以看到,由于增加抖動的位數恰當,既消除了雜波,又提高了整個頻譜的噪聲電平。

在用FPGA實現NCOs時,通過相位加噪可以提高整個輸出頻率的SFDR性能。但從圖3,圖6比較可以看出,在整個電路中串入了加法器,且關鍵路徑包含了兩個部分Dithering和NCOs的加法器,因而限制了整個設計的最大時鐘頻率。

3?結? 語

NCOs在數字通訊中起著非常重要的作用,在FPGA實現時,它可以由一個累加器和一個輸出頻率由步長定義的正弦波查找表的數字硬件構成。SFDR是表明合成正弦波譜純度性能的參數。仿真證明,在NCOs累加器輸出的相位中加入抖動,以提高SFDR性能,是一種簡單有效、低成本的方法。

NCOs可以通過各種方式實現:無限沖擊響應濾波器(IIR filters),坐標旋轉(CORDIC rotations),查找表技術(Lookup Tables,LUTs)。本文在Simulink軟件平臺仿真LUTs技術實現NCOs時,累加器步長、累加器控制字等參數對NCOs性能的影響。重點討論NCOs的頻譜純度問題,即如何抑制雜波分量,影響頻譜純度的因素以及如何提高無雜散動態范圍(SpuriousFree Dynamic Range,SFDR)。

1 NCOs的工作原理

NCOs主要包括一個正弦波樣點查找表(LUTs)和一個產生地址的累加器,如圖1所示。

圖1中n為累加器產生的地址位數,則LUTs有N=2n個輸入。LUTs的輸出分辨率/精度為L位(該參數與n有關),其工作原理見圖2。

由圖2可以看出,累加器產生地址碼,循環從LUTs地址中取數正弦波的樣點數據,其取數的速率越快,即步長μ越大,則產生的正弦波頻率越高。

設步長參數μ由式(1)決定:

?

式中:N為LUTs的樣點數據總量;fs為系統采樣頻率;fd為期望的正弦波的頻率。

例如,累加器地址數據線寬度為8 b,則對應的LUTs的數據樣點數為N=2n=256。如果采樣頻率為10 MHz,期望頻率為2.5 MHz,則步長為:

2 提高NCOs的無雜散動態范圍

SFDR是無線系統設計中需要考慮的重要參數。如果振蕩器產生的信號包含過多的雜波(Spurs)頻率,這些干擾成分會使信號混頻的質量變差,特別是當雜波頻率接近中心頻率時,在后續的電路中很難去除。

2.1?相位截斷對頻譜純度的影響

當LUT輸出正弦波樣點數據時,只有整數部分可以用于輸出,而小數部分則被忽略,這導致輸出相位部分有截斷。相位截斷(Phase Truncation)的情況決定了產生的正弦波的純度。如:當采樣頻率為100 kHz時,NCOs輸出的期望頻率為24.3 kHz,其NCOs設置參數見表1。從表1中可以看出,LUTs的分辨率為32 b,則可以忽略幅度值量化的影響,而雜波主要是由相位截斷產生的。?

?

2.2? 幅度值量化對頻譜純度的影響

將LUT的深度增大為12 b(4 096),則可以忽略相位舍去對頻譜純度的影響,而雜波主要由幅度值的量化(Amplitude Quantization)產生。同樣,當采樣頻率為100 kHz時,NCOs輸出的期望頻率24.3 kHz,NCOs設置參數見表2。

由圖3,圖4可以看出,相位截斷產生的雜波遠大于幅度值量化產生的雜波,是雜波的主要來源。

由以上的仿真波形可以看出,提高整數位的位數,雖然可以使相位截斷小,頻率雜波少,但要使用較大的LUTs容量。如整數位增加一位,即由n位增加n+1位,則LUTs的數據量會增加一倍。

提高小數位的位數可以有較高的步長精度和頻率分辨率,但需要更加多的累加器。如小數部分由b位增加到b+1位,雖然對LUTs無影響,但將累加器的加法器和延遲器分別增加1位,從而影響NCOs的輸出頻率。

提高LUTs輸出分辨率對正弦波樣點的幅度值量化影響小,但需要更多的LUTs存儲器。如LUTs輸出分辨率增加1位,由L位增加L+1位,LUTs所需的存儲容量擴大2n。

可見,采用傳統的設計方法要達到無相位截斷,則需要LUT的字長非常長,占用資源非常大,導致NCOs的成本很高,而這在實際實現過程中是不可行的。

2.3?相位加抖提高SFDR

通過以上的仿真研究可看出,雖然可以通過增加整數位和提高LUTs輸出分辨率的方法來提高SFDR,但因它們要占用大量的資源,因而不是經濟有效的方法。為有效解決雜波問題,必須考慮其他有效的方法。目前的主要技術手段有:

幅度加抖(Amplitude Dithering):在LUT的輸出中加入低水平的噪聲,以打散原有幅度值量化的噪聲結構。

相位加抖(Phase Dithering):在累加器的輸出中加入低水平的噪聲,以打散原有相位截斷的噪聲結構。

帶通濾波(Bandpass Filtering):在振蕩器輸出端加濾波器濾出毛刺頻率。但該方法很難濾出靠近中心頻率的雜波。

以上的仿真已經證明,相位截斷對SFDR的影響量是最大的,是提高SFDR的首選方法。

相位加抖的數學模型如圖5所示。在LUTs地址字截斷之前,在累加器的輸出中加入低水平的偽隨機噪聲(A Low-level of Pseudo Random Noise),其中抖動的位數d是可變的。

抖動(Dither)可以通過線性反饋移位寄存器(Linear Feedback Shift Register,LFSR)來實現,見圖6。LFSR有帶M個抽頭的移位寄存器,抽頭反饋通常由或門構成,以產生一個周期為2M-1的序列。因此,長偽隨機噪聲序列(Long Pseudo Random Noise Sequences)可以用很少的硬件資源實現。例如,一個由12個元件構成的LFSR能夠生成周期為4 095的PN序列。LFSR可以由M個D觸發器和很少的組合器件構成。

來自某位的抽頭,可以組合為一個矢量生成該位的抖動。實際實現時,可以采用較長的移位寄存器。移位寄存器越長,則輸出的抖動越接近隨機的性質。

下面分析相位加抖數據位數d對SFDR的影響。圖7~圖9分別為d=b-3,b+3,b三種情況的仿真波形,其中b為累加器控制字小數部分的位數。

加抖位數d=6-3時,僅對整數位產生0~1/8的影響。此時將SFDR提高了1 dB。可見,增加過少位數的抖動,僅對相位的截斷有很小的影響,對改變雜波極為有限。

加抖位數d=b+3時,可以對整數位產生0~8的影響。此時將SFDR提高了9 dB。但同時可以看到,由于增加抖動的位數過多,雖然消除了雜波,但同時也提高了整個頻譜的噪聲電平。

加抖位數d=b時,可以對整個整數位產生0~1影響。此時將SFDR提高到106 dB。同時可以看到,由于增加抖動的位數恰當,既消除了雜波,又提高了整個頻譜的噪聲電平。

在用FPGA實現NCOs時,通過相位加噪可以提高整個輸出頻率的SFDR性能。但從圖3,圖6比較可以看出,在整個電路中串入了加法器,且關鍵路徑包含了兩個部分Dithering和NCOs的加法器,因而限制了整個設計的最大時鐘頻率。

3?結? 語

NCOs在數字通訊中起著非常重要的作用,在FPGA實現時,它可以由一個累加器和一個輸出頻率由步長定義的正弦波查找表的數字硬件構成。SFDR是表明合成正弦波譜純度性能的參數。仿真證明,在NCOs累加器輸出的相位中加入抖動,以提高SFDR性能,是一種簡單有效、低成本的方法。

電子發燒友App

電子發燒友App

評論