現代集成電路芯片中,隨著設計規模的不斷擴大。一個系統中往往含有數個時鐘。多時鐘帶來的一個問題就是,如何設計異步時鐘之間的接口電路。異步 FIFO(First In First Out)是解決這個問題的一種簡便、快捷的解決方案。##異步FIFO的VHDL語言實現

2014-05-28 10:56:41 3405

3405 大家好,又到了每日學習的時間了,今天我們來聊一聊基于FPGA的異步FIFO的實現。 一、FIFO簡介 FIFO是英文First In First Out 的縮寫,是一種先進先出的數據緩存器,它與普通

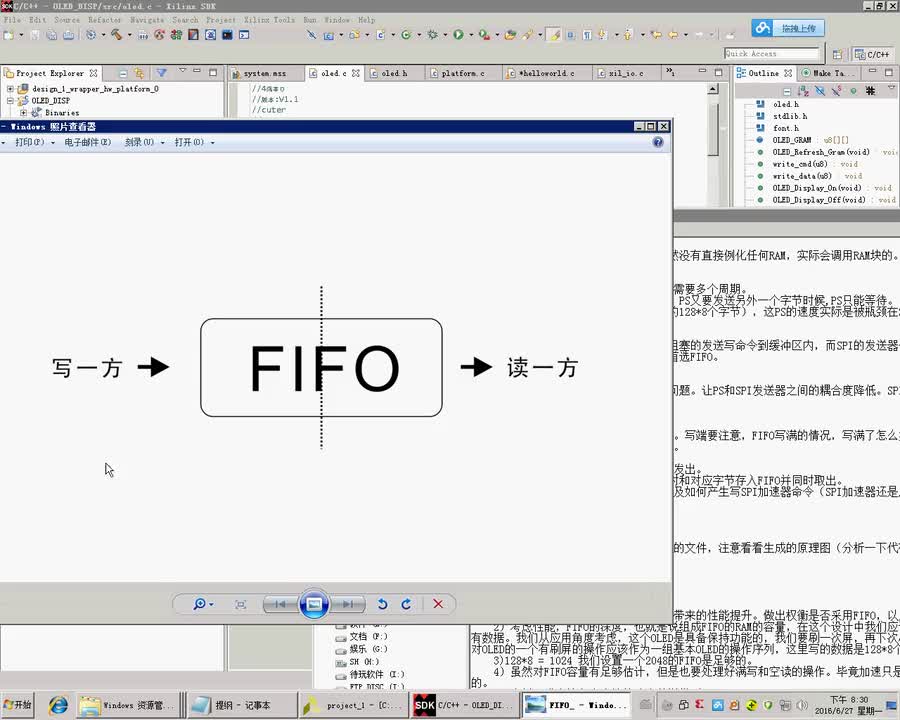

2018-06-21 11:15:25 6164

6164

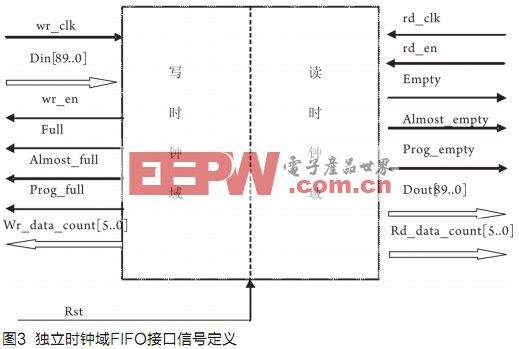

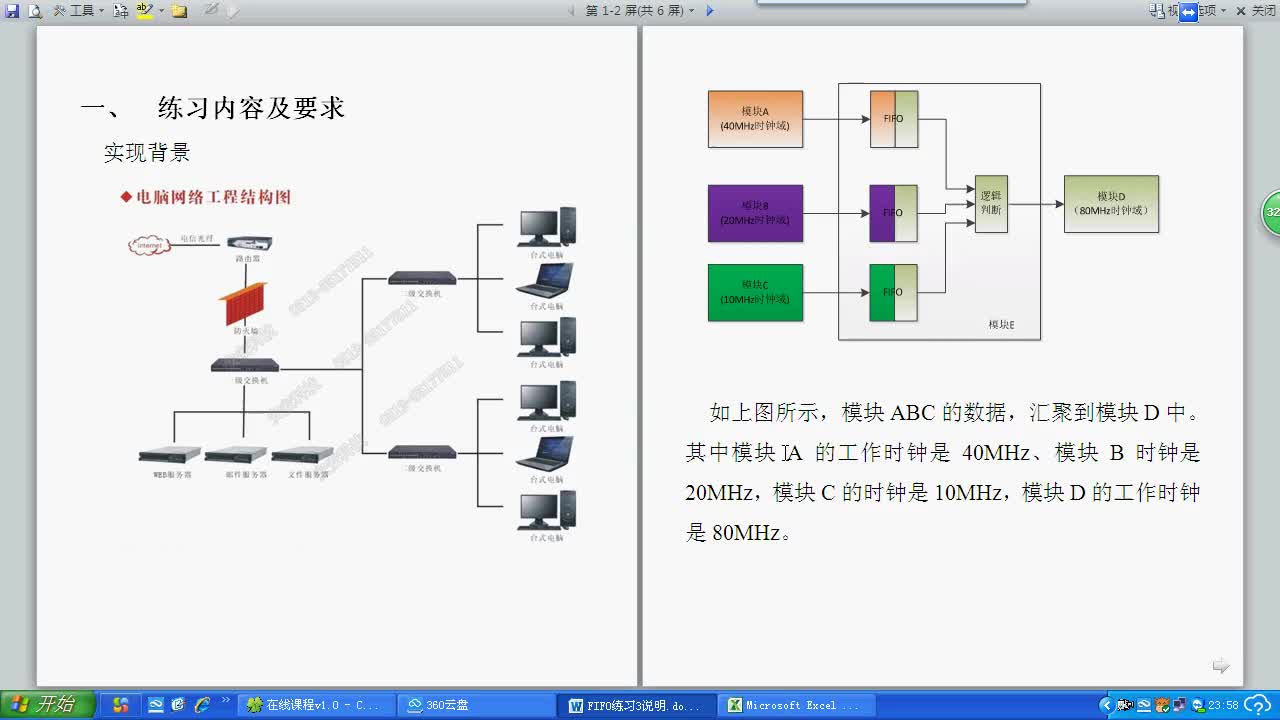

異步 FIFO 讀寫分別采用相互異步的不同時鐘。在現代集成電路芯片中,隨著設計規模的不斷擴大,一個系統中往往含有數個時鐘,多時鐘域帶來的一個問題就是,如何設計異步時鐘之間的接口電路。異步 FIFO

2020-07-16 17:41:46 1050

1050

,它是7系列FPGA新設計的IO專用FIFO,主要用于IOLOGIC(例如ISERDES、IDDR、OSERDES或ODDR)邏輯功能的擴展。 FPGA的每個BANK有4個IN_FIFO

2020-11-29 10:08:00 2340

2340

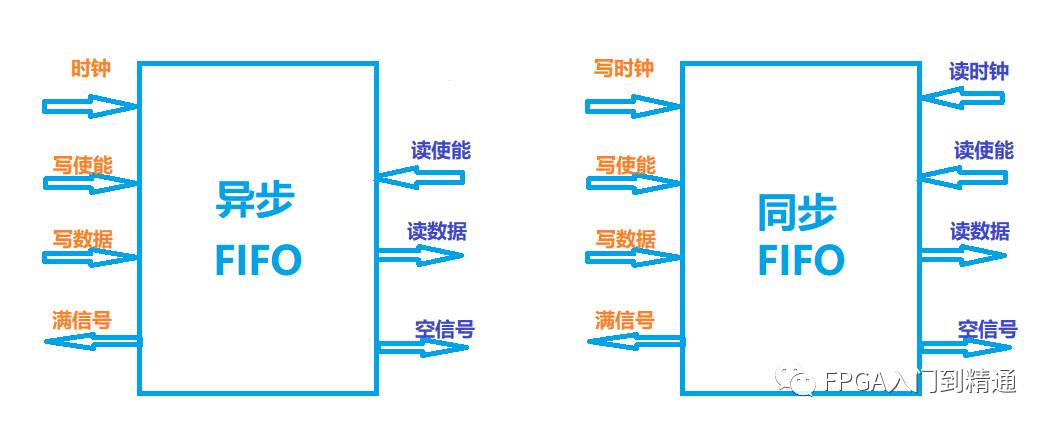

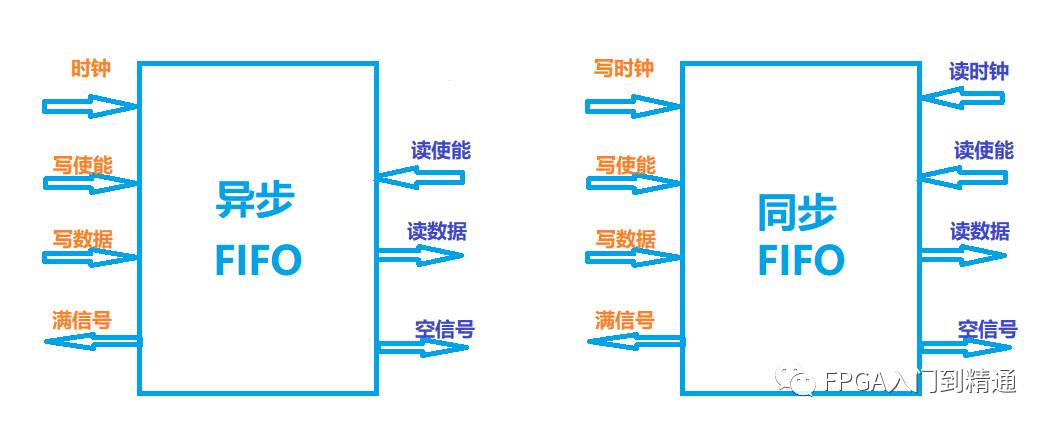

FIFO (先入先出, First In First Out )存儲器,在 FPGA 和數字 IC 設計中非常常用。 根據接入的時鐘信號,可以分為同步 FIFO 和異步 FIFO 。

2023-06-27 10:24:37 1199

1199

各位好,我想完成一個能往FPGA串口一下發多個字節的程序,在網上找了很久,都說是要加一個FIFO,有沒有相關的資料,謝謝了!

2013-12-07 17:00:57

華為FPGA關于FIFO的經驗之談!

2015-07-16 16:05:45

我在自己的流媒體應用(我們收集的高速串行數據流,將其轉換為并行,運輸起來USB)。我們有一個FPGA做的串口- >;并行轉換,做自己的內部fifoing,喂養FX2接口作為一個主人的奴隸。(8

2019-07-24 13:31:58

1 功能概述該工程實例內部系統功能框圖如圖所示。我們通過IP核例化一個FIFO,定時寫入數據,然后再讀出所有數據。通過ISE集成的在線邏輯分析儀chipscope,我們可以觀察FPGA片內FIFO

2019-04-08 09:34:42

FPGA調試技術資料“中國高速列車網絡控制系統”課題組提供資料FPGA常用調試技術?查看綜合報告?仿真測試?在線調試?其他工具FPGA調試技術資料[hide][/hide]

2012-03-09 14:33:28

大俠好,歡迎來到FPGA技術江湖。本系列將帶來FPGA的系統性學習,從最基本的數字電路基礎開始,最詳細操作步驟,最直白的言語描述,手把手的“傻瓜式”講解,讓電子、信息、通信類專業學生、初入職場小白

2023-06-16 17:50:31

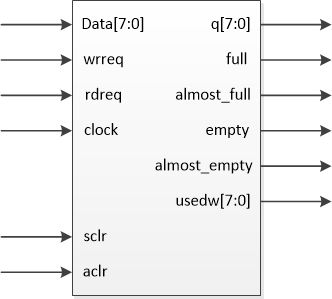

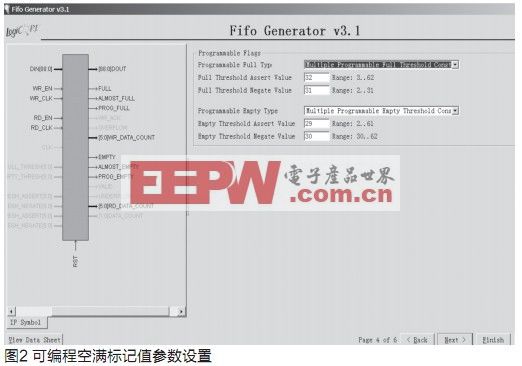

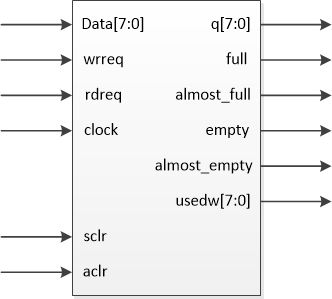

100MHz、輸出速率為50MHz和各類標志信號的FIFO。 · 設計原理FPGA內部沒有FIFO的電路,實現原理為利用FPGA內部的SRAM和可編程邏輯實現。 quartus軟件中提供了FIFO的ip

2023-03-15 16:19:35

高速模擬電路設計技術 [hide]高速模擬電路設計技術.rar[/hide]

2009-10-08 15:02:51

闡述了EDA技術與FPGA設計應用。關鍵詞:電子設計自動化;現場可編程門陣列;復雜可編程邏輯器件;專用集成電路;知識產權;甚高速集成電路硬件描述語言

2019-06-18 07:33:04

闡述了EDA技術與FPGA設計應用。關鍵詞:電子設計自動化;現場可編程門陣列;復雜可編程邏輯器件;專用集成電路;知識產權;甚高速集成電路硬件描述語言

2019-06-27 08:01:28

Xilinx FPGA入門連載51:FPGA片內FIFO實例之功能概述特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1 功能概述該工程

2016-02-26 10:26:05

Xilinx FPGA入門連載52:FPGA片內FIFO實例之FIFO配置特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm1新建源文件打開

2016-02-29 13:35:55

Xilinx FPGA入門連載52:FPGA片內FIFO實例之FIFO配置特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm1新建源文件打開

2016-02-29 13:35:55

`Xilinx FPGA入門連載55:FPGA 片內異步FIFO實例之功能概述特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1 功能

2016-03-07 11:32:16

本帖最后由 電氣學渣 于 2017-2-16 20:14 編輯

cRIO采集的模擬量,然后通過FIFO進行傳遞。在FPGA Target創建DAQ_FPGA.vi,使用FIFO保存采集的模擬量

2017-02-16 20:11:01

高速、超寬帶信號采集技術在雷達、天文和氣象等領域應用廣泛。高采樣率需要高速的模/數轉換器(ADC)。目前市場上單片高速ADC的價格昂貴,分辨率較低,且采用單片超高速ADC實現的數據采集對FPGA的性能和PCB布局布線技術提出了嚴峻的挑戰。

2019-11-08 06:34:52

以FPGA為橋梁的FIFO設計方案是什么?以FPGA為橋梁的FIFO有哪些應用?

2021-04-29 07:05:18

摘要:RS 232接口是現在最常用的一種通信接口。隨著FPGA技術的高速發展,一些常見的接口電路的時序電路可以通過FPGA實現,通過這種設計可減少電路系統元件的數量,提高系統集成度和可靠性。詳細闡述

2019-06-19 07:42:37

復雜可編程邏輯器件—FPGA技術在近幾年的電子設計中應用越來越廣泛。FPGA具有的硬件邏輯可編程性、大容量、高速、內嵌存儲陣列等特點使其特別適合于高速數據采集、復雜控制邏輯、精確時序邏輯等場合的應用。而應用FPGA中的存儲功能目前還是一個較新的技術。

2019-10-12 07:32:24

FPGA數字信號處理——基于FPGA和高速DAC的DDS設計與頻率調制(一)——X現如今,隨著高速模數-數模轉換技術和FPGA的發展。FPGA的高速性、并行性、高數據吞吐量與高速數模-模數轉換技術

2021-07-23 08:06:59

的輸入輸出接口設計就顯得尤為重要。1 高速采集系統介紹 數據采集系統原理框圖如圖1所示,輸入的中頻信號經A/D采樣電路采樣后,轉換成LVDS信號送入FPGA中,或通過FPGA的端口RocketIO從高速接口

2018-12-18 10:22:18

之一是參考FPGA制造商提供的參考板。絕大部分制造商會提供參考板的源版圖信息,雖然由于私有信息問題可能需要特別申請。這些電路板通常包含標準的高速I/O接口,因為FPGA制造商在表征和認證他們的器件

2018-11-27 10:07:39

發生什么的專業版圖設計師相互合作的成果。通常,對最終電路板的成敗負責的是原理圖設計師。但是,原理圖設計師對優秀的版圖技術懂得越多,避免出現重大問題的機會就越多。 如果設計中含有高密度的FPGA,很可能

2019-07-10 06:22:53

的網絡數據傳輸。3、 系統結構高速同步數據采集系統主要包括以下幾個部分:ARM控制器、存儲電路、FPGA邏輯控制電路、A/D轉換電路、FIFO緩存、電源電路、接口電路等。系統具備多通道數據采集接口

2010-08-31 09:14:55

引 言在高速的數據采集或傳輸中,目前使用較多的都是采用USB 2.0接口控制器和FPGA或DSP實現的,本設計在USB 2.0接口芯片CY7C68013的Slave FIFO模式下,利用FPGA作為

2021-06-24 07:00:00

數據進入FPGA的速率高于傳出的速率,持續的傳輸會造成數據的溢出,斷續的傳輸可能會造成數據不連續。使用基于LabVIEW FPGA的DMA FIFO作為主控計算機和FPGA之間的緩存,若DMAFIFO深度設置的合適,FIFO不會溢出和讀空,那么就能實現數據輸出FPGA是連續的。

2019-10-12 09:05:54

,影響系統可靠性,要進一步提高系統實時性,必須研究開發高速嵌入式雷達信號采集系統。這里結合高速嵌入式數據采集系統,提出一種基于CvcloneⅢFPGA實現的異步FIFO和鎖相環(PLL)結構來實現

2019-08-21 06:56:32

)-SPIXMOSI)來配置FPGA,然后使GPFI到32位從FIFO模式,顯然是可行的。在固件運行時,我想再次用SPI接口重新配置FPGA,但在那個時候,GPIF是32位從FIFO模式,我可以停止

2019-01-29 12:35:48

結合高速嵌入式數據采集系統,提出一種基于CvcloneⅢ FPGA實現的異步FIFO和鎖相環(PLL)結構來實現高速緩存,該結構可成倍提高數據流通速率,增加數據采集系統的實時性。采用FPGA設計高速緩存,能針對外部硬件系統的改變,通過修改片內程序以應用于不同的硬件環境。

2021-04-30 06:19:52

圖像壓縮之后的數據存入fifo,然后經過nrf2401發送。。但是由于圖片尺寸比較大,導致fifo深度不夠,受限于FPGA芯片尺寸的限制,fifo深度不能再選大了。。。求指導

2015-05-22 14:34:48

In First Out)存儲器憑借其操作簡單、可靠性好等特點,被廣泛的應用于數據采集系統中,成為了連接MCU與AD芯片的橋梁。為了使MCU、AD芯片以及高速FIFO存儲器能夠協調工作,就需要設計好這

2019-05-23 05:01:08

首先介紹異步FIFO 的概念、應用及其結構,然后分析實現異步FIFO的難點問題及其解決辦法; 在傳統設計的基礎上提出一種新穎的電路結構并對其進行綜合仿真和FPGA 實現。

2009-04-16 09:25:29 46

46 利用參數可設置模塊庫(LPM)中的兆功能模塊,根據實際系統的需要,對其參數進行必要的調整設置,介紹了一個高速FIFO 存儲器的設計方法和步驟,給出了仿真結果,方便實用。

2009-09-02 09:33:50 26

26 基于高速FPGA的PCB設計技術:如果高速PCB 設計能夠像連接原理圖節點那樣簡單,以及像在計算機顯示器上所看到的那樣優美的話,那將是一件多么美好的事情。然而,除非設計師初入PC

2009-09-20 18:02:02 32

32 介紹了PCI 9054 接口芯片的性能及數據傳輸特點,提出了一種基于PCI 9054 外擴異步FIFO(先進先出)的FPGA(現場可編程門陣列)實現方法。由于PCI 9054 內部FIFO存儲器主要用于數據

2010-01-06 15:20:10 44

44 本文主要研究了用FPGA 芯片內部的EBRSRAM 來實現異步FIFO 設計方案,重點闡述了異步FIFO 的標志信號——空/滿狀態的設計思路,并且用VHDL 語言實現,最后進行了仿真驗證。

2010-01-13 17:11:58 40

40 摘要:文章介紹了一個正向設計,并已成功流片的FIFO存儲器電路結構設計及關鍵技術.重點研究了實現該電路的兩類關鍵技術,存儲電路和控制邏輯。文中的設計思想和具體的邏輯

2010-05-04 08:48:53 17

17 介紹了異步FIFO在Camera Link接口中的應用,將Camera Link接口中的幀有效信號FVAL和行有效信號LVAL引入到異步FIFO的設計中。分析了FPGA中設計異步FIFO的難點,解決了異步FIFO設計中存在的兩

2010-07-28 16:08:06 32

32 以CPLD為邏輯控制核心實現了ADS8323與高速FIFO的接口電路,該電路具有可靠性高、通用性強、易于移植等特點。在設計過程中,以QuartusII作為開發環境,采用圖形輸入和Verilog HDL語言輸

2010-08-06 14:25:53 22

22 設計工程師通常在FPGA上實現FIFO(先進先出寄存器)的時候,都會使用由芯片提供商所提供的FIFO。但是,由于其通用性使得其針對性變差,某些情況下會變得不方便或者將增加硬

2010-10-27 15:40:30 38

38 介紹了一種基于CPLD(復雜可編程邏輯器件)和FIFO(先入先出存儲器)的多通道高速A/D數據采集系統的設計方法,并給出了這種數據采集方法的硬件原理電路和主要的軟件設計思路

2009-05-05 20:50:09 1651

1651

摘要:首先介紹異步FIFO的概念、應用及其結構,然后分析實現異步FIFO的難點問題及其解決辦法;在傳統設計的基礎上提出一種新穎的電路結構并對其進行

2009-06-20 12:46:50 3667

3667

基于FPGA的高速時鐘數據恢復電路的實現

時鐘數據恢復電路是高速收發器的核心模塊,而高速收發器是通信系統中的關鍵部分。隨著光纖在通信中的應用,信道可以承載

2009-10-25 10:29:45 3626

3626

基于FPGA的FIFO設計和應用

引 言

在利用DSP實現視頻實時跟蹤時,需要進行大量高速的圖像采集。而DSP本身自帶的FIFO并不足以支持系統中大量數據的暫時存儲

2009-11-20 11:25:45 2127

2127

異步FIFO和PLL在高速雷達數據采集系統中的應用

1 引言 隨著雷達系統中數字處理技術的飛速發展,需要對雷達回波信號進行高速數據采集。在嵌入式條

2009-12-22 17:41:08 2082

2082

高速異步FIFO的設計與實現

引言

現代集成電路芯片中,隨著設計規模的不斷擴大.一個系統中往往含有數個時鐘。多時鐘帶來的一個問題就是,如何設

2010-04-12 15:13:08 2790

2790

本文采用VHDL描述語言,充分利用Xilinx公司Spartan II FPGA的系統資源,設計實現了一種非對稱同步FIFO,它不僅提供數據緩沖,而且能進行數據總線寬度的轉換。

2011-01-13 11:33:43 1744

1744 為了解決基于LabVIEWFPGA模塊的DMAFIFO深度設定不當帶來的數據不連續問題,結合LabVIEWFPGA的編程特點和DMA FIFO的工作原理,提出了一種設定 FIFO 深度的方法。對FIFO不同深度的實驗表明,采

2011-09-26 13:45:17 6923

6923

文中給出了異步FIFO的實現代碼和FPGA與DSP的硬件連接電路。經驗證,利用異步FIFO的方法,在FPGA與DSP通信中的應用,具有傳輸速度快、穩定可靠、實現方便的優點。

2011-12-12 14:28:22 51

51 為實現目標識別與跟蹤的應用目的 ,在基于 TMS320DM642 的 FIFO 基礎上擴展存儲空間 ,提出一種基于

FPGA實現 SDRAM 控制器的方法。分析所用 SDRAM 的特點和工作原理

2015-10-29 14:05:57 2

2 異步FIFO結構及FPGA設計,解決亞穩態的問題

2015-11-10 15:21:37 4

4 異步FIFO在FPGA與DSP通信中的運用

2016-05-19 11:17:11 0

0 高速電路板設計技術

2017-01-12 12:35:15 0

0 DSP與FPGA高速的數據傳輸有三種常用接口方式: EMIF, HPI 和 McBSP 方式。而采用 EMIF 接口方式, 利用 FPGA ( 現場可編程邏輯門陣列) 設計 FIFO的接口電路,即可實現高速互聯。

2017-02-11 14:16:10 2487

2487

基于異步FIFO在FPGA與DSP通信中的運用

2017-10-19 10:30:56 10

10 基于FIFO的高速A_D和DSP接口設計

2017-10-19 14:10:23 9

9 代碼和FPGA與DSP的硬件連接電路。經驗證,利用異步FIFO的方法,在FPGA與DSP通信中的應用,具有傳輸速度快、穩定可靠、實現方便的優點。 關鍵詞 異步FIFO;FPGA與DSP數據通信;EMIFA

2017-10-30 11:48:44 1

1 在現代電路設計中,一個系統往往包含了多個時鐘,如何在異步時鐘間傳遞數據成為一個很重要的問題,而使用異步FIFO可以有效地解決這個問題。異步FIFO是一種在電子系統中得到廣泛應用的器件,文中介紹了一種基于FPGA的異步FIFO設計方法。使用這種方法可以設計出高速、高可靠的異步FIFO。

2018-07-17 08:33:00 7873

7873

)片上集成的高速FIFO實現采集數據的高速緩存并通過對高速FIFO的讀寫操作實現總線同步數據傳輸,提高數據的傳輸速率。

2018-07-12 09:06:00 4707

4707

設計工程師通常在FPGA上實現FIFO(先進先出寄存器)的時候,都會使用由芯片提供商所提供的FIFO。但是,由于其通用性使得其針對性變差,某些情況下會變得不方便或者將增加硬件成本。此時,需要進行自行

2018-11-28 08:10:00 6709

6709

為了解決基于LabVIEWFPGA模塊的DMAFIFO深度設定不當帶來的數據不連續問題,結合LabVIEWFPGA的編程特點和DMA FIFO的工作原理,提出了一種設定FIFO深度的方法。對FIFO

2019-01-04 14:25:07 4225

4225

FIFO隊列具有處理簡單,開銷小的優點。但FIFO不區分報文類型,采用盡力而為的轉發模式,使對時間敏感的實時應用(如VoIP)的延遲得不到保證,關鍵業務的帶寬也不能得到保證。

2019-12-02 07:02:00 1471

1471

FIFO隊列具有處理簡單,開銷小的優點。但FIFO不區分報文類型,采用盡力而為的轉發模式,使對時間敏感的實時應用(如VoIP)的延遲得不到保證,關鍵業務的帶寬也不能得到保證。

2019-11-29 07:10:00 1595

1595 根據FIFO工作的時鐘域,可以將FIFO分為同步FIFO和異步FIFO。同步FIFO是指讀時鐘和寫時鐘為同一個時鐘。在時鐘沿來臨時同時發生讀寫操作。異步FIFO是指讀寫時鐘不一致,讀寫時鐘是互相獨立的。

2019-11-29 07:08:00 1609

1609 FIFO隊列不對報文進行分類,當報文進入接口的速度大于接口能發送的速度時,FIFO按報文到達接口的先后順序讓報文進入隊列,同時,FIFO在隊列的出口讓報文按進隊的順序出隊,先進的報文將先出隊,后進的報文將后出隊。

2019-11-29 07:04:00 4345

4345 FIFO( First Input First Output)簡單說就是指先進先出。由于微電子技術的飛速發展,新一代FIFO芯片容量越來越大,體積越來越小,價格越來越便宜。作為一種新型大規模集成電路

2019-09-20 07:04:00 1941

1941

FIFO( First Input First Output)簡單說就是指先進先出。由于微電子技術的飛速發展,新一代FIFO芯片容量越來越大,體積越來越小,價格越來越便宜。

2019-11-18 07:10:00 1605

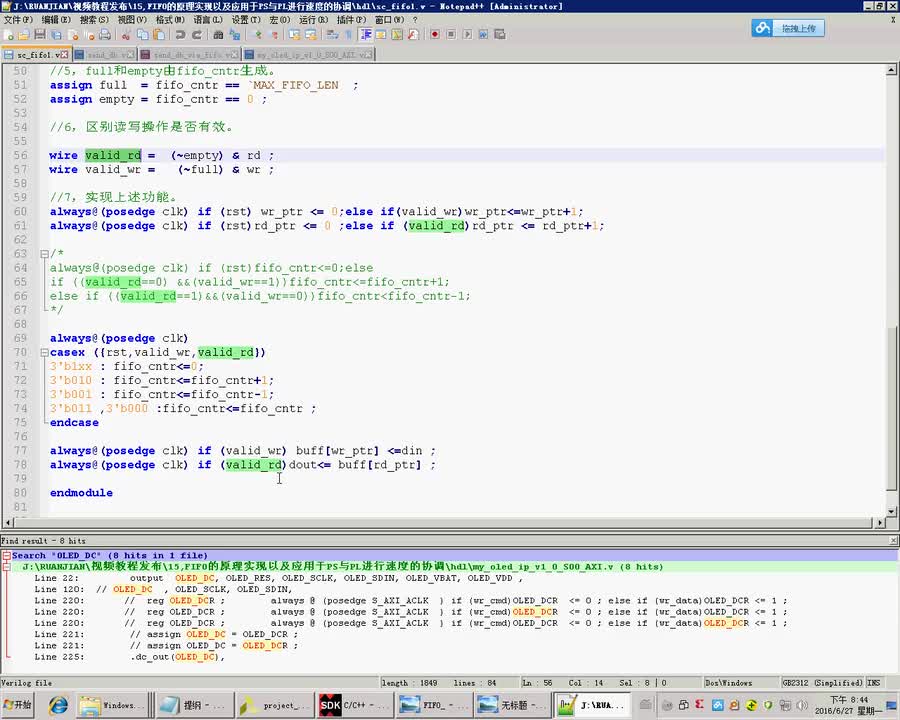

1605 FPGA電路FIFO設計的源代碼

2020-07-08 17:34:37 15

15 FIFO是FPGA應用當中非常重要的模塊,廣泛用于數據的緩存,跨時鐘域數據處理等。學好FIFO是FPGA的關鍵,靈活運用好FIFO是一個FPGA工程師必備的技能。本章主要介紹利用XILINX提供的FIFO IP進行讀寫測試。

2021-02-02 06:24:38 11

11 FIFO是FPGA處理跨時鐘和數據緩存的必要IP,可以這么說,只要是任意一個成熟的FPGA涉及,一定會涉及到FIFO。但是我在使用異步FIFO的時候,碰見幾個大坑,這里總結如下,避免后來者入坑。

2021-03-12 06:01:34 12

12 一:fifo是什么 FIFO的完整英文拼寫為FirstIn First Out,即先進先出。FPGA或者ASIC中使用到的FIFO一般指的是對數據的存儲具有先進先出特性的一個存儲器,常被用于數據

2021-03-12 16:30:48 2796

2796

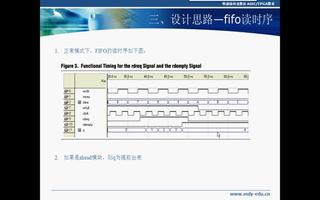

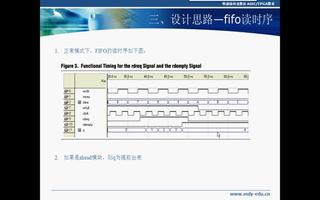

FIFO是在FPGA設計中使用的非常頻繁,也是影響FPGA設計代碼穩定性以及效率等得關鍵因素。在數據連續讀取時,為了能不間斷的讀出數據而又不導致FIFO為空后還錯誤的讀出數據。可以將FIFO

2021-09-09 11:15:00 6293

6293 FIFO是FPGA項目中使用最多的IP核,一個項目使用幾個,甚至是幾十個FIFO都是很正常的。通常情況下,每個FIFO的參數,特別是位寬和深度,是不同的。

2022-03-08 11:06:12 4520

4520

在FPGA中對圖像的一行數據進行緩存時,可以采用FIFO這一結構,如上圖所示,新一行圖像數據流入到FIFO1中,FIFO1中會對圖像數據進行緩存,當FIFO1中緩存有一行圖像數據時,在下一行圖像數據來臨的時候,將FIFO1中緩存的圖像數據讀出,并傳遞給下一個FIFO

2022-05-10 09:59:29 3056

3056 無論何時,在復雜的 FPGA 設計過程中,都不可避免地需要在模塊之間發送數據,實現這一點的常用的是 FIFO。

2022-09-20 09:10:27 1883

1883 位寬變換:對于不同寬度的數據接口也可以用FIFO,例如單片機位8位數據輸出,而DSP可能是16位數據輸入,在單片機與DSP連接時就可以使用FIFO來達到數據匹配的目的。

2022-11-09 20:00:03 1253

1253 用來做數據的緩存,或者用來解決高速異步數據的交互,即解決了跨時鐘域的問題。此外,FIFO還有一個特點,就是數據被讀出之后就不存在了,不像RAM和ROM一樣,數據被讀出后還存在。所以我們如果想進行多次的讀,那么就需要進行同樣次數的寫。

2023-06-09 09:38:02 2021

2021

FIFO 是FPGA設計中最有用的模塊之一。FIFO 在模塊之間提供簡單的握手和同步機制,是設計人員將數據從一個模塊傳輸到另一個模塊的常用選擇。

2023-06-14 08:59:29 223

223 在FPGA的設計中的,內部的FIFO和RAM是兩種非常常見的存儲單元

2023-07-11 17:23:33 956

956 FIFO,先進先出。在FPGA中使用的FIFO一般是指對數據的存儲具有先進先出的緩沖器,FIFO與普通的存儲器的不同在于它沒有讀寫地址線。舉個例子,當FPGA從外部傳感器讀取到一連串數據時,首先

2023-07-23 11:47:03 369

369

FIFO(First In First Out)是一種先進先出的存儲結構,經常被用來在FPGA設計中進行數據緩存或者匹配傳輸速率。

2023-08-07 15:39:50 446

446 FPGA廠商提供了豐富的IP核,基礎性IP核都是可以直接免費調用的,比如FIFO、RAM等等。

2023-08-07 15:41:28 1294

1294

上文XILINX FPGA IP之FIFO對XILINX FIFO Generator IP的特性和內部處理流程進行了簡要的說明,本文通過實際例子對該IP的使用進行進一步的說明。本例子例化一個讀數據位寬是寫數據位寬兩倍的FIFO,然后使用讀時鐘頻率:寫時鐘頻率=2:3,進行簡單的FIFO跨時鐘域操作。

2023-09-07 18:31:35 759

759

正在加载...

電子發燒友App

電子發燒友App

評論