脈沖壓縮技術是指對雷達發射的寬脈沖信號進行調制(如線性調頻、非線性調頻、相位編碼),并在接收端對回波寬脈沖信號進行脈沖壓縮處理后得到窄脈沖的實現過程。脈沖壓縮有效地解

2011-09-30 15:09:56 1068

1068

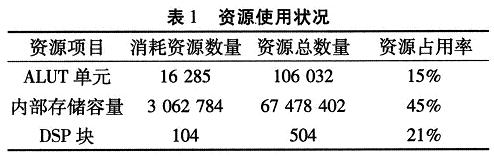

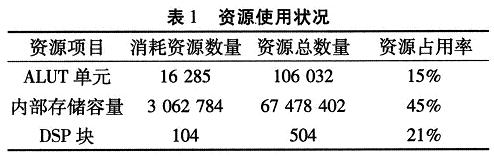

為了研究數字化γ能譜儀,本文提出一種基于FPGA的數字核脈沖分析器硬件設計方案,該方案采用現場可編程邏輯部件(FPGA),完成數字多道脈沖幅度分析儀的硬件設計。用QuartusⅡ軟件在FPGA平臺上完成了數字核脈沖的幅度提取并生成能譜。

2013-11-21 10:57:26 1948

1948

基于FPGA 的數字核脈沖分析器硬件設計方案,該方案采用現場可編程邏輯部件(FPGA),完成數字多道脈沖幅度分析儀的硬件設計。

2015-02-03 09:55:05 1870

1870

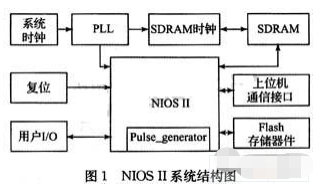

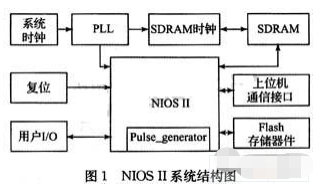

只有設計出了高頻率的、參數化的脈沖發生器,脈沖加工電源的精度、參數化才可以實現。該電源系統中采用的是性價比較好的Altera公司的Cyclone II序列的FPGA芯片EP2C8Q208C7。其邏輯資源足夠實現系統的功能。

2021-02-23 10:01:45 3091

3091

【作者】:陳世海;裴東興;張琦;【來源】:《電子設計工程》2010年02期【摘要】:針對數據采集系統高速長時間的采樣和后端數據傳輸及存儲能力有限的問題,提出基于FPGA的數據壓縮解決方案。同時為平滑

2010-04-24 09:05:21

架構、嵌入式系統、實時操作系統、數字信號處理、圖像與視頻處理和數字通信等,可以實現片上課程理念。七、教學大綱基于Xilinx FPGA的DSP系統設計與實現的課程安排如下: 第一天 課程目標

2009-07-21 09:22:42

分析了抖動偏頻激光陀螺信號的解調原理,提出了一種利用數字信號處理技術并采用FPGA實現的抖動解調方法;通過對激光陀螺脈沖計數值高速采樣并采用數字濾波器濾波處理,可以有效消除抖動引起的信號噪聲,得到

2018-08-30 09:21:12

CCSDS星載圖像壓縮模塊的FPGA設計與實現.pdf

2011-03-16 18:38:44

架構、嵌入式系統、實時操作系統、數字信號處理、圖像與視頻處理和數字通信等,可以實現片上課程理念。七、教學大綱基于Xilinx FPGA的DSP系統設計與實現的課程安排如下:第一天 課程目標

2009-07-21 09:20:11

學習一下該開發板其他例程,提升一下自己,順便也希望可以給他人提供些有用的參考例程。項目描述:1:完成線性調頻信號LFM的數字下變頻DDC(包括正交變換、FIR低通濾波及抽取);2:LFM信號的脈沖壓縮

2015-09-10 11:18:53

什么是數字中頻?FPGA怎么實現數字中頻?

2021-05-08 08:05:40

小弟最近在做一個數字下變頻和脈沖壓縮的仿真,現在一點頭緒都沒有,有沒有大神指教一下方向的。希望大神不吝賜教,或者是有源代碼能分享一下,跪謝了。

2017-03-11 10:50:24

DSP技術廣泛應用于各個領域,但傳統的數字信號處理器由于以順序方式工作使得數據處理速度較低,且在功能重構及應用目標的修改方面缺乏靈活性。而使用具有并行處理特性的FPGA實現數字信號處理系統,具有很強的實時性和靈活性,因此利用FPGA實現數字信號處理成為數字信號處理領域的一種新的趨勢。

2019-10-17 08:12:27

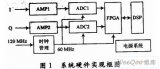

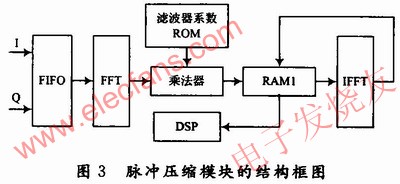

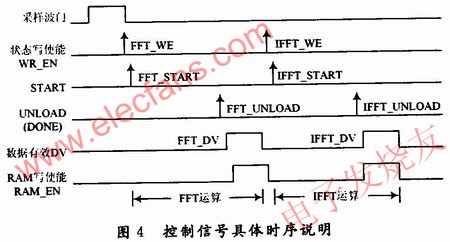

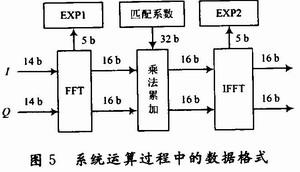

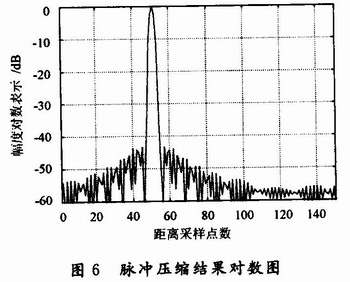

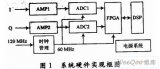

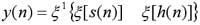

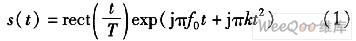

使用。 本文基于快速傅里葉IP核可復用和重配置的特點,實現一種頻域的FPGA數字脈壓處理器,能夠完成正交輸入的可變點LFM信號脈沖壓縮,具有設計靈活,調試方便,可擴展性強的特點。 1 系統功能硬件

2018-11-09 15:53:22

基于FPGA的數字脈沖壓縮技術1.數字脈沖壓縮實現原理2.電路設計2.1APEX2OKE系列FPGA 簡介2.2 基于FPGA 的算法研究及實現 2.3 脈沖壓縮在FPGA 上的實現

2011-03-02 09:41:50

便于改造實現。而信號處理的核心就是數字穩定校正(DSU),DSU的主要作用就是消除發射信號的相位抖動,使接收信號具有相參性。在數字技術飛速發展的今天,信號處理的硬件實現主要有FPGA和DSP等來實現

2015-02-05 15:34:43

調相脈沖信號可以獲得較大的壓縮比,它作為一種常用的脈沖壓縮信號,在現代雷達及通信系統中獲得了廣泛應用。隨著近年來軟件無線電技術和電子技術的發展,DDS(直接數字頻率合成)用于實現信號產生的應用越來越廣。

2019-09-30 07:22:22

基于FPGA的雷達脈沖壓縮系統設計參見附件:

2011-03-02 09:39:11

脈沖壓縮技術是指對雷達發射的寬脈沖信號進行調制(如線性調頻、非線性調頻、相位編碼),并在接收端對回波寬脈沖信號進行脈沖壓縮處理后得到窄脈沖的實現過程。脈沖壓縮有效地解決了雷達作用距離與距離分辨率之間的矛盾,可以在保證雷達在一定作用距離下提高距離分辨率。

2019-10-08 11:16:45

王玲,邱軍海,王世橋(煙臺工程職業技術學院山東煙臺264006)線性調頻信號可以獲得較大的壓縮比,有著良好的距離分辨率和徑向速度分辨率,所以線性調頻信號作為雷達系統中一種常用的脈沖壓縮信號,已經

2019-07-08 07:38:45

視頻過大,打包成8個壓縮包基于FPGA設計的數字時鐘.part01.rar (20 MB )基于FPGA設計的數字時鐘.part02.rar (20 MB )基于FPGA設計的數字時鐘

2019-05-14 06:35:34

基于SOCFPGA的無線圖傳系統關鍵詞 圖傳 SOC 視頻壓縮 信道編碼 COFDM1. 簡介無線數字視頻傳輸系統(圖傳)廣泛應用于利用無人機進行視頻/圖像拍攝,以及視頻監控領域。一般說來,圖傳由

2016-08-17 13:34:22

脈沖壓縮是近年來光子晶體光纖中一個新的應用領域,在光通信系統中,利用具有高非線性系數和較大負色散值的光子晶體光纖進行脈沖壓縮,將降低傳輸時間,提高傳輸速率。本文從非線性薛定諤方程組入手,深入探討

2010-05-28 13:38:25

脈沖壓縮體制在現代雷達中被廣泛采用,通過發射寬脈沖來提高發射的平均功率,保證足夠的作用距離;接收時則采用相應的脈沖壓縮算法獲得脈寬較窄的脈沖,以提高距離分辨力,從而能夠很好地解決作用距離和距離分辨力之間的矛盾問題。

2019-11-08 08:08:55

傅里葉變換、脈沖壓縮、線性預測編碼語音處理、高速定點矩陣乘法等,有較好的應用前景和發展空間。那有誰知道該如何利用FPGA實現級聯信號處理器嗎?

2019-07-30 07:22:48

如何用FPGA實現數字電視條件接收系統?

2021-04-29 06:57:30

本文采用FPGA實現ADPCM(Adaptive Differential Pulse CodeModulation,自適應差分脈沖編碼調制)編解碼器設計,對語音信息進行壓縮存儲。從而使存儲信息量增大了一倍。

2021-05-17 06:26:37

本文提出一種采用FPGA和CMOS數字傳感器實現前端數據采集、利用單片機進行圖像鑒別和壓縮、通過以太網控制器實現圖像數據傳輸的圖像監測系統。該系統不僅實現了圖像信號數據采集,而且數據傳輸速度和穩定性高;不僅靈活性好、成本低,而且具有網絡化、智能化等優點。

2021-05-26 06:58:29

怎么實現基于DSP的視頻圖像壓縮系統的設計?

2021-06-08 06:02:18

數字系統的設計人員擅長在其印制電路板上用FPGA和CPLD將各種處理器、存儲器和標準的功能元件粘合在一起來實現數字設計。除了這些數字功能之外,FPGA和CPLD還可以使用LVDS輸入、簡單的電阻電容(RC)電路和一些FPGA或CPLD的數字邏輯單元實現共模功能,從而構建模數轉換器(ADC)。

2019-08-19 06:15:33

脈沖壓縮體制在現代雷達中被廣泛采用,通過發射寬脈沖來提高發射的平均功率,保證足夠的作用距離;接收時則采用相應的脈沖壓縮算法獲得脈寬較窄的脈沖,以提高距離分辨力,從而能夠很好地解決作用距離和距離分辨力

2019-08-26 07:10:09

如何有效解決雷達作用距離與距離分辨率之間的矛盾?基于FPGA的雷達脈沖壓縮系統設計

2021-04-08 06:02:27

脈沖壓縮網絡,給出了關鍵參數的設計計算,并且介紹了新穎的末級磁脈沖壓縮放電結構。實驗結果顯示:各級磁脈沖壓縮效果達到設計指標,電源輸出電壓峰達30 kV,輸出電流峰值大于40 kA,電流脈沖寬度200

2010-04-22 11:41:29

脈沖壓縮系統工業原理是什么?LFM信號實時脈沖壓縮是如何實現的?TMS320C64x處理器的特點有哪些?

2021-04-19 11:50:02

【作者】:張鵬;和天慧;沈旭明;【來源】:《信息與電子工程》2010年01期【摘要】:為了實現高功率微波初級波源的小型化,獲得更高功率的輸出微波脈沖,研制了用于高功率微波脈沖壓縮的能量倍增器。利用

2010-04-22 11:48:46

傳統的匹配濾波只能將距離旁瓣壓縮到一定的程度,因此可能出現強目標的旁瓣掩蓋弱目標的情況。針對上述問題,該文提出了基于迭代思想和最大輸出信噪比準則的自適應脈沖壓

2009-11-20 16:01:33 10

10 本文設計了一種以 FPGA 為數據壓縮和數據緩存單元的高速數據采集系統,其主要特點是對高速采集的數據進行實時壓縮,再將壓縮后的數據進行緩沖存儲。該設計利用數據比較模

2009-11-30 15:32:36 20

20 BOA單棱鏡飛秒超短脈沖壓縮器 當超短脈沖激光透過材料傳輸時(即使是簡單的玻璃),由于群延遲色散(GDD)它們會在時間上展寬。紅光的傳播速度比藍光的傳播速度

2023-05-24 11:04:06

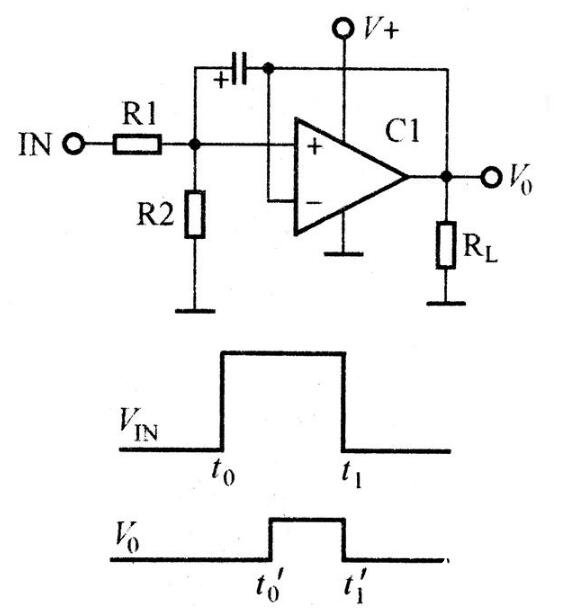

脈沖壓縮透射光柵高功率光束組合光譜衍射光柵 脈沖壓縮透射光柵高功率光束組合光譜衍射光柵采用獨特的圖案化方法、DUV投影光刻和離子蝕刻,為透射衍射光柵提供了許多

2023-05-24 13:50:09

Lightsmyth光通信1550nm脈沖壓縮透射衍射光柵 Lightsmyth光通信1550nm脈沖壓縮透射衍射光柵用于將入射光成角度地分散到光譜中。光通信透射衍射光柵

2023-05-24 13:55:56

發射信號的分離是MIMO 雷達的一個重要環節,該文基于最小均方誤差準則,提出了一種有效的MIMO雷達自適應脈沖壓縮方法,從每個接收陣元接收到的信號中分別自適應地估計每個距

2010-02-09 13:37:38 15

15 描述了Z箍縮放電等離子體極紫外光源系統中的主脈沖電源,給出了主電路拓撲結構,重點介紹了三級磁脈沖壓縮網絡,給出了關鍵參數的設計計算,并且介紹了新穎的末級磁脈沖

2010-03-05 14:13:38 27

27 針對受激布里淵散射(SBS)脈沖壓縮系統中經常出現的波形調制現象,提出一種抑制調制、改善窄脈沖波形質量的新方法——雙級SBS脈沖壓縮結構。此方法以“兩次壓縮,子峰能量

2010-03-05 15:20:08 19

19 為解決機載高分辨率圖像的實時壓縮問題,提出了一個基于FPGA+PowerPC的高分辨率圖像實時壓縮系統的設計方案。本系統主控采用PowerPC 處理器,壓縮芯片采用ADV202,用FPGA實現圖像數

2010-09-15 11:45:25 40

40

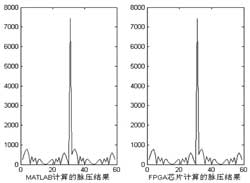

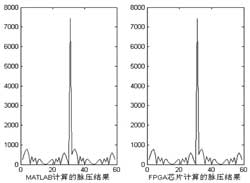

為解決雷達探測能力與距離分辨力之間的問題,在線性調頻信號脈沖壓縮的原理的基礎上,利用MATLAB軟件對數字脈沖壓縮算法進行仿真,給出一種基于FPGA分布式算法的

2010-12-24 16:10:59 37

37 FPGA的多路可控脈沖延遲系統設計

采用數字方法和模擬方法設計了一種最大分辨率為0.15 ns級的多路脈沖延遲系統,可以實現對連續脈沖信號的高分辨

2009-03-29 15:09:48 2234

2234

摘要:采用XILINX公司的SpartanII系列FPGA芯片設計了一種基于數字移相技術的高精度脈寬測量系統,同時給出了系統的仿真結果和精度分析。與通常的脈沖計

2009-06-20 14:59:56 1693

1693

基于FPGA雷達成像方位脈沖壓縮系統的設計

合成孔徑雷達成像算法中較為成熟和應用廣泛的算法主要有距離-多普勒(R-D)算法和線性調頻變標(CS)算法。R-D算法復雜度相

2009-12-02 11:44:10 1168

1168

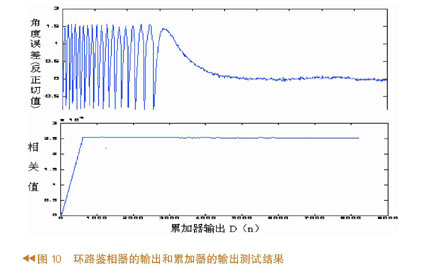

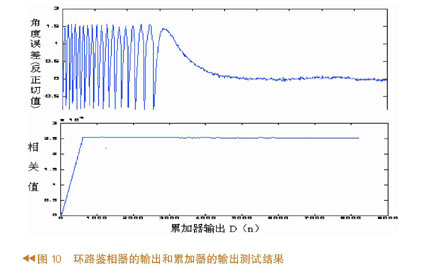

直擴導航系統中數字科思塔斯環的FPGA設計與實現

引言

擴頻接收機載波的同步包括捕獲和跟蹤兩個過程,載波捕獲即多普勒頻移的粗略估計通常包含在偽

2010-03-01 09:11:45 1060

1060

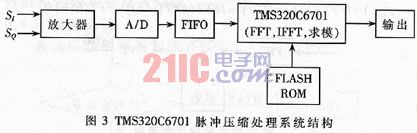

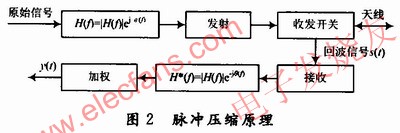

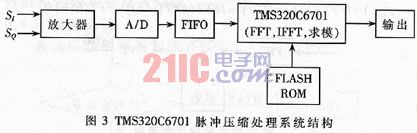

本文以TI公司的高性能的TMS320C6701浮點DSP芯片作為實現數字脈沖壓縮的核心器件,實現了線性調頻信號的頻域數字脈沖壓縮。

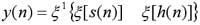

1 數字脈沖壓縮原理

數

2010-07-02 09:47:37 2878

2878

脈沖壓縮技術是指對雷達發射的寬脈沖信號進行調制(如線性調頻、非線性調頻、相位編碼),并在接收端對回波寬脈沖信號進行脈沖壓縮處理后得到窄脈沖的實現過程。脈沖壓縮有效

2010-07-19 09:37:01 1064

1064

本文主要介紹了一種利用FPGA IP核設計線性調頻信號脈沖壓縮的方法,通過各種仿真與實際測試表明脈沖壓縮結果正確。這種基于IP核的模塊化設計方法非常靈活,參數的設置和修改方便

2011-06-29 10:40:20 7309

7309

本設計開發出了一套基于雙FPGA+ARM架構的高速計算機屏幕圖像壓縮系統。系統通過對圖像壓縮系統任務的劃分,利用FPGA的并行計算能力和靈活的編程方式,完成圖像壓縮算法。

2011-08-22 11:44:31 2039

2039

用大多數FPGA都可以實現一個數字UWB(超寬帶)脈沖發生器。本設計可以創建一個兩倍于FPGA時鐘頻率的脈沖信號(

2011-09-06 11:59:48 5280

5280

針對一種新型的寬脈沖信號二相碼碼內線性調頻信號,分析了其數學表達式及其回波形成原理,并介紹了一種二相碼碼內線性調頻信號地雜波模擬器的系統實現。

2011-09-07 18:58:11 46

46 基于FPGA的靜止圖像壓縮系統的研究-JPEG編碼器的設計電力電子與電力傳動數字圖像在人們生活中的應用越來越廣泛,由于原始圖像數據量比較大,因此數字圖非常重要。

2011-11-01 18:17:55 65

65 本設計名為CDIC(基于Camera Link接口的圖像壓縮解壓縮)系統,應用了Altera公司的StratixTMII系列FPGA EP2S30F484I5芯片和基于Camera Link接口的數碼相機CV-A10CL,設計實現了對高分辨率黑白數字圖

2011-11-10 15:04:47 41

41 本文基于快速傅里葉IP核可復用和重配置的特點,實現一種頻域的FPGA數字脈壓處理器,能夠完成正交輸入的可變點LFM信號脈沖壓縮,具有設計靈活,調試方便,可擴展性強的特點。

2012-10-15 17:20:46 2738

2738

高性能的數據壓縮可以有效的減少數據對存儲空間和通信帶寬的要求,降低通信成本。為解決圖像數據的高壓縮性能問題,本文提出了基于JPEG2000標準的數據壓縮系統的FPGA實現方案。相

2013-04-16 10:39:07 46

46 本書比較全面地闡述了fpga在數字信號處理中的應用問題。本書共分8章,主要內容包括典型fpga器件的介紹、vhdl硬件描述語言、fpga設計中常用軟件簡介、用fpga實現數字信號處理的數據規劃、多種

2015-12-23 11:07:46 44

44 Xilinx FPGA工程例子源碼:VHDL實現對圖像的采集和壓縮

2016-06-07 14:54:57 6

6 Xilinx FPGA工程例子源碼:用FPGA實現數字鎖相環

2016-06-07 15:07:45 37

37 機載圖像無損近無損壓縮方案及其FPGA實現

2016-08-29 15:02:03 5

5 一種圖像動態范圍壓縮算法及其FPGA實現,感興趣的小伙伴們可以看一看。

2016-09-14 17:17:07 5

5 空間圖像CCSDS壓縮算法研究與FPGA實現,感興趣小伙伴們可以瞧一瞧。

2016-09-18 14:57:42 16

16 空間太陽望遠鏡FPGA星載圖像壓縮模塊的設計與實現

2016-09-17 07:37:00 23

23 中頻脈沖壓縮信號數字化直接產生技術研究

2017-01-10 21:35:22 17

17 噪聲干擾對線性調頻脈沖壓縮濾波器的干擾效果分析

2017-01-10 21:35:20 6

6 用高速DSP在頻域上實現LFM信號的實時脈沖壓縮

2017-01-10 21:35:20 6

6 一類新的脈沖壓縮信號的旁瓣抑制,下來看看。

2017-01-10 21:35:20 11

11 壓縮比1201的線性調頻脈沖壓縮系統,下來看看

2017-01-10 21:35:20 11

11 脈沖壓縮在超寬帶雷達中的應用,可以下來看看

2017-01-22 21:15:50 11

11 針對網內采用了旁瓣匿影和旁瓣對消技術的脈沖壓縮雷達,采用卷積噪聲對該種雷達進行干擾。結合公式推導及仿真實驗,驗證了該噪聲的假目標特性。同時得出了該噪聲在雷達接收機處所能獲得的匹配增益計算公式,在信號

2017-11-07 09:46:41 0

0 介紹了基于Zynq平臺實現的JPEG圖像壓縮系該系統利用Zynq片上AXI總線實現了ARM與FPGA核間高吞吐率的數據交互操作,并結合了ARM和FPGA在嵌入式系統開發中各自的優勢,對軟硬件功能

2017-11-17 14:41:50 6811

6811

即實現空時二維信號處理。實現了自適應副瓣相消,4路脈沖壓縮與MTI/MTD,副瓣匿影和差波束測角等算法,可以完成對目標距離,方位偏差量的測算,滿足系統需求。

2017-12-11 02:21:07 1881

1881

在數字信號處理系統中,數據表示格式可分為定點制、浮點制和塊浮點制,它們在實現時對系統資源的要求不同,工作速度也不同,有著不同的適用范圍。定點表示法使用最多,簡單且速度快,但動態范圍有限,需要用合適

2018-08-26 09:40:52 1032

1032

脈沖壓縮技術是指對雷達發射的寬脈沖信號進行調制(如線性調頻、非線性調頻、相位編碼),并在接收端對回波寬脈沖信號進行脈沖壓縮處理后得到窄脈沖的實現過程。脈沖壓縮有效地解決了雷達作用距離與距離分辨率之間的矛盾,可以在保證雷達在一定作用距離下提高距離分辨率。

2018-11-28 09:18:00 3561

3561

、功耗與實時性要求都很高的實時SAR成像系統,其應用十分廣泛。在整個有距離-多普勒(R-D)算法中方位脈沖壓縮系統是設計的關鍵。隨著FPGA芯片突飛猛進的發展,實時雷達成像方位脈沖壓縮系統在FPGA上實現變成了可能。

2018-12-30 11:10:00 3331

3331

對一種新型的寬脈沖信號一一二相碼碼內線性 調頻信號,分析了其數學表達式及其回波形成原理,并介紹了一種二相碼碼內線性調頻信號地雜波模擬器的系統實現。

2019-07-26 17:06:00 7

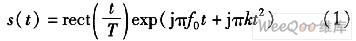

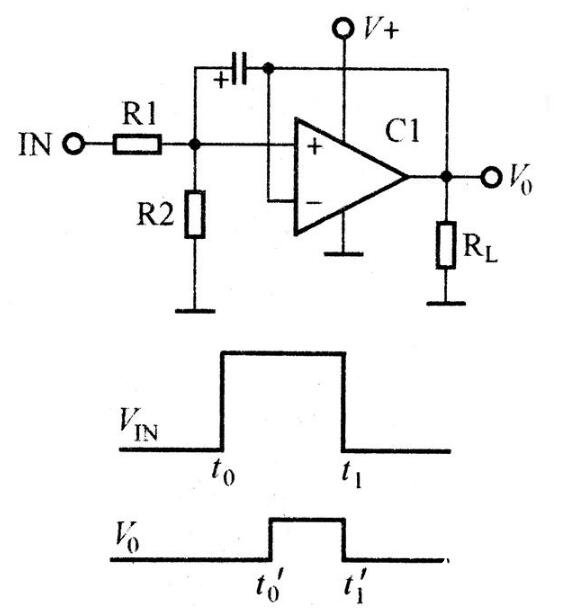

7 同時,由于C1與R1對信號的積分延時,所以,輸出脈沖與輸入脈沖相比,幅度和寬度都被壓縮了。

2020-05-02 17:00:00 2067

2067

本文檔的主要內容詳細介紹的是怎么樣才能使用FPGA實現數字系統內容包括了:FPGA簡介,為什么采用FPGA,開發平臺和設計工具,HDL(硬件描述語言),FPGA的設計原則,系統設計開發流程。

2020-08-11 15:29:00 9

9 在科學研究、通信和一些自動控制中,經常需要精確定時的連續脈沖信號,用于產生測試信號或控制用的時序。脈沖延遲的基本方法可分為數字方法和模擬方法。數字方法采用計數器或存儲器實現延遲控制,其缺點是無法滿足

2020-08-11 17:36:46 1060

1060

近日,中科院上海光機所成功制備出超大口徑(1620mmx1070mm)的無拼縫脈沖壓縮光柵,該口徑面積是目前國際已知最大同類光柵元件2.9倍。

2023-11-20 10:08:57 311

311

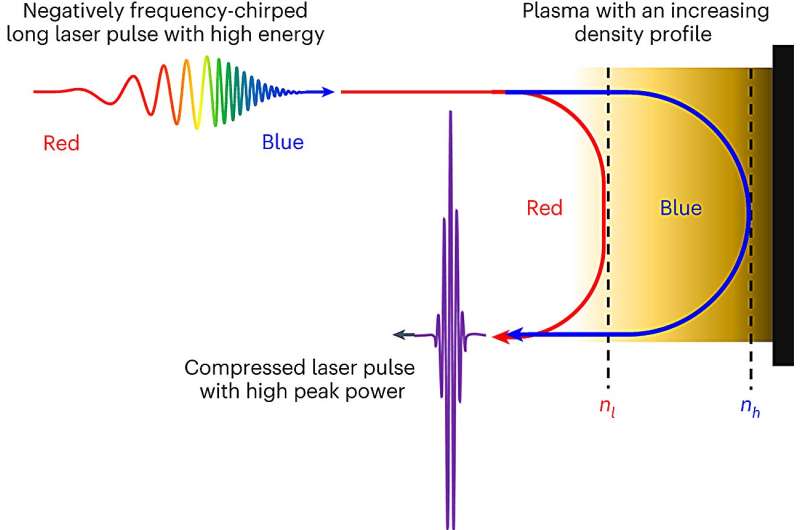

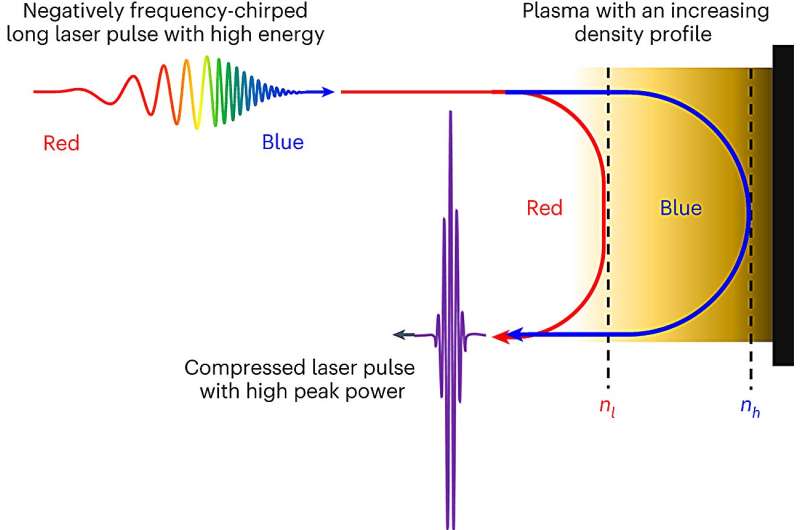

中提取粒子并研究物質的性質。為了實現這一目標,三個小組共同制作了一種非常特殊的鏡子——這種鏡子不僅能反射光脈沖,還能及時將光脈沖壓縮兩百倍以上,并有可能進一步壓縮。 斯特拉斯克萊德大學、UNIST和GIST的研究小組提出一個簡

2023-12-07 06:32:51 196

196

相位編碼信號的相位調制函數是離散的有限狀態,屬于“離散型“編碼脈沖壓縮信號。

在相位編碼中,二相編碼信號是常用的脈壓信號形式之一。

將寬脈沖分為許多短的等寬度子脈沖,每個子脈沖以兩種相位調制,其調制的順序由指定的編碼序列決定。

2024-02-20 10:57:30 353

353

電子發燒友App

電子發燒友App

評論