MAX11359A智能數(shù)據(jù)采集系統(tǒng)(DAS)基于16位、Σ-Δ模數(shù)轉(zhuǎn)換器(ADC),系統(tǒng)支持的功能使其適用于基于微處理器(μP)的系統(tǒng)。

2012-10-17 14:19:47 997

997

無(wú)關(guān)Max+plusⅡ系統(tǒng)的核心Complier支持Altera公司的FLEX10K、FLEX8000、FLEX6000、MAX9000、MAX7000、MAX5000和Classic可編程邏輯器件

2009-10-09 17:14:29

請(qǐng)大家?guī)兔Γ蚁肜肈AQ編程數(shù)據(jù)采集系統(tǒng),并且利用數(shù)據(jù)庫(kù)存儲(chǔ)數(shù)據(jù),請(qǐng)大家?guī)兔Γl(shuí)有好的數(shù)據(jù)采集的實(shí)例請(qǐng)發(fā)一下編程vi至1538568180@qq.com。謝謝!

2015-03-13 20:23:14

一、緒論(一)、1、“數(shù)據(jù)采集”是指什么?將溫度、壓力、流量、位移等模擬量經(jīng)測(cè)量轉(zhuǎn)換電路輸出電量后再采集轉(zhuǎn)換成數(shù)字量后,再由PC 機(jī)進(jìn)行存儲(chǔ)、處理、顯示或打印的過(guò)程。2、數(shù)據(jù)采集系統(tǒng)的組成?由數(shù)據(jù)

2021-09-10 07:53:28

數(shù)據(jù)采集與傳輸系統(tǒng)一、設(shè)計(jì)任務(wù)與要求1、設(shè)計(jì)任務(wù)設(shè)計(jì)制作一個(gè)用于8路模擬信號(hào)采集與單向傳輸系統(tǒng)。系統(tǒng)方框圖參見下圖。基于羽毛球拍的數(shù)據(jù)采集技術(shù)探討,專家答疑

2009-03-20 10:06:01

;2.可以在MAX當(dāng)中通過(guò)配置無(wú)需編程實(shí)現(xiàn)數(shù)據(jù)采集功能3.在MAX中創(chuàng)建的數(shù)據(jù)采集任務(wù)可以自動(dòng)導(dǎo)入LabView,并生成LabView代碼; 二、如何獲取MAX軟件:NI的數(shù)據(jù)采集硬件產(chǎn)品對(duì)應(yīng)的驅(qū)動(dòng)

2019-04-19 09:40:04

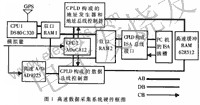

不同的需要進(jìn)行現(xiàn)場(chǎng)編程,具有通用性好、價(jià)格相對(duì)便宜,易于系統(tǒng)調(diào)試,升級(jí)等特點(diǎn)。系統(tǒng)中 CPLD選擇的型號(hào)是 ALTERA公司的MAX7000系列低功耗芯片EPM7128A。片外大容量 SRAM是DSP

2019-06-20 07:31:29

不同的需要進(jìn)行現(xiàn)場(chǎng)編程,具有通用性好、價(jià)格相對(duì)便宜,易于系統(tǒng)調(diào)試,升級(jí)等特點(diǎn)。系統(tǒng)中 CPLD選擇的型號(hào)是 ALTERA公司的MAX7000系列低功耗芯片EPM7128A。片外大容量 SRAM是DSP

2019-07-26 07:16:41

如果用國(guó)產(chǎn)數(shù)據(jù)采集卡做數(shù)據(jù)采集,在用labVIEW編程是能使用DAQmx嗎?能在MAX中自動(dòng)生成簡(jiǎn)單數(shù)據(jù)采集代碼嗎?

2017-05-30 14:44:56

單芯片12位數(shù)據(jù)采集系統(tǒng)

2023-03-28 18:28:42

單芯片12位數(shù)據(jù)采集系統(tǒng)

2023-03-23 07:59:40

本帖最后由 reachland 于 2014-12-24 15:50 編輯

使用LabVIEW進(jìn)行數(shù)據(jù)采集,編程時(shí)可以創(chuàng)建任務(wù),比如說(shuō)現(xiàn)在創(chuàng)建0通道的一個(gè)模擬電壓的連續(xù)采集,但是使用MAX也可以創(chuàng)建一個(gè)任務(wù),這兩個(gè)任務(wù)會(huì)矛盾嗎?還是在實(shí)際使用中這兩個(gè)都需要進(jìn)行設(shè)置?

2013-06-12 10:57:36

、采用查找表的FPGA的工作原理第三節(jié) Altera系列CPLD介紹一、MAX7000系列器件簡(jiǎn)介二、MAX7000系列器件的結(jié)構(gòu)三、MAX7000系列器件功能描述第四節(jié) Xilinx系列CPLD介紹······下載鏈接:`

2018-03-30 15:07:50

大家好,小弟新手求助關(guān)于數(shù)據(jù)采集的問(wèn)題,現(xiàn)在有兩路信號(hào),每路信號(hào)有6000-7000hz,現(xiàn)在想用NI USB6211采集卡進(jìn)行采集和數(shù)據(jù)處理,但是設(shè)置的時(shí)候觀察采樣的波形總是有點(diǎn)失真,采樣率設(shè)置

2014-06-29 21:11:15

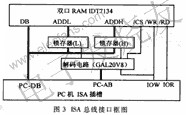

分享一款不錯(cuò)的基于CPLD和ISA總線的數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)

2021-05-06 09:53:44

在max7000系列中, 只允許有兩個(gè)輸出使能信號(hào), 可在設(shè)計(jì)中卻存在三個(gè), 每次編譯時(shí)出現(xiàn)“device need too many [3/2] output enable signal”. 如果不更換器件(使用的是max7064lc68). 如何解決這個(gè)問(wèn)題?

2019-09-18 05:55:29

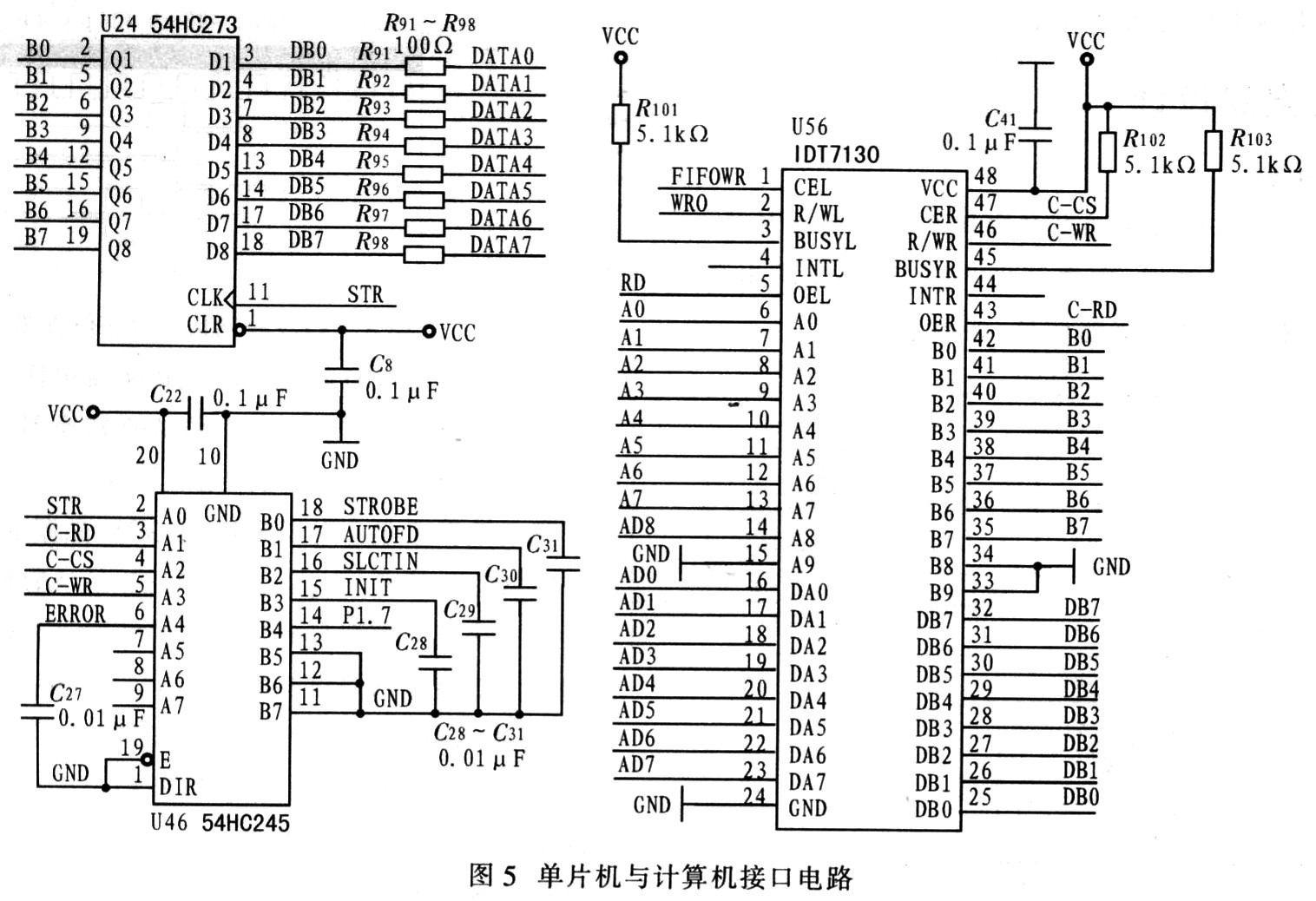

/模轉(zhuǎn)換器DAC0832構(gòu)成一個(gè)數(shù)據(jù)采集系統(tǒng),并用CPLD/FPGA實(shí)現(xiàn)數(shù)據(jù)采樣、D/A轉(zhuǎn)換輸出、有關(guān)數(shù)據(jù)顯示的控制,單片機(jī)完成對(duì)A/D轉(zhuǎn)換數(shù)據(jù)運(yùn)算。電路如圖1所示。系統(tǒng)功能如下:系統(tǒng)按一定速率采集輸入

2018-12-10 10:18:34

摘要:介紹了用ALTERA公司MAX7000系列CPLD芯片實(shí)現(xiàn)單片機(jī)與PC104ISA總線接口之間的關(guān)行通信。給出了系統(tǒng)設(shè)計(jì)方法及程序源代碼。關(guān)鍵詞:CPLD ISA總線 并行通信 CPLD

2019-06-20 05:00:02

基于MAX125芯片和串行總線實(shí)現(xiàn)同步數(shù)據(jù)采集系統(tǒng)的設(shè)計(jì)

2021-01-04 06:17:27

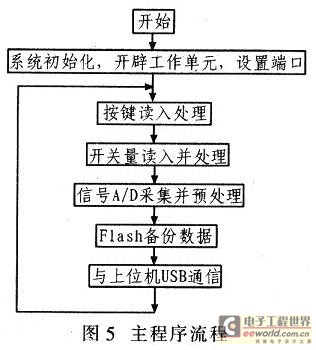

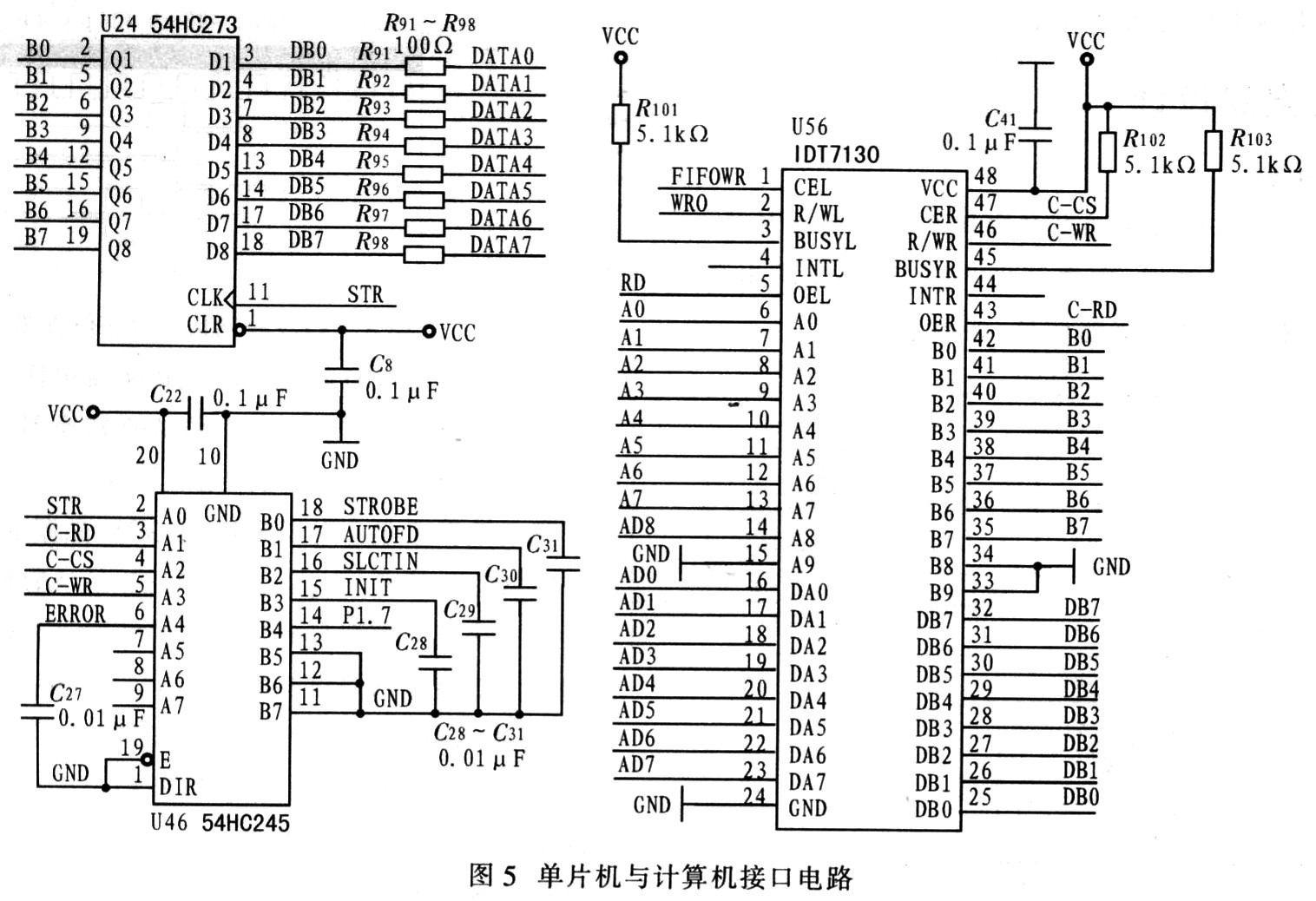

接口,它使電路工作在更加平穩(wěn)、簡(jiǎn)潔而易丁控制,同時(shí)也提高了ARM的工作效率。為了提高通信速度,這里采用通用申行總線(USB)技術(shù)米與PC進(jìn)行通信。ARM是用來(lái)控制主處理器的數(shù)據(jù)采集,數(shù)據(jù)的計(jì)算和數(shù)據(jù)傳輸。結(jié)果證明,整個(gè)系統(tǒng)能高效運(yùn)作。該系統(tǒng)可應(yīng)用于高速數(shù)據(jù)采集及多路模擬信號(hào)的工作環(huán)境下。

2023-09-26 07:41:28

本帖最后由 mr.pengyongche 于 2013-4-30 03:26 編輯

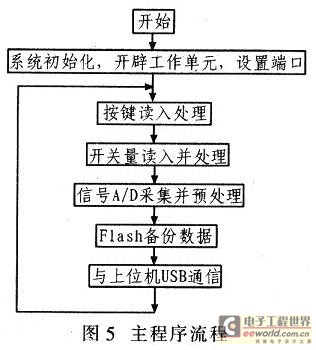

1 引言 數(shù)據(jù)采集系統(tǒng)是通信與信息技術(shù)領(lǐng)域中重要的功能模塊,應(yīng)用廣泛。而傳統(tǒng)的數(shù)據(jù)采集系統(tǒng)大多以單片機(jī)或中規(guī)模數(shù)字電路為核心,其模數(shù)轉(zhuǎn)換器(A/D轉(zhuǎn)換

2011-12-14 10:24:47

,電力系統(tǒng)自動(dòng)化程度也日益提高,通過(guò)數(shù)字信號(hào)處理技術(shù)和現(xiàn)場(chǎng)總線技術(shù)的應(yīng)用提高了電力系統(tǒng)的可靠性和可維護(hù)性[2]。本文設(shè)計(jì)的數(shù)據(jù)采集系統(tǒng),選用TI公司推出的C2XXX系列的32位定點(diǎn)DSP芯片

2009-12-08 10:28:19

基于FPGA的數(shù)據(jù)采集系統(tǒng)IEE ... 介紹了數(shù)據(jù)采集系統(tǒng)中以FPGA為處理核心、采用TI公司接口芯片的IEEE1394接口設(shè)計(jì),給出了系統(tǒng)硬件設(shè)計(jì)和FPGA邏輯設(shè)計(jì),討論了IEEE1394總線

2012-08-11 15:43:47

基于GPRS遠(yuǎn)程數(shù)據(jù)采集系統(tǒng)根據(jù)近年來(lái) GSM/GPRS 通信技術(shù)發(fā)展的趨勢(shì),本文提出并設(shè)計(jì)了基于GPRS 網(wǎng)絡(luò)通信的遠(yuǎn)程數(shù)據(jù)采集系統(tǒng),主要論述了采用AT89C52 單片機(jī)控制GPRS 模塊(G20

2009-12-08 09:57:10

,設(shè)計(jì)了一種基于USB(通用串行總線)接口的USAT基帶數(shù)據(jù)采集系統(tǒng),該系統(tǒng)通過(guò)對(duì)USB接口控制邏輯的合理設(shè)計(jì)和芯片內(nèi)部FIFO的有效運(yùn)用,充分應(yīng)用了CPLD(復(fù)雜可編程邏輯器件)的靈活性,僅采用單片

2018-12-05 10:16:02

,分辨率等等。基于單片機(jī)的數(shù)據(jù)采集系統(tǒng)數(shù)據(jù)處理能力比較低,已經(jīng)無(wú)法達(dá)到某些要求。科技的不斷創(chuàng)新及半導(dǎo)體工業(yè)的發(fā)展使得我們將可編程邏輯器件的技術(shù)應(yīng)用到數(shù)據(jù)采集系統(tǒng)的研究上。同時(shí)利用CPLD 強(qiáng)大的數(shù)字

2021-07-20 06:23:22

該文檔為基于FPGA的多路模擬數(shù)據(jù)采集接口設(shè)計(jì)講解文檔,介紹一種基于 8,RQ 的多路模擬數(shù)據(jù)采集接口的設(shè)計(jì)方案。該方案使用Max1281 作為模數(shù)轉(zhuǎn)換芯片,在 APA150 FPGA 中設(shè)計(jì)和實(shí)現(xiàn)了相關(guān)的接口控制、配置和數(shù)據(jù)存儲(chǔ)模塊;給出了系統(tǒng)設(shè)計(jì)框圖、FPGA開發(fā)要點(diǎn)和仿真波形。

2018-09-21 14:37:00

MAX115的工作原理MAX115的基本操作如何利用MAX115的電網(wǎng)數(shù)據(jù)采集和模/數(shù)轉(zhuǎn)換對(duì)已使用多年的系統(tǒng)進(jìn)行改進(jìn)?

2021-04-08 06:35:39

如果沒有硬件和熱電偶,如何用MAX虛擬創(chuàng)建信號(hào)源和數(shù)據(jù)采集卡實(shí)現(xiàn)數(shù)據(jù)采集的溫度任務(wù)?謝謝

2015-05-27 16:30:56

本文設(shè)計(jì)一種基于CPLD的數(shù)據(jù)采集控制板。它能實(shí)現(xiàn)信號(hào)采集與控制、信號(hào)處理、通訊及輸出控制等功能。

2021-05-08 07:33:42

設(shè)計(jì)的基于CPLD與單片機(jī)的高速數(shù)據(jù)采集系統(tǒng)在QUARTUS II軟件中進(jìn)行了仿真并達(dá)到了預(yù)期的控制邏輯。

2021-04-13 06:07:06

MAX197芯片具有哪些特點(diǎn)及性能?如何采用高精度模數(shù)轉(zhuǎn)換芯片MAX197和51系列單片機(jī)AT89S52設(shè)計(jì)高精度數(shù)據(jù)采集系統(tǒng)?

2021-04-12 06:47:57

測(cè)井數(shù)據(jù)采集控制系統(tǒng)原理是什么?由哪些構(gòu)成?數(shù)據(jù)采集有哪些方案設(shè)計(jì)?如何采用數(shù)據(jù)采集卡設(shè)計(jì)測(cè)井數(shù)據(jù)采集控制系統(tǒng)?

2021-04-13 06:25:12

本文介紹了一種基于AD、CPLD、串行閃存來(lái)實(shí)現(xiàn)的小體積的數(shù)據(jù)采集系統(tǒng)。與其他數(shù)據(jù)采集系統(tǒng)相比,該系統(tǒng)體積小,存儲(chǔ)器便于控制,易于升級(jí)存儲(chǔ)器的容量,能夠滿足一般的信號(hào)采集。不足是系統(tǒng)的采樣頻率不夠高,只能達(dá)到250kHz/S,不適于高頻信號(hào)的采集。

2021-04-07 06:48:52

的通用性比較差。另一方面,早期數(shù)據(jù)采集系統(tǒng)多是基于復(fù)雜可編程邏輯器件(CPLD)設(shè)計(jì)的,數(shù)據(jù)的采樣速度和精度都不是很高。

2019-09-23 08:32:23

,具有通用性好、價(jià)格相對(duì)便宜,易于系統(tǒng)調(diào)試,升級(jí)等特點(diǎn)。系統(tǒng)中 CPLD選擇的型號(hào)是ALTERA公司的MAX7000系列低功耗芯片EPM7128A。片外大容量 SRAM是DSP與 CPLD的聯(lián)系橋梁

2019-09-18 08:31:58

高速數(shù)據(jù)采集系統(tǒng)的硬件結(jié)構(gòu)MAX7000系列CPLD及其開發(fā)平臺(tái)介紹CPLD在高速數(shù)據(jù)采集系統(tǒng)中的應(yīng)用

2021-04-30 06:43:12

給CPLD編程,使用MAX7000系列芯片,需要延時(shí)功能,延時(shí)時(shí)間1秒到幾分鐘,并可以外部進(jìn)行調(diào)整延時(shí)時(shí)間,不知怎么處理,請(qǐng)教高手幫助!多謝!

2010-01-16 10:59:27

近年來(lái),隨著可編程邏輯器件(CPLD/FPGA)的迅猛發(fā)展,可編程邏輯器件在數(shù)據(jù)采集、邏輯接口設(shè)計(jì)、電平接口轉(zhuǎn)換和高性能數(shù)字信號(hào)處理等領(lǐng)域取得越來(lái)越廣泛的應(yīng)用。CPLD/FPGAD不僅可以解決電子系統(tǒng)

2020-03-05 06:20:45

數(shù)據(jù)采集系統(tǒng)是由哪些部分組成的?Blackfin及uClinux在數(shù)據(jù)采集系統(tǒng)中有哪些應(yīng)用?數(shù)據(jù)采集系統(tǒng)該如何去設(shè)計(jì)?

2021-04-26 06:20:04

基于AVR和CPLD的高速數(shù)據(jù)采集系統(tǒng)該怎樣去設(shè)計(jì)?

2021-04-29 06:59:21

采用PCI總線流水式高速數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)摘要:目前基于PCI總線的高速數(shù)據(jù)采集系統(tǒng),大多采用高速A/D,CPLD或FPGA,FIFO或雙端口RAM以及通用PCI接口來(lái)設(shè)計(jì),其通用性、靈活性差,不能

2009-10-30 15:09:49

高速數(shù)據(jù)采集系統(tǒng)的硬件結(jié)構(gòu)MAX7000系列CPLD及其開發(fā)平臺(tái)介紹CPLD在高速數(shù)據(jù)采集系統(tǒng)中的應(yīng)用

2021-04-08 06:11:56

max7000系列器件可編程邏輯的技術(shù)規(guī)范

2007-11-14 12:49:29 17

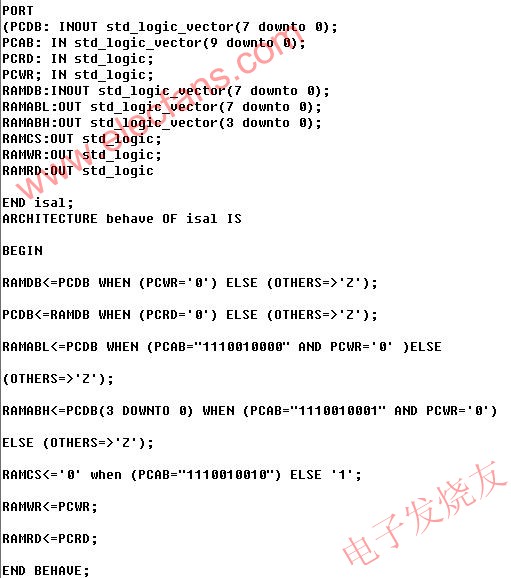

17 用ALTERA 公司MAX7000 系列CPLD 芯片實(shí)現(xiàn)單片機(jī)與PC104 ISA 總線接口之間的并行通信,給出系統(tǒng)設(shè)計(jì)方法及程序源代碼。包括通信軟件和AHDL 設(shè)計(jì)部分。

2009-04-14 17:36:07 29

29 用ALTERA 公司MAX7000 系列CPLD 芯片實(shí)現(xiàn)單片機(jī)與PC104 ISA 總線接口之間的并行通信,給出系統(tǒng)設(shè)計(jì)方法及程序源代碼。包括通信軟件和AHDL 設(shè)計(jì)部分。

2009-05-14 13:24:39 14

14 本文介紹了 MAX7000 系列CPLD 器件在DSP 接口電路中的應(yīng)用,重點(diǎn)介紹了TMS3202××系列DSP 和存儲(chǔ)器,LCD 接口的方法,并輔以VHDL 源程序的例子。關(guān)鍵詞:DSP;MAX7000;CPLD;可編程

2009-06-29 08:57:03 43

43 本文介紹了一種基于CPLD的溫度采集系統(tǒng)的設(shè)計(jì)方法,設(shè)計(jì)分為溫度采集和LED顯示兩個(gè)功能模塊。與常用溫度采集系統(tǒng)相比,本設(shè)計(jì)采用高精度數(shù)字溫度傳感器MAX6627與CPLD控制芯片E

2009-07-07 13:44:56 22

22 本文介紹的數(shù)據(jù)采集系統(tǒng)應(yīng)用低功耗、14 位逐次逼近以及兼容于I2C 串行接口的模/數(shù)轉(zhuǎn)換器MAX1069,可方便的與微控制器及其外圍設(shè)備進(jìn)行連接。通過(guò)自行設(shè)計(jì)的數(shù)據(jù)采集系統(tǒng),本文

2009-07-11 08:27:10 11

11 設(shè)計(jì)了以CPLD 為核心處理芯片的多路數(shù)據(jù)采集系統(tǒng),按照正確的時(shí)序直接控制AD676和雙端口RAM的工作, 所有這些功能都采用VHDL語(yǔ)言進(jìn)行描述。關(guān)鍵詞:CPLD, AD676, VHDL語(yǔ)言, 雙端口R

2009-09-01 10:26:41 25

25 本文介紹了一種利用CPLD 器件作控制核心,基于SCSI 硬盤的雷達(dá)高度表高速大容量數(shù)據(jù)采集存儲(chǔ)系統(tǒng),分析了系統(tǒng)組成和設(shè)計(jì)思想,著重對(duì)CPLD 實(shí)現(xiàn)的功能做了介紹并給出了代表信號(hào)

2009-09-18 11:09:30 11

11 本文針對(duì)新型匝間耐壓測(cè)試儀中需要高速采集數(shù)據(jù)的問(wèn)題提出了一種結(jié)合CPLD 與單片機(jī)的高速數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)方案。CPLD 產(chǎn)生A/D 芯片的控制時(shí)序以及SRAM 的讀寫控制時(shí)序,單片機(jī)輸

2009-12-23 14:59:57 88

88 基于CPLD 的雷達(dá)高度表高速大容量數(shù)據(jù)采集存儲(chǔ)系統(tǒng)設(shè)計(jì)作者:李貴新 袁嗣杰 轉(zhuǎn)貼自:微計(jì)算機(jī)信息摘 要:本文介紹了一種利用CPLD 器件作控制核心,基于SCSI 硬盤的雷達(dá)高

2010-01-27 14:18:26 22

22 基于MAX3420的實(shí)時(shí)數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)

針對(duì)TMSC3206000數(shù)字信號(hào)處理器的特點(diǎn),設(shè)計(jì)了基于DSP和MAX3420的實(shí)時(shí)數(shù)據(jù)采集系統(tǒng).

2010-06-11 17:26:23 39

39 Altera的 MAX 7000 CPLDs®基于先進(jìn)的多陣列矩陣(MAX)架構(gòu),為大量應(yīng)用提供了世界級(jí)的高性能解決方案 。基于電可擦除可編程只讀存儲(chǔ)器(EEPROM)的MAX7000產(chǎn)品采用先進(jìn)的CMOS工藝制造

2010-11-03 16:32:45 149

149 本文對(duì)激光掃描車身坐標(biāo)測(cè)量系統(tǒng)的數(shù)據(jù)采集部分進(jìn)行了深入研究,設(shè)計(jì)了基于“AVR+FIFO+CPLD”的數(shù)據(jù)采集及處理模塊;解決了當(dāng)多路信號(hào)有數(shù)據(jù)同時(shí)傳輸時(shí),如何將數(shù)據(jù)完整地寫入F

2010-11-22 14:51:10 24

24 摘要:用ALTERA公司MAX7000系列CPLD芯片實(shí)現(xiàn)單片機(jī)與PC104 ISA總線接口之間的并行通信,給出系統(tǒng)設(shè)計(jì)方法及程序源代碼。包括通信軟件和AHDL設(shè)計(jì)部分。CPLD(Complex Programmable Logi

2006-05-26 21:52:11 872

872

換體DMA高速數(shù)據(jù)采集電路的CPLD實(shí)現(xiàn)

介紹了換體DMA高速數(shù)據(jù)采集電路原理及其CPLD實(shí)現(xiàn)。用CPLD設(shè)計(jì)雙端口RAM緩存、控制譯碼、時(shí)序邏輯電路,很好地解決了電路元件所占體積

2009-03-28 15:09:18 666

666

CPLD在多路高速同步數(shù)據(jù)采集系統(tǒng)中的應(yīng)用

CPLD(Complex Programmable Logic Device,復(fù)雜可編程邏輯器件)是在傳統(tǒng)的PAL、GAL基礎(chǔ)上發(fā)展而來(lái)的,具有多種工作方式

2009-03-28 16:49:00 767

767

數(shù)據(jù)采集系統(tǒng)是通過(guò)采樣電路將輸入的模擬信號(hào)轉(zhuǎn)換成離散信號(hào),并送入CPU、MCU或DSP進(jìn)行處理。現(xiàn)在流行的基于PCI總線設(shè)計(jì)的采集卡是數(shù)據(jù)采集系統(tǒng)的主流,其優(yōu)點(diǎn)是可以利用PCI

2009-04-19 10:52:31 817

817

設(shè)計(jì)了以CPLD為核心處理芯片的多路數(shù)據(jù)采集系統(tǒng),整個(gè)數(shù)據(jù)采集系統(tǒng)可實(shí)現(xiàn)最大采集頻率為800kHz,通道數(shù)為48路的模擬信號(hào)的采集。系統(tǒng)中采用了TI公司最新推出的高速低功耗A/D

2009-05-05 20:04:02 1666

1666

介紹了一種基于CPLD(復(fù)雜可編程邏輯器件)和FIFO(先入先出存儲(chǔ)器)的多通道高速A/D數(shù)據(jù)采集系統(tǒng)的設(shè)計(jì)方法,并給出了這種數(shù)據(jù)采集方法的硬件原理電路和主要的軟件設(shè)計(jì)思路

2009-05-05 20:50:09 1651

1651

摘要:用ALTERA公司MAX7000系列CPLD芯片實(shí)現(xiàn)單片機(jī)與PC104 ISA總線接口之間的并行通信,給出系統(tǒng)設(shè)計(jì)方法及程序源代碼。包括通信軟件和AHDL設(shè)計(jì)部分。

關(guān)鍵詞:CPLD

2009-06-20 13:34:28 1116

1116

摘要: 采用VHDL語(yǔ)言和圖形輸入設(shè)計(jì)方法,給出了用CPLD在遠(yuǎn)程多路數(shù)據(jù)采集系統(tǒng)中實(shí)現(xiàn)地址譯碼、串口擴(kuò)展、模塊測(cè)試、模數(shù)轉(zhuǎn)換以及高位數(shù)據(jù)處理等功能的具體方

2009-06-20 14:52:11 525

525

摘要:介紹了換體DMA高速數(shù)據(jù)采集電路原理及其CPLD實(shí)現(xiàn)。用CPLD設(shè)計(jì)雙端口RAM緩存、控制譯碼、時(shí)序邏輯電路,很好地解決了電路元件所占體積大、電路復(fù)雜、不能實(shí)現(xiàn)在線

2009-06-20 15:12:07 878

878

高速數(shù)據(jù)采集系統(tǒng)中精確時(shí)標(biāo)的CPLD實(shí)現(xiàn)方法

本文介紹一種利用復(fù)雜可編程邏輯器件給高速數(shù)據(jù)采集系統(tǒng)中的采集數(shù)據(jù)貼上精確時(shí)間標(biāo)簽的方法,并

2009-07-20 12:42:23 609

609 基于ADS8364的數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)

開發(fā)了基于DSP和ADS8364的數(shù)據(jù)采集處理系統(tǒng)。該系統(tǒng)主要由信號(hào)調(diào)理模塊、A/D轉(zhuǎn)換模塊、DSP處理器模塊、CPLD邏輯控制模塊、Flash存儲(chǔ)器模

2009-09-19 09:30:20 1487

1487

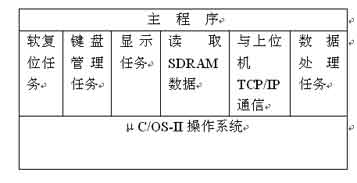

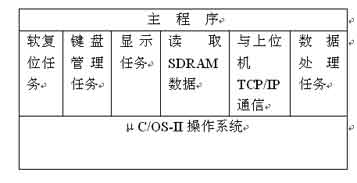

基于CPLD和嵌入式系統(tǒng)的高速數(shù)據(jù)采集系統(tǒng)的設(shè)計(jì)與實(shí)現(xiàn)

介紹一種基于CPLD和嵌入式系統(tǒng)的高速數(shù)據(jù)采集系統(tǒng),并詳細(xì)闡述了系統(tǒng)的結(jié)構(gòu)和軟硬件的實(shí)

2009-10-15 23:46:59 616

616

基于DSP和MAX1420的高速數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)

1 引言

數(shù)據(jù)采集系統(tǒng)是通信與信息技術(shù)領(lǐng)域中重要的功能模塊,應(yīng)用廣泛。

2009-12-21 17:07:15 906

906

基于單片機(jī)和CPLD實(shí)時(shí)數(shù)據(jù)采集顯示系統(tǒng)設(shè)計(jì)

1 引言 數(shù)據(jù)采集是分析模擬信號(hào)量數(shù)據(jù)的有效方法。而實(shí)時(shí)顯示數(shù)據(jù)是自動(dòng)化檢測(cè)系統(tǒng)的現(xiàn)實(shí)需求。在測(cè)

2009-12-22 17:31:02 1739

1739

基于CPLD/FPGA高速數(shù)據(jù)采集系統(tǒng)的設(shè)計(jì)

0 引 言 傳統(tǒng)的數(shù)據(jù)采集系統(tǒng)一般采用單片機(jī),系統(tǒng)大多通過(guò)PCI總線完成數(shù)據(jù)的傳輸。其缺點(diǎn)是數(shù)學(xué)運(yùn)算能力差;

2010-01-27 09:35:01 508

508

為實(shí)現(xiàn)尺寸較大、內(nèi)部結(jié)構(gòu)較為復(fù)雜的星載電子設(shè)備的多余物自動(dòng)檢測(cè),設(shè)計(jì)了以EZ-USB FX2和CPLD芯片為核心器件的數(shù)據(jù)采集卡,實(shí)現(xiàn)了四通道的同步數(shù)據(jù)采集和傳輸。此系統(tǒng)包括數(shù)據(jù)采

2011-03-21 10:54:38 0

0 CPLD在高速數(shù)據(jù)采集系統(tǒng)中的應(yīng)用! 介紹了高速數(shù)據(jù)采集系統(tǒng)的整體框架分析了其中的通用部分CPLD系列產(chǎn)品的特點(diǎn)及其開發(fā)軟件.CPLD根據(jù)高速數(shù)據(jù)采集系統(tǒng)的需要VHDL語(yǔ)言的形式,介紹了由

2011-12-17 00:12:00 26

26 本文結(jié)合實(shí)際應(yīng)用需要,設(shè)計(jì)了基于復(fù)雜可編程邏輯器件(CPLD)的線陣CCD數(shù)據(jù)采集系統(tǒng)。著重介紹了數(shù)據(jù)采集的特點(diǎn)及該系統(tǒng)軟、硬件設(shè)計(jì)和最后的性能評(píng)價(jià)。

2012-05-14 09:53:41 1133

1133

本文設(shè)計(jì)了一種基于CPLD(復(fù)雜可編程邏輯器件)+FX2(單片機(jī)CY7C68013)的便攜式高速數(shù)據(jù)采集系統(tǒng),采用了數(shù)據(jù)流驅(qū)動(dòng)多模塊并行技術(shù)和USB2.0接口。實(shí)踐證明,該方案結(jié)構(gòu)簡(jiǎn)單,成本低廉

2012-05-25 09:53:19 1472

1472

本文提出了采用Xilinx公司生產(chǎn)的CPLD來(lái)對(duì)多通道旋轉(zhuǎn)編碼器進(jìn)行數(shù)據(jù)采集的方法,著重介紹了系統(tǒng)的軟硬件設(shè)計(jì)和驅(qū)動(dòng)程序開發(fā),以及實(shí)際應(yīng)用情況,得出了用CPLD技術(shù)為多通道編碼器

2012-07-11 10:36:31 1224

1224 NBP3 Altera MAX7000 MAX3000 PLCC Rev1.00

2016-02-17 15:07:18 0

0 基于CPLD高速數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)_鮮果

2017-03-19 11:45:23 3

3 本文檔的主要內(nèi)容詳細(xì)介紹的是MAX7000可編程邏輯器件系列數(shù)據(jù)手冊(cè)免費(fèi)下載。MAX 7000系列高密度、高性能PLD基于Altera的第二代MAX架構(gòu)。采用先進(jìn)的CMOS技術(shù)制造,基于EEPROM

2018-12-20 08:00:00 23

23 為了提高數(shù)據(jù)采集卡的速度,同時(shí)降低成本,設(shè)計(jì)一種并行數(shù)據(jù)采集系統(tǒng),要求并行采集速度大于10 Mb/s。整個(gè)系統(tǒng)由AVR與CPLD控制實(shí)現(xiàn),通過(guò)MAXl308完成模數(shù)轉(zhuǎn)換,并設(shè)計(jì)搭建了其外圍電路。采用

2020-07-20 17:17:02 11

11 時(shí)域工作站MAX70000系列是以數(shù)據(jù)采集分析系統(tǒng)和任意信號(hào)合成為基礎(chǔ)的軟件可定義測(cè)量?jī)x器。搭載“鳳凰座”芯片組,具有四個(gè)4GHz模擬帶寬的接收通道和四個(gè)5GHz模擬帶寬的發(fā)射通道,并可依據(jù)客戶

2021-12-11 09:49:08 1109

1109 CPLD的MAX系列器件庫(kù)max-13.0.1.232

2022-12-21 17:26:11 4

4

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論