Q1:FPGA設計與DSP設計相比,最大的不同之處在哪里?

A1:這個問題要從多個角度看。它們都用于某個功能的硬件電路實現,但是它們的側重點有所不同。這里涵蓋的說一下。

1)內部資源

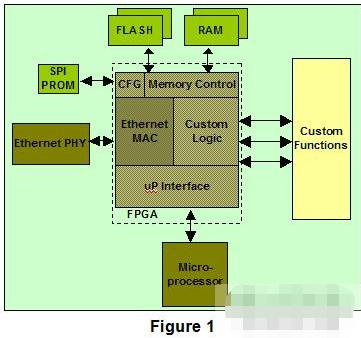

FPGA側重于設計具有某個功能的硬件電路,內部資源是VersaTiles(ActelFPGA)之類的微小單元,FPGA的內部單元初始在編程前都是使用的是HDL語言實現硬件電路的設計描述。FPGA內部的連線資源將這些功能模塊的內部和模塊之間的信號連接起來,構成較大的模塊。FPGA可以內部實現ALU,加法器,乘法器,累加器,FIFO,SRAM,DDRcontroller,FFT,HDLC,DMA,PWM等等數字電路,也就說我們要用其實現一個特定的或是通用的硬件功能一個或是多個模塊,這些模塊的各個細節都要要用HDL來描述設計實現。目前的FPGA都可以直接內嵌諸如ARM7,CoretexM1,Core8051等微處理器,用于FPGA的軟核的,也有的FPGA廠商將一些硬件模塊直接做到FPGA中,這些是FPGA內部的硬核。傳統的FPGA都是實現純數字電路的,業界只有Actel的FPGA實現了數模混合的PSC單芯片技術,真正的提升和擴大了FPGA的應用功能和領域。另外多數FPGA都有PLL,DLL之類的鎖相環,Slew可調,Actel的還內建了OSC,RTC,Powermanager之類的硬件單元,甚至Actel的Fusion系列還內建了600kbps的12bit的ADC以及MOSFETDriver之類模擬接口,內部有UserFlashMemeory,FlashROM等資源可以實現真正的PSC,Bootloader之類的功能。

DSP主要是算法處理,內部資源主要是乘法器,加法器之類的資源,有SPI接口,UART接口,接受一定的指令集,內部的資源基本上都是現成的,需要客戶的需要而重新配置,方便于客戶的使用,但是相對來講其功能是有局限性的,所以主要用于某些特定的領域。DSP也有內嵌的鎖相環,計數器,Baudrate發生器,有的DSP也有ADC模擬接口。

2)使用的編程語言

FPGA主要使用HDL,包括VHDl,Verilog,還有數模混合的描述語言Verilog-AMS等。DSP使用C,匯編語言編程。

3)功能角度

FPGA普遍用于實現數字電路模塊,基本上能實現所有的數字電路,傳統的數字功能模塊,以及客戶產品特定需求的數字處理模塊。FPGA的IO橋接種類繁多,不同種類的級別的FPGA支持的IO標準和協議都不盡相同,但是這些IO的驅動能力或是電壓都是可編程配置的。任何數字功能電路的實現,高速信號的處理,控制領域的信號處理,橋轉換協議的實現,Actel的Fusion還能用于電流/電壓檢測,溫度的檢測,MOSFETdriver,電源管理,其獨特的Flash工藝技術可以依靠電池供電工作,和掉電實時保存數據,超低功耗,多種工作模式(Static,Sleepmode),尤其IGLOO芯片的功能在Sleepmode下功耗只有5uW。這樣的功耗用于手機,GPS之類的移動手持設備中能發揮更大的功能應用。另外用FPGA實現ASIC的前期的設計驗證,FPGA實現DSP的功能,實現CPU的功能,MCU的功能,內存控制器,用于工業的PWM,SVPWM,Clarke,Park的正逆變換的實現,VGA控制,數據的編解碼,解復用,高達上Gbps的信號的處理,協議的轉換實現等等等等功能,都是DSP難以勝任的。

DSP內部有很多現成的硬件模塊和接口以及控制器,但是需要軟件編程設定,可以實現PWM控制,接口控制,UART接口,SPI接口等功能。但是由于受指令集的時鐘周期的限制,DSP不能處理太高的信號,至于說上Gbps的信號,LVDS之類的信號就很難以涉及了。所以相應的應用領域會有所限制。但是不同的領域客戶的設計方案不同,考慮的側重點不同,有些領域設計者也是愛好使用DSP的,諸如算法實現,協議的處理等等如果換作FPGA來處理那就得不償失。

FPGA和DSP的區別還有很多,這里先說一點,希望能起到拋磚引玉的作用。具體的環境和設計方案各有其用武之地,設計者要根據自己的需要來選用。

Q2:在做設計之前,如何選擇FPGA呢?

A2:一般情況下,先針對設計,列出您想要實現的功能,大致畫個功能框圖,然后根據其功能和系統的要求大致推算出你需要的:

IO需求——可用IO數量、差分信號對、IO的電平格式等;

電壓源的需求——系統提供哪些電壓?核電壓需要多少?IO電壓源需要哪些?

封裝——用TQ?VQ?PLCC?BGA?還是其它的封裝形式?

內部RAM的需求——需要雙口RAM嗎?需要FIFO嗎?大小是多少?

時鐘及速度需求——最大的時鐘速率是多少?需要多少個PLL?速度等級?全局時鐘有多少?

邏輯資源和IPcore的需求——需要哪些IP核,大致占用多少資源?

擴展和升級的需求——是否考慮IO和邏輯資源留有一些余量,以便以后的擴展?升級是否方便?

價格的因素。欲了解更多信息請登錄電子發燒友網(http://www.1cnz.cn)

基本就這些,當然也可以初步選定一個型號,直接在開發軟件中對你的程序進行編譯、綜合、布局布線等,這樣能清楚地可以看到你的設計占用的資源,然后再選擇合適的型號。

Q3:FPGA對于初學者來說,應該從哪幾個方面入手?

A3:我建議初學者首先要理解FPGA的原理,這是基礎,然后設計一些小型的代碼,在驗證設計的基礎上真正的理解設計硬件的思想,那么這樣的話你必然要學到如何結合FPGA資源,特點,性能等方面知識的理論才能專心于設計代碼上。至于說芯片的設計安全也是必然要理解的,不然一個靜電上去就毀掉芯片了,那你的老板肯定要感到Surprised了。設計的精髓就是設計的思路上的問題了,包括代碼的設計技巧,系統要求的功能模塊的實現方法,多個模塊如何配合的代碼設計,后期的驗證,調試,到板級的設計調試等等,要做好FPGA設計不同于DSP,軟件設計等等,精髓的東西即使現在講給初學者,他一樣是茫然的,不知道什么是什么,因為這是需要很強的功力才能理解和體會到的。需要時間需要付出,需要努力吃苦鉆研技術,更需要成長的路上有良師的指導和同行朋友的交流,需要長期的積累的。到那時你就是專家了。

Q4:用Actel的方案進行加密后,成本上有增加嗎?

A4:用ACTEL方案加密,成本不會增加。因為ACTEL的FPGA是單芯片的,所有的編程信息已經編程在FPGA內部,有了加密選項該信息不會被讀出。

Q5:作為剛接觸FPGA的初學者,是否一開始就要深入了解芯片安全設計的精髓或者是原理之類的,還是應該把重點放在如何設計代碼上?

A5:了解FPGA的原理和代碼設計,兩者缺一不可。只有了解FPGA的結構,才能設計出更好的代碼;編寫代碼能實現自己的設計意圖,最終能熟練地使用FPGA。

Q6:系統中運放很多都是閉環應用,但是仿真的時候經常要開環仿真,可是開環仿真不能真實模擬其實際工作環境,我該如何仿真呢?

A6:這里應該是指的FPGA仿真吧,如果是運放的話要定好芯片之前就看懂了芯片手冊了,然后在實際的環境中測試,在軟件環境里仿真的話需要特別的工具,我目前不是很清楚。但是我們可以單就FPGA的仿真來談問題。實際的環境中的仿真是板級的,但是也必須有信號源和反饋信號,否則這個閉環還是不會響應外界的信號而發揮其功能的。根據這個思想我們就要額外設計一個或是多個模塊或是叫做模擬出一個信號源和接收反饋信號的模塊,這里的模擬不是模擬信號的意思而是我們從設計的角度來看就是寫一些Testbench,設計FPGA的會使用Verilog或是VHDL,做前端的RTL代碼后我們其后可以借用Modelsim或是別的仿真軟件輸入滿足設計需要的信號源(Testbench)查看波形,對于自己關注的節點或是信號標注以特別的名字,我們就能實現所謂的閉環仿真了。

Q7:Actel的設計安全保護和計算機網絡安全DES和RSA算法有什么聯系或者是互補的關聯?

A7:ACTEL的設計安全是對設計的內容進行保密,阻止非法讀取和寫入;而計算機網絡中的DES和RSA是對網絡上流動的數據進行加密/解密。兩者關系不大。

Q8:關于全定制或半定制ASIC方面,是否也有同樣安全設計?

A8:對于全定制的ASIC,一般來說保密性不如半定制的ASIC。對于半定制的ASIC,如果定制信息很容易被讀出的話,安全性就很差了;如果采用單芯片的半定制ASIC,而且定制信息不被讀出,安全性就會很高。 欲了解更多信息請登錄電子發燒友網(http://www.1cnz.cn)

A1:這個問題要從多個角度看。它們都用于某個功能的硬件電路實現,但是它們的側重點有所不同。這里涵蓋的說一下。

1)內部資源

FPGA側重于設計具有某個功能的硬件電路,內部資源是VersaTiles(ActelFPGA)之類的微小單元,FPGA的內部單元初始在編程前都是使用的是HDL語言實現硬件電路的設計描述。FPGA內部的連線資源將這些功能模塊的內部和模塊之間的信號連接起來,構成較大的模塊。FPGA可以內部實現ALU,加法器,乘法器,累加器,FIFO,SRAM,DDRcontroller,FFT,HDLC,DMA,PWM等等數字電路,也就說我們要用其實現一個特定的或是通用的硬件功能一個或是多個模塊,這些模塊的各個細節都要要用HDL來描述設計實現。目前的FPGA都可以直接內嵌諸如ARM7,CoretexM1,Core8051等微處理器,用于FPGA的軟核的,也有的FPGA廠商將一些硬件模塊直接做到FPGA中,這些是FPGA內部的硬核。傳統的FPGA都是實現純數字電路的,業界只有Actel的FPGA實現了數模混合的PSC單芯片技術,真正的提升和擴大了FPGA的應用功能和領域。另外多數FPGA都有PLL,DLL之類的鎖相環,Slew可調,Actel的還內建了OSC,RTC,Powermanager之類的硬件單元,甚至Actel的Fusion系列還內建了600kbps的12bit的ADC以及MOSFETDriver之類模擬接口,內部有UserFlashMemeory,FlashROM等資源可以實現真正的PSC,Bootloader之類的功能。

DSP主要是算法處理,內部資源主要是乘法器,加法器之類的資源,有SPI接口,UART接口,接受一定的指令集,內部的資源基本上都是現成的,需要客戶的需要而重新配置,方便于客戶的使用,但是相對來講其功能是有局限性的,所以主要用于某些特定的領域。DSP也有內嵌的鎖相環,計數器,Baudrate發生器,有的DSP也有ADC模擬接口。

2)使用的編程語言

FPGA主要使用HDL,包括VHDl,Verilog,還有數模混合的描述語言Verilog-AMS等。DSP使用C,匯編語言編程。

3)功能角度

FPGA普遍用于實現數字電路模塊,基本上能實現所有的數字電路,傳統的數字功能模塊,以及客戶產品特定需求的數字處理模塊。FPGA的IO橋接種類繁多,不同種類的級別的FPGA支持的IO標準和協議都不盡相同,但是這些IO的驅動能力或是電壓都是可編程配置的。任何數字功能電路的實現,高速信號的處理,控制領域的信號處理,橋轉換協議的實現,Actel的Fusion還能用于電流/電壓檢測,溫度的檢測,MOSFETdriver,電源管理,其獨特的Flash工藝技術可以依靠電池供電工作,和掉電實時保存數據,超低功耗,多種工作模式(Static,Sleepmode),尤其IGLOO芯片的功能在Sleepmode下功耗只有5uW。這樣的功耗用于手機,GPS之類的移動手持設備中能發揮更大的功能應用。另外用FPGA實現ASIC的前期的設計驗證,FPGA實現DSP的功能,實現CPU的功能,MCU的功能,內存控制器,用于工業的PWM,SVPWM,Clarke,Park的正逆變換的實現,VGA控制,數據的編解碼,解復用,高達上Gbps的信號的處理,協議的轉換實現等等等等功能,都是DSP難以勝任的。

DSP內部有很多現成的硬件模塊和接口以及控制器,但是需要軟件編程設定,可以實現PWM控制,接口控制,UART接口,SPI接口等功能。但是由于受指令集的時鐘周期的限制,DSP不能處理太高的信號,至于說上Gbps的信號,LVDS之類的信號就很難以涉及了。所以相應的應用領域會有所限制。但是不同的領域客戶的設計方案不同,考慮的側重點不同,有些領域設計者也是愛好使用DSP的,諸如算法實現,協議的處理等等如果換作FPGA來處理那就得不償失。

FPGA和DSP的區別還有很多,這里先說一點,希望能起到拋磚引玉的作用。具體的環境和設計方案各有其用武之地,設計者要根據自己的需要來選用。

Q2:在做設計之前,如何選擇FPGA呢?

A2:一般情況下,先針對設計,列出您想要實現的功能,大致畫個功能框圖,然后根據其功能和系統的要求大致推算出你需要的:

IO需求——可用IO數量、差分信號對、IO的電平格式等;

電壓源的需求——系統提供哪些電壓?核電壓需要多少?IO電壓源需要哪些?

封裝——用TQ?VQ?PLCC?BGA?還是其它的封裝形式?

內部RAM的需求——需要雙口RAM嗎?需要FIFO嗎?大小是多少?

時鐘及速度需求——最大的時鐘速率是多少?需要多少個PLL?速度等級?全局時鐘有多少?

邏輯資源和IPcore的需求——需要哪些IP核,大致占用多少資源?

擴展和升級的需求——是否考慮IO和邏輯資源留有一些余量,以便以后的擴展?升級是否方便?

價格的因素。欲了解更多信息請登錄電子發燒友網(http://www.1cnz.cn)

基本就這些,當然也可以初步選定一個型號,直接在開發軟件中對你的程序進行編譯、綜合、布局布線等,這樣能清楚地可以看到你的設計占用的資源,然后再選擇合適的型號。

Q3:FPGA對于初學者來說,應該從哪幾個方面入手?

A3:我建議初學者首先要理解FPGA的原理,這是基礎,然后設計一些小型的代碼,在驗證設計的基礎上真正的理解設計硬件的思想,那么這樣的話你必然要學到如何結合FPGA資源,特點,性能等方面知識的理論才能專心于設計代碼上。至于說芯片的設計安全也是必然要理解的,不然一個靜電上去就毀掉芯片了,那你的老板肯定要感到Surprised了。設計的精髓就是設計的思路上的問題了,包括代碼的設計技巧,系統要求的功能模塊的實現方法,多個模塊如何配合的代碼設計,后期的驗證,調試,到板級的設計調試等等,要做好FPGA設計不同于DSP,軟件設計等等,精髓的東西即使現在講給初學者,他一樣是茫然的,不知道什么是什么,因為這是需要很強的功力才能理解和體會到的。需要時間需要付出,需要努力吃苦鉆研技術,更需要成長的路上有良師的指導和同行朋友的交流,需要長期的積累的。到那時你就是專家了。

Q4:用Actel的方案進行加密后,成本上有增加嗎?

A4:用ACTEL方案加密,成本不會增加。因為ACTEL的FPGA是單芯片的,所有的編程信息已經編程在FPGA內部,有了加密選項該信息不會被讀出。

Q5:作為剛接觸FPGA的初學者,是否一開始就要深入了解芯片安全設計的精髓或者是原理之類的,還是應該把重點放在如何設計代碼上?

A5:了解FPGA的原理和代碼設計,兩者缺一不可。只有了解FPGA的結構,才能設計出更好的代碼;編寫代碼能實現自己的設計意圖,最終能熟練地使用FPGA。

Q6:系統中運放很多都是閉環應用,但是仿真的時候經常要開環仿真,可是開環仿真不能真實模擬其實際工作環境,我該如何仿真呢?

A6:這里應該是指的FPGA仿真吧,如果是運放的話要定好芯片之前就看懂了芯片手冊了,然后在實際的環境中測試,在軟件環境里仿真的話需要特別的工具,我目前不是很清楚。但是我們可以單就FPGA的仿真來談問題。實際的環境中的仿真是板級的,但是也必須有信號源和反饋信號,否則這個閉環還是不會響應外界的信號而發揮其功能的。根據這個思想我們就要額外設計一個或是多個模塊或是叫做模擬出一個信號源和接收反饋信號的模塊,這里的模擬不是模擬信號的意思而是我們從設計的角度來看就是寫一些Testbench,設計FPGA的會使用Verilog或是VHDL,做前端的RTL代碼后我們其后可以借用Modelsim或是別的仿真軟件輸入滿足設計需要的信號源(Testbench)查看波形,對于自己關注的節點或是信號標注以特別的名字,我們就能實現所謂的閉環仿真了。

Q7:Actel的設計安全保護和計算機網絡安全DES和RSA算法有什么聯系或者是互補的關聯?

A7:ACTEL的設計安全是對設計的內容進行保密,阻止非法讀取和寫入;而計算機網絡中的DES和RSA是對網絡上流動的數據進行加密/解密。兩者關系不大。

Q8:關于全定制或半定制ASIC方面,是否也有同樣安全設計?

A8:對于全定制的ASIC,一般來說保密性不如半定制的ASIC。對于半定制的ASIC,如果定制信息很容易被讀出的話,安全性就很差了;如果采用單芯片的半定制ASIC,而且定制信息不被讀出,安全性就會很高。 欲了解更多信息請登錄電子發燒友網(http://www.1cnz.cn)

電子發燒友App

電子發燒友App

評論