基于eFPGAsim的電機硬件在環測試系統,是面向電驅HIL測試的高精度FPGA的解決方案,利用最新的eHS (Electric Hardware Solver)技術實現,在獲得基于FPGA片上仿真

2017-08-09 10:52:21 2930

2930

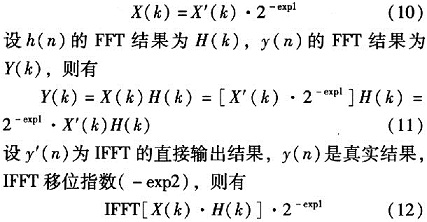

Block實現32位單精度浮點的卷積運算,而針對定點及低精度的浮點運算,則需要對硬浮點DSP Block進行相應的替換即可。

2018-07-23 09:09:45 7321

7321

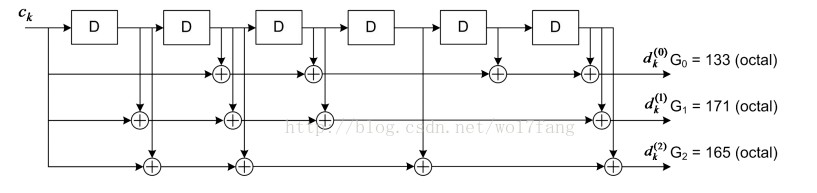

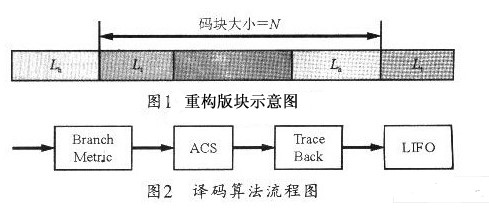

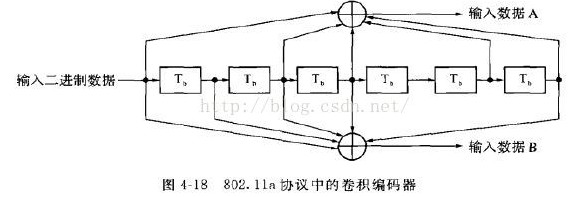

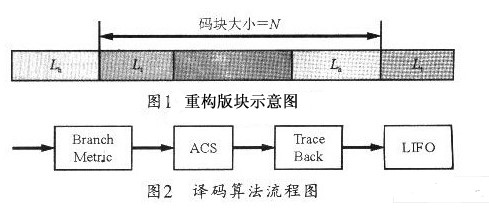

咬尾卷積碼的原理是尾卷積碼保證格形起始和終止于某個相同的狀態。它具有不要求傳輸任何額外比特的優點。

2018-08-21 09:11:53 6662

6662

?一個卷積操作占用的內存 2. PipeCNN可實現性 ??? PipeCNN論文解析:用OpenCL實現FPGA上的大型卷積網絡加速 ? ? 2.1?已實現的PipeCNN資源消耗 3. 實現大型神經網絡

2022-07-10 09:24:45 1672

1672 靈思All Programmable FPGA 和 SoC 實現高速無線電設計( Enabling High-Speed Radio Designs with Xilinx All

2017-02-10 17:10:32

本人剛入門FPGA,不知道如何實現FPGA+DSP,FPGA+ARM接口設計,網上查詢有的說FPGA+DSP可以通過EMIF,IP核實現,FPGA+ARM可以通過SPI,有沒有具體硬件參考的?

2016-08-27 11:30:26

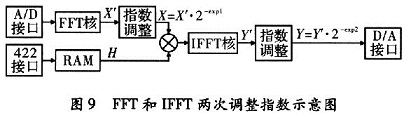

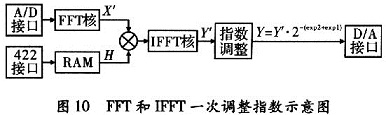

FPGA實現高速FFT處理器的設計介紹了采用Xilinx公司的Virtex - II系列FPGA設計高速FFT處理器的實現方法及技巧。充分利用Virtex - II芯片的硬件資源,減少復雜邏輯,采用

2012-08-12 11:49:01

請問各位大神,我想問一下用FPGA做卷積碼有什么注意的地方?

2015-04-07 12:57:40

卷積特性(卷積定理).zip

2017-10-04 11:36:30

這是一個高速硬件除法器,要求畫出此硬件的除法器的工作流程圖。說明其工作原理特別是高速原理。要求有仿真時序波形圖并說出說明在fpga上驗證器硬件功能。

2020-12-17 09:10:03

高速移動下OFDM均衡器的FPGA實現

2012-08-17 10:48:23

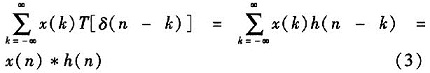

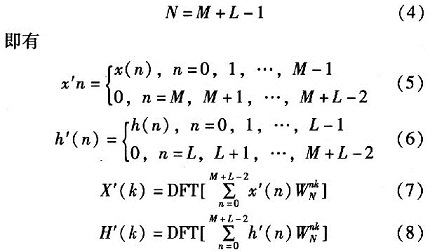

實現線性卷積的原理二 實驗內容及要求1.對N=2048或4096點的離散時間信號x(n),試用Matlab語言編程分別以DFT和FFT計算N個頻率樣值X(k), 比較兩者所用時間的大小。 2.對N/2點

2011-12-29 21:52:49

算法的軟件實現方式非常低效,所以業界對GNN的硬件加速有著非常迫切的需求。我們知道傳統的CNN(卷積神經網絡網絡)硬件加速方案已經有非常多的解決方案;但是,GNN的硬件加速尚未得到充分的討論和研究,在

2021-07-07 08:00:00

探索整個過程中資源利用的優化使整個過程更加節能高效預計成果:1、在PYNQ上實現卷積神經網絡2、對以往實現結構進行優化3、為卷積神經網絡網路在硬件上,特別是在FPGA實現提供一種優化思路和方案

2018-12-19 11:37:22

和概率譯碼兩種。代數譯碼根據卷積碼自身的代數結構進行譯碼,計算簡單;概率譯碼則在計算時考慮信道的統計特性,計算較復雜,但糾錯效果好得多。典型的算法如:Viterbi 譯碼、序列譯碼等。隨著硬件技術的發展,概率譯碼已占統制地位。[此貼子已經被作者于2008-5-30 16:09:13編輯過]

2008-05-30 16:06:52

反卷積deconvolution引起的棋盤效應?kernel size無法被stride整除的原因?解決反卷積deconvolution存在的弊端的思路?反卷積deconvolution如何實現更好的采樣 ?

2020-11-04 08:08:00

處理,設計出高速高精度 且低功耗的加速方案,并完成相關仿真和FPGA平臺的驗證,實現一個可以框選出圖像中行 人或其他物體位置的硬件電路。

本項目的系統框圖如圖2-1所示,首先PS端從SD卡讀取圖片并

2023-06-20 19:45:12

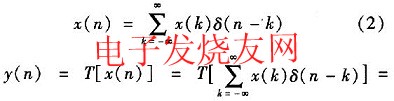

在數字信號處理領域,離散時間系統的輸出響應,可以直接由輸入信號與系統單位沖激響應的離散卷積得到。離散卷積在電子通信領域應用廣泛,是工程應用的基礎。

2019-10-16 07:52:21

本帖最后由 gk320830 于 2015-3-8 21:23 編輯

開始科創,老師給了我們一個題基于FPGA的FFT算法硬件實現。但是什么都不會,想找些論文看看,求相關的論文

2012-05-24 22:14:40

我們在此基礎上修改,從而實現,基于FPGA的動態圖片的Sobel邊緣檢測、中值濾波、Canny算子邊緣檢測、腐蝕和膨脹等。那么這篇文章我們將來實現基于FPGA的Sobel邊緣檢測。圖像邊緣:簡言之,邊緣

2017-08-29 15:41:12

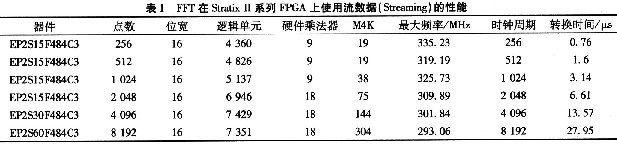

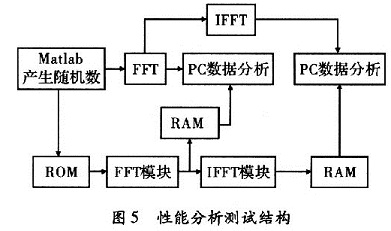

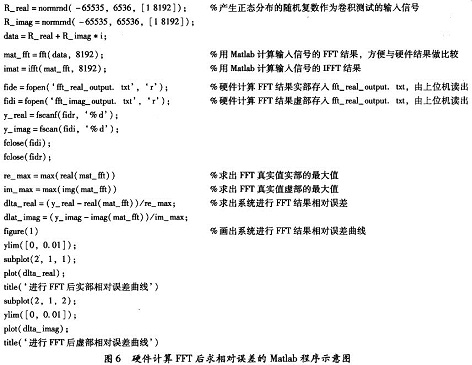

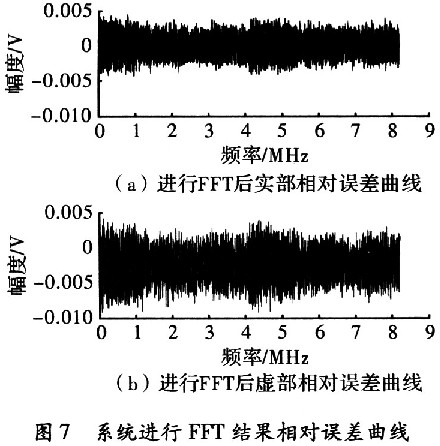

基于FPGA的超高速FFT硬件實現介紹了頻域抽取基二快速傅里葉運算的基本原理;討論了基于FPGA達4 096點的大點數超高速FFT硬件系統設計與實現方法,當多組大點數進行FFT運算時,利用FPGA

2009-06-14 00:19:55

FPGA 上實現卷積神經網絡 (CNN)。CNN 是一類深度神經網絡,在處理大規模圖像識別任務以及與機器學習類似的其他問題方面已大獲成功。在當前案例中,針對在 FPGA 上實現 CNN 做一個可行性研究

2019-06-19 07:24:41

求助!大佬們,問一下用FPGA實現卷積碼編解碼的難度。

2023-10-16 23:26:26

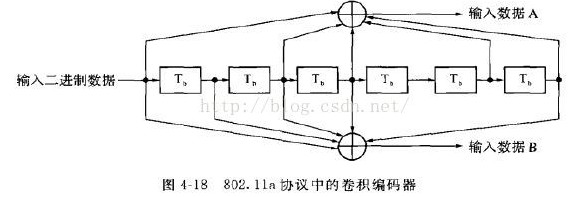

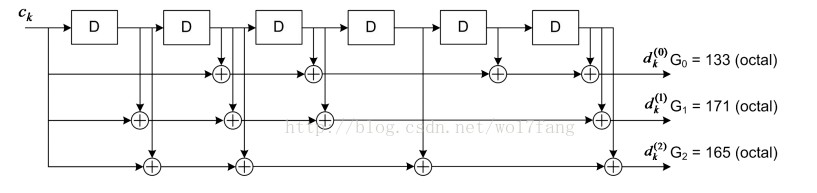

為了縮短卷積編碼器設計周期,使硬件設計更具靈活性,在介紹卷積編碼器原理的基礎上,論述了一種基于可編程邏輯器件,采用模塊化設計方法,利用VHDL硬件描述語言實現CDMA2000系統前向鏈路卷積編碼器

2019-08-27 07:41:05

現代信號處理技術通常都需要進行大量高速浮點運算。由于浮點數系統操作比較復雜,需要專用硬件來完成相關的操作(在浮點運算中的浮點加法運算幾乎占到全部運算操作的一半以上),所以,浮點加法器是現代信號

2019-08-15 08:00:45

高速連續數據采集系統的背景及功能是什么?如何利用FPGA實現高速連續數據采集系統設計?FPGA在高速連續數據采集系統中的應用有哪些?

2021-04-08 06:19:37

嵌入式測試是什么?如何用FPGA技術去實現嵌入式設計?如何測試FPGA中的高速串行I/O?

2021-04-13 07:03:58

前言FPGA 可以實現高速硬件電路,如各種時鐘,PWM,高速接口,DSP計算等硬件功能。這是Cortex-M 處理器軟件無法比擬的。要實現FPGA 的邏輯設計,對于嵌入式系統工程師又是比較復雜和具有

2021-12-21 06:13:49

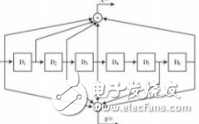

由于卷積碼具有較好的糾錯性能,因而在通信系統中被廣泛使用。采用硬件描述語言VerilogHDL或VHDL和FPGA(FieldProgrammableGateArray——現場可編程門陣列)進行數字通信系統設計,可在集成度、可靠性和靈活性等方面達到比較滿意的效果。

2019-10-14 06:02:23

在IPSec協議中認證使用SHA-1和MD5單向散列函數算法實現,通過使用FPGA高速實現SHA-1消息認證算法。

2021-04-13 06:02:01

卷積層實現在上一篇文章中,我解釋了卷積層是對圖像的過濾過程,但是并沒有解釋輸入輸出通道如何處理,過濾時圖像的邊緣處理等。由于本文旨在實現層面的理解,因此我將詳細介紹這些要點。處理 I/O 通道在圖像

2023-02-24 15:41:16

本文通過對長BCH碼優化方法的研究與討論,針對標準中二進制BCH碼的特性,設計了實現該譯碼器的FPGA硬件結構。

2021-06-15 09:23:27

本文給出了基于FPGA高速數據采集系統中的輸入輸出接口的實現,介紹了高速傳輸系統中RocketIO設計以及LVDS接口、LVPECL接口電路結構及連接方式,并在我們設計的高速數傳系統中得到應用。

2021-04-29 06:04:42

結合高速嵌入式數據采集系統,提出一種基于CvcloneⅢ FPGA實現的異步FIFO和鎖相環(PLL)結構來實現高速緩存,該結構可成倍提高數據流通速率,增加數據采集系統的實時性。采用FPGA設計高速緩存,能針對外部硬件系統的改變,通過修改片內程序以應用于不同的硬件環境。

2021-04-30 06:19:52

y(n) =x(n)* h(n)上式的運算關系稱為卷積運算,式中 代表兩個序列卷積運算。兩個序列的卷積是一個序列與另一個序列反褶后逐次移位乘積之和,故稱為離散卷積,也稱兩序列的線性卷積。其計算的過程

2012-10-31 22:29:00

,其算法的軟件實現方式非常低效,所以業界對GNN的硬件加速有著非常迫切的需求。我們知道傳統的CNN(卷積神經網絡網絡)硬件加速方案已經有非常多的解決方案;但是,GNN的硬件加速尚未得到充分的討論和研究

2020-10-20 09:48:39

本帖最后由 mr.pengyongche 于 2013-4-30 03:12 編輯

畢業設計_分段卷積MATLAB仿真與DSP實現 常用的線性卷積方法要求兩個輸入序列的持續時間相同,但在實際

2012-12-25 13:43:20

本文介紹了一種基于FPGA芯片的高速智能節點的硬件結構和軟件設計,旨在提高現在LON網絡的智能節點的處理能力和通用性。

2021-05-06 08:20:28

本帖最后由 upup11 于 2012-11-21 20:45 編輯

我想請教一個問題:如何用FPGA硬件實現小波變換。 問題的由來:我在做一個不影響語音通信的前提下,電話線感應信號特征提取

2012-11-20 21:35:16

大俠好,歡迎來到FPGA技術江湖,江湖偌大,相見即是緣分。大俠可以關注FPGA技術江湖,在“闖蕩江湖”、\"行俠仗義\"欄里獲取其他感興趣的資源,或者一起煮酒言歡。

今天

2023-05-25 18:08:24

《數字信號處理》要做課程設計,題目是:線性卷積在DSP芯片上的實現。要求:給出算法原理,寫出主程序。

2011-10-08 16:12:58

請問一下高速流水線浮點加法器的FPGA怎么實現?

2021-05-07 06:44:26

介紹了頻域抽取基二快速傅里葉運算的基本原理;討論了基于FPGA達4 096點的大點數超高速FFT硬件系統設計與實現方法,當多組大點數進行FFT運算時,利用FPGA內部大容量存儲資源,采

2009-04-26 18:33:08 26

26 本文介紹了神經網絡VLSI硬件實現的基本情況和VerilgHDL硬件設計方法的概念,在此基礎上利用FPGA設計出了Kohonen競爭網絡硬件電路,其工作頻率為33Mhz,并對其工作過程進行了較詳細的

2009-06-18 08:49:21 11

11 提出用FPGA 來實現指紋識別算法, 代替了PC 機、通用MCU 或者DSP。算法由硬件來實現, 提高了運算速度。同時具體說明了指紋識別系統的基本原理、系統總體結構、FPGA 模塊劃分, 以及指

2009-07-22 15:17:27 0

0 本文介紹了一種應用FPGA 器件完成高速數字傳輸的方法,利用這種方法實現無線收發芯片nRF2401A 的高速數據接口。為進一步提高信息的傳輸速率,這里還對待傳輸的數據進行了壓縮處

2009-08-04 09:16:20 9

9 本文介紹了一種基于FPGA 的高速多路數據采集系統的設計方案,描述了系統的主要組成及FPGA 的實現方法。在硬件上FPGA 采用ACEX1K100 器件,用于實現A/D 轉換器的控制電路、多路

2009-12-19 16:02:33 50

50 本文探討了無線通信中廣泛涉及的差錯控制問題,介紹了卷積碼的編譯碼原理。提出了一種卷積碼編碼,及其高速Viterbi 譯碼的實現方案,對譯碼的各個組成部分作了分析,并在FP

2010-01-06 15:06:59 12

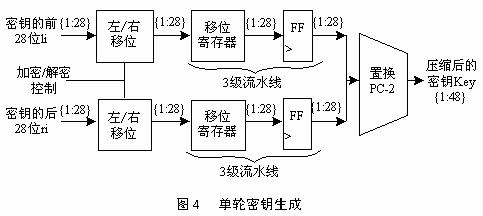

12 介紹AES 算法的原理以及基于FPGA 的高速實現。結合算法和FPGA 的特點,采用查表法優化處理了字節代換運算、列混合運算。同時,為了提高系統工作速度,在設計中應用了內外結合

2010-01-25 14:26:51 29

29 基于FPGA 的LON 網絡高速智能節點的設計作者:王傳云楊輝 來源:微計算機信息摘要:本文介紹了一種基于FPGA 芯片的高速智能節點的硬件結構和軟件設計,旨在提高現在LON 網絡的

2010-02-06 12:17:38 16

16 介紹了一種基于新型FPGA的高速數字下變頻的實現方法,它充分利用數字下變頻的優化算法以及FPGA領域的新技術,去除由于數據速率過高而造成的各種瓶頸,極大地減少了計算量和FPG

2010-07-02 16:49:24 21

21 介紹AES算法的原理以及基于FPGA的高速實現。結合算法和FPGA的特點,采用查表法優化處理了字節代換運算、列混合運算。同時,為了提高系統工作速度,在設計中應用了內外結合的流水線

2010-07-17 18:09:43 44

44 本文探討了無線通信中廣泛涉及的差錯控制問題,介紹了卷積碼的編譯碼原理。提出了一種卷積碼編碼,及其高速Viterbi譯碼的實現方案,對譯碼的各個組成部分作了分析,并在FPGA中實現

2010-07-21 17:20:04 22

22 提出了模糊CMAC網絡的一種基于FPGA的硬件實現方法。首先,分析了模糊CMAC網絡的結構與算法,并以MATLAB仿真為依據,得到模糊CMAC網絡的FPGA實現所需的參數;在此基礎上,對模糊CMAC

2010-08-09 14:55:03 19

19 為解決目前高速信號處理中的數據傳輸速度瓶頸以及傳輸距離的問題,設計并實現了一種基于FPGA 的高速數據傳輸系統,本系統借助Altera Cyclone III FPGA 的LVDS I/O 通道產生LVDS 信號,穩

2010-11-02 15:27:43 42

42 摘要:介紹3-DES算法的概要;以Xilinx公司SPARTANII結構的XC2S100為例,闡述用FPGA高速實現3-DES算法的設計要點及關鍵部分的設計。引 言

2006-03-13 19:36:42 651

651

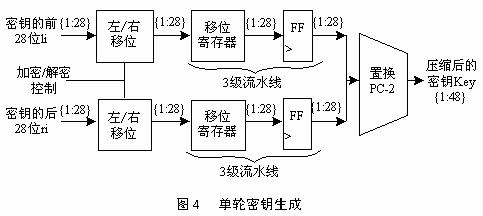

摘要:介紹3-DES算法的概要;以Xilinx公司SPARTANII結構的XC2S100為例,闡述用FPGA高速實現3-DES算法的設計要點及關鍵部分的設計。

關鍵詞:3-DES

2009-06-20 14:22:00 1317

1317

高速流水線浮點加法器的FPGA實現

0 引言現代信號處理技術通常都需要進行大量高速浮點運算。由于浮點數系統操作比較復雜,需要專用硬件來完成相關的操

2010-02-04 10:50:23 2042

2042

提出了二維模糊CMAC網絡的一種基于FPGA的硬件實現方法。首先,分析了模糊CMAC網絡的結構與算法,并以Matlab仿真為依據,得到模糊CMAC網絡的FPGA實現所需的參數;在此基礎上,對模糊CMAC網絡進行硬件模塊劃分,基于VHDL實現了各硬件模塊的功能描述,并對模塊

2011-03-15 17:19:56 29

29 System Generator 工具由 MathWorks 與 Xilinx 合作開發而成,DSP 設計人員可使用 MATLAB 和Simulink 工具在 FPGA 內進行開發和仿真來完善 DSP 設計。 該工具為系統級 DSP 設計與 FPGA 硬件實現的融合起

2011-05-11 18:36:23 224

224 基于FPGA硬件實現固定倍率的圖像縮放,將2維卷積運算分解成2次1維卷積運算,對輸入原始圖像像素先進行行方向的卷積,再進行列方向的卷積,從而得到輸出圖像像素。把圖像縮放過程

2012-05-09 15:52:04 34

34 TCAM在高速路由查找中的應用及其FPGA實現,TCAM在高速路由查找中的應用及其FPGA實現

2015-11-04 16:32:39 15

15 這是verilog寫的可以實現卷積編碼1/2碼率的代碼,附帶測試文件0

2016-01-20 18:23:39 1

1 高速專用GFP處理器的FPGA實現,下來看看

2016-05-10 11:24:33 15

15 基于FPGA的高速數據采集硬件系統設計.

2016-05-10 17:06:40 43

43 基于FPGA的高速多通道AD采樣系統的設計與實現_徐加彥

2017-01-18 20:23:58 12

12 一種高速卷積編解碼器的FPGA實現

2017-02-07 15:05:00 19

19 DSP與FPGA高速的數據傳輸有三種常用接口方式: EMIF, HPI 和 McBSP 方式。而采用 EMIF 接口方式, 利用 FPGA ( 現場可編程邏輯門陣列) 設計 FIFO的接口電路,即可實現高速互聯。

2017-02-11 14:16:10 2487

2487

(Xilinx)FPGA中LVDS差分高速傳輸的實現

2017-03-01 13:12:04 64

64 采用FPGA實現對AD 輸出數據的高速采集

2017-08-30 17:16:02 35

35 基于FPGA的高速DSP與液晶模塊接口的實現

2017-10-19 13:46:23 3

3 ,自然語言處理,推薦算法,圖像識別等廣泛的應用領域。 FPGA云服務器提供了基于FPGA的深度卷積神經網絡加速服務,單卡提供約3TOPs的定點計算能力,支持典型深度卷積網絡算子,如卷積、逆卷積、池化、拼接、切割等。有效加速典型網絡結構如VggNet、GoogLeNet、ResNet等。

2017-11-15 16:56:36 724

724

Verilog HDL硬件描述語言完成其FPGA實現與驗證,測試結果表明多速率卷積編碼器可以實時地調整碼率,高效穩定地進行差錯控制,滿足L-DACS1 高速傳輸仍保持穩定的要求,并且用于實際項目中。

2017-11-18 12:26:34 1263

1263

卷積編碼是現代數字通信系統中常見的一種前向糾錯碼,區別于常規的線性分組碼,卷積編碼的碼字輸出不僅與當前時刻的信息符號輸入有關,還與之前輸入的信息符號有關。

2018-08-21 10:26:04 7945

7945

自1955年Elias發明卷積碼以來,卷積碼作為一種高效的信道編碼已被用在許多現代通信系統中。卷積碼分為零比特卷積碼(Zero Tail CC,簡稱ZTCC)和咬尾卷積碼(Tail Biting

2019-05-03 09:00:00 3784

3784

本文提出了一種實現信號采集方案,介紹了由ARM 處理器S3C2410 和EP2C8 FPGA 組成的高速信號采集系統的系統設計,并著重介紹前端硬件的設計,并就ARM 處理器和FPGA 的互聯設計進行探討。利用FPGA 硬件控制A/D 轉換,達到了較好的效果,實現了信號的采集與存儲。

2018-11-02 15:46:01 10

10 卷積神經網絡是一類包含卷積計算且具有深度結構的前饋神經網絡,是深度學習的代表算法之一 。卷積神經網絡具有表征學習能力,能夠按其階層結構對輸入信息進行平移不變分類,因此也被稱為“平移不變人工神經網絡” 。

2019-11-25 07:04:00 2030

2030 卷積神經網絡仿造生物的視知覺(visual perception)機制構建,可以進行監督學習和非監督學習,其隱含層內的卷積核參數共享和層間連接的稀疏性使得卷積神經網絡能夠以較小的計算量對格點化

2019-11-14 07:10:00 1640

1640 目前在做FPGA移植加速CNN卷積神經網絡Inference相關的學習,使用的是Xilinx公司的ZYNQ-7000系列的FPGA開發板,該博客為記錄相關學習內容,如有問題歡迎指教。前面已經介紹

2020-12-25 17:34:36 22

22 本文檔的主要內容詳細介紹的是如何使用Xilinx的FPGA對高速PCB信號實現優化設計。

2021-01-13 17:00:59 25

25 在電子設計中,由于現場可編程門陣y~J(FPGA)的高邏輯密度和高可靠性以及用戶可編程性,受到了廣大硬件工程師的青睞。用FPGA來實現某些專用電路,可使整個設計更加緊湊、更小巧、靈活、穩定、可靠

2021-01-15 15:27:00 9

9 針對高速率QPSK數據傳輸鏈系統,比較分析了數字中頻接收與零中頻接收的優、缺點,并提出了一種基于多相濾波的寬帶中頻正交采樣數字零中頻接收方案。基于FPGA對此數字零中頻正交變換方案進行了實現和驗證,同時,對一種全數字零中頻QPSK信號的高速解調算法及其FPGA硬件實現進行了介紹。

2021-03-19 17:43:12 11

11 功能.文中將軟硬件實現的順序形態圖像處理圖片在處理效果和速度兩個方面作了比較.算法在FPGA芯片上的高速實現特征使數學形態學在圖像實時處理領域的應用成為可能。

2021-04-01 11:21:46 8

8 Xilinx zynq系列FPGA實現神經網絡評估 本篇目錄 1. 內存占用 1.1 FPGA程序中內存的實現方式 1.2 Zynq的BRAM內存大小 1.3 一個卷積操作占用的內存 2.

2021-04-19 11:12:02 2202

2202

基于FPGA的RBF神經網絡硬件實現說明。

2021-04-28 11:24:23 25

25 當前,卷積神經網絡已在圖像分類、目標檢測等計算機視覺領域被廣泛應用。然而,在前向推斷階段許多實際應用往往具有低延時和嚴格的功耗限制。針對該問題,采用參數重排序、多通道數據傳輸等優化策略,設計并實現

2021-05-28 14:00:22 23

23 基于FPGA的神經網絡硬件實現方法說明。

2021-06-01 09:35:16 37

37 電子發燒友網站提供《在FPGA上構建EVM硬件的實現.zip》資料免費下載

2023-06-26 11:50:49 0

0 電子發燒友網站提供《基于FPGA的RBF神經網絡的硬件實現.pdf》資料免費下載

2023-10-23 10:21:25 0

0

電子發燒友App

電子發燒友App

評論