利用FPGA Editor,你可以察看完成的設計并確定是否在FPGA構造一級真正實現了設計意圖 – 而這對于任何工程師或現場應用工程師來說都是非常需要的。假設你拿到協作者的設計,需要對其進行修改,但他們的HDL源代碼非常難于理解,或者根本沒有任何注釋或文檔。也許你只是想將某些時鐘邏輯鎖定,但卻不知道實例的名稱或者如何將其鎖在所希望的位置。下面討論的一些用來探查FPGA構造以及創建命令行補丁的技巧可以幫助設計人員滿足不斷迫近的任務期限要求。

FPGA構造勘察技巧

當賽靈思發布針對新FPGA器件的工具時,通常我做的第一件事就是打開FPGA Editor來勘FPGA器件的內部構造。具體做法是找到Xilinx → ISE →Accessories菜單并點擊FPGA Editor圖標,或者在命令行鍵入fpga_editor。圖形用戶界面打開后,在File菜單下選擇New。FPGA Editor會詢問設計文件名稱和物理約束文件。此時還沒有任何設計文件,因此隨便鍵入一個設計文件名(例如,test.ncd),并選擇希望察看的器件類型。FPGA Editor將會使用同樣的名字作為物理約束文件的名稱,并加載一個空白設計。

另一種方法是編譯隨軟件提供的某個ISE?工具套件設計例子,并將其加載到FPGA Editor中來察看FPGA構造。加載一個設計實例可以顯示更多細節,并且更容易定位感興趣的項目。

在FPGA Editor中瀏覽只需要記住兩件事:

1、如何利用CTRL / Shift快捷鍵進行放大縮小。

2、如果利用F11鍵放大選定的項目。

不使用GUI按鈕快速縮放的方法是,按住Ctrl 和 Shift鍵,然后分別利用鼠標左鍵和右鍵進入放大和縮小。要想快速找到任何項目,在GUI右上角的列表窗口(List window)中選擇該項目即可。一旦定位了想找的項目,按F11鍵。陣列窗口(Array window)就會放大顯示該項目。

FPGA Editor有四個主要窗口:列表(List)、全局(World)、陣列(Array)和塊(Block)。List窗口顯示設計中所有活動的項目。通過此窗口頂部的下拉菜單可選擇其內容 – 列表內容包括已經布局或還未使用的部件、網絡或未布線的網絡等等。

全局視圖窗口(World Windows)始終顯示完整FPGA硅片視圖,這在試圖確定某個網絡的布線情況時非常有用。同時,陣列窗口(Array window)則是FPGA構造和邏輯的動態視圖。如果雙擊Array視圖中的任何項目,會顯示Block視圖,給出所選擇項目或邏輯單元的詳細情況。

利用FPGA Editor,你可以察看物理實施后的設計并確定是否在FPGA構造一級真正實現了設計意圖 – 而這對于任何工程師或現場應用工程師來說都是非常需要的。

為方便瀏覽或對設計進行編輯,這些窗口可以復制。許多情況下,打開第二個Array窗口會比較方便同時在設計的兩個不同部分工作。例如,假設需要在全局時鐘緩沖器和芯片底部的觸發器之間增加一條布線。如果在一個Array窗口中顯示全局時鐘緩沖器的輸出,另一個Array窗口則顯示觸發器時鐘輸入,那么會做起來會更方便。不然的話就必須來回縮放來定位布線的兩端,顯然這很繁瑣。

在FPGA Editor GUI的右側是一組由20個功能按鈕組成的工具條,用于設計察看和編輯。通過編輯$XILINX/data目錄下的fpga_editor.ini文件可以增加更多功能按鈕。當察看設計時,應當隨時使用INFO按鈕。該功能會將所選擇項目的所有信息轉錄到控制臺(Console)窗口。這一功能非常方便,你可以在控制臺窗口中標注數據并將其拷貝到其它地方使用,例如編寫UCF約束。一旦了解了最基本的概念和操作,就可以開始察看FPGA構造。通常我都從時鐘邏輯開始。這包括數字時鐘管理器(DCM)、鎖相環(PLL)、全局時鐘緩沖器(BUFG)、區域時鐘緩沖器(BUFR)、I/O緩沖器(BUFIO)以及不同的時鐘區域。(要想按字母列出項目表,可以到LIST窗口點擊 Type來排序。)點擊一個DCM并按F11。ARRAY窗口會定位到選擇的DCM并放大顯示它。繼續點擊DCM并觀察GUI底部的Console窗口,其中會顯示與下面類似的內容:

comp “DCM_BASE_inst_star”, site “DCM_ADV_X0Y9”, type = DCM_ADV

(RPM grid X73Y202)

這是有用的數據。 拷貝并粘貼上述內容到UCF文件中,并作如下更改以鎖定這一DCM邏輯:

INST “DCM_BASE_inst_star”

LOC=DCM_ADV_X0Y9;

利用這一方法,幾乎可以鎖定FPGA中的任何項目。 下面是BUFG鎖定的另一個例子:

comp “BUFG_inst_star”, site “BUFGCTRL_X0Y20”, type = BUFG (RPM grid X73Y124)

INST “BUFG_inst_star”

LOC=BUFGCTRL_X0Y20;

再次回到List窗口并標注同一DCM。雙擊之后將會在Block視圖中顯示該DCM以及所有設置和參數。這是一項非常強大的功能,可用于FPGA構造中的任何邏輯項目。如果選擇一個邏輯片并雙擊它,就可以看到邏輯片是如何布線連接的,以及是否使用了進位鏈或本地觸發器。

Block視圖的按鈕條包含許多其它選項。值得一提的是 F= button按鈕,其功能是顯示邏輯片中使用的項目的完整配置。例如,如果使用了一個LUT6和一個觸發器,按下F= 按鈕將會給出LUT的布爾議程以及觸發器的配置模式。

閱讀賽靈思用戶指南是一回事,而從計算機屏幕上展開的視圖上探察所有邏輯、開關和參數則是另一回事。一旦熟悉了FPGA構造及所有資源,那么在編寫和驗證設計時獲得的幫助將會令人感到驚奇。在設計流程中記錄

生成補丁腳本

當用戶在GUI環境中編輯設計時,FPGA Editor能夠記錄用戶動作。用戶不僅可以保存記錄動作流程,還可在以后重新使用記錄的腳本并加以重復。當無法更改RTL,但又需要在設計過程中對設計進行修改時,這一功能特別有用。假設設計采用了第三方IP或賽靈思加密IP,其中包括一個全局時鐘和一個DCM來生成稱為 interface_clk的時鐘。然后再假設接口所連接的ASIC出現問題,無法在預定的interface_clk的上升沿接收數據。如何修正這一問題?

當然,你可以改變PCB,更換出現問題的ASIC或者讓第三方IP小組來修改時鐘輸出邏輯以提供90度相移的interface_clk。所有這些解決方案都既耗費時間又成本高昂。一個更簡單的建議是利用FPGA Editor來記錄修改動作,對interface_clk邏輯進行必要的更改,從而為出現問題的ASIC提供正確的時鐘相位。一旦有了相關修改的 FPGA Editor腳本,就可以回放這些命令行腳本記錄的修改步驟,而你也可以正常繼續你的FPGA設計流程。當出現問題的ASIC修復正常以后,你只需要將 FPGA Editor腳本從編譯腳本中移除就可以,而interface_clk也會恢復其正常的行為。

要想對設計進行手動編輯,首先需要在FPGA Editor中開啟讀/寫(read/write)權限。在菜單條中點擊File → Main Properties。在此菜單下,可以調整編輯模式(從No logic Change到Read/Write)。點擊Apply,現在就可以開始對設計進行編輯了。在下一步利用FPGA Editor記錄對設計進行的所有修改時,只需要簡單地從菜單條中點擊Tools → Scripts →Begin Recording。FPGA Editor將會提示輸入一個腳本名字(如patch.scr)。輸完腳本名字,就可以對設計進行必要的修改了。

在設計中運行設計規則檢查(DRC)來看一下是否有規則沖突的紅色標志是一個很好的方式。在我的設計例子中,有14條警告,但都可以忽略。下一步我們將需要定位interface_clk使用的DCM,并為此DCM的90度相移輸出創建另一個稱為DCM_clk90_out的時鐘。這需要利用全局時鐘布線資源將時鐘連接到BUFG。要增加一個BUFG,先在FPGA構造中找到一個未用的BUFG位置,右擊并選擇 Add(添加)。然后,工具會提醒你為BUFG命名(clk90_bufg)并確定其類型:BUFG(參見圖1)。

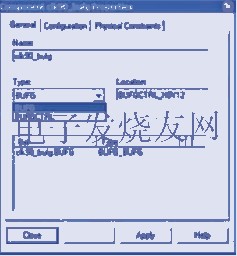

創建了新的BUFG,就需要將其輸入和輸出連接到適當的位置。在本例中,DCM的90度相移輸出將驅動BUFG。在窗口Array1中,點擊DCM 的90度輸出端衰減器,在窗口Array2中,點擊BUFG的輸入端衰減器,同時按住Ctrl鍵,可實現連接。然后釋放Ctrl鍵,點擊鼠標右鍵并選擇 Add。工具會提示為新網絡連接輸入名字。這樣就將DCM 和 BUFG通過新網絡連接到一起了(參看圖2)。

圖2:在兩個邏輯項目中手動布線時,如紅色三角所示,使用兩個Array窗口可以輕松選擇源頭和目標

clk90_bufg的輸出要代替由原interface_clk驅動的IOB上的時鐘。要將IOB從原來的時鐘域中移開,需要定位IOB,標注時鐘輸入端衰減器并按下Delete鍵移除這一連接。這樣我們就可以將新的clk90_bufg時鐘連接到這兒,從而完成整個補丁。要連接BUFG (clk90_bufg)的輸出,按住Ctrl鍵不放,在窗口Array2中標注BUFG的輸出端衰減器并在Array1窗口中選擇IOB的時鐘輸入。松開Ctrl鍵,點擊鼠標右鍵顯示選項菜單并選擇Add。這樣就最終完成了BUFG輸出和IOB之間的連接,而IOB則用來驅動下游ASIC的新建接口,利用interface_clk90時鐘就可以正確地捕獲傳輸的數據。

這樣就完成了ASIC的補丁。現在重新運行設計規則(DRC)檢查器,確保沒有引入任何新的錯誤。在菜單條中點擊Tools →DRC →Run。

腳本完成并且沒有錯誤的情況下,就可以回到菜單選擇Tool →Script →End Recording。這將停止并關閉腳本記錄過程,下次需要這一ASIC補丁時你還可以重新利用這一腳本。一個不錯的方法是在文本編輯器中打開腳本文件,將所有GUI Post 和 Unpost命令去除。這些命令并不是必要的,而且留著它們還讓腳本難于閱讀。下面的文本就是我們ASCI補丁的腳本。如前面所述,內容非常直接,易于讀取。

unselect -all

setattr main edit-mode Read-Write

add -s “BUFGCTRL_X0Y28” comp

clk90_bufg ;

setattr comp clk90_bufg type BUFG

unselect -all

select pin ‘BUFGCTRL_X0Y28.I0’

select pin ‘DCM_ADV_X0Y11.CLK90’

add

post attr net $NET_0

setattr net $NET_0 name

DCM_clk90_out

unselect -all

select pin ‘OLOGIC_X0Y2.CLK’

delete

unselect -all

select pin ‘ILOGIC_X0Y3.CLK’

delete

unselect -all

select pin ‘ILOGIC_X0Y3.CLK’

select pin ‘OLOGIC_X0Y2.CLK’

select pin ‘BUFGCTRL_X0Y28.O’

add

post attr net $NET_1

setattr net $NET_1 name

clk90_bufg_out

unselect -all

drc

save -w design “patch.ncd”

“patch.pcf”

exit

end

仔細看看腳本內容,看能否分辨出對應GUI中做的動作。

很重要的是,可以從GUI(在菜單條 Tool →Scripts →Playback下)中或命令行回放這一腳本。要在編譯腳本中加入補丁,只需要增加下面一條命令就可以了:

fpga_edline yourdesign.ncd

yourdesign.pcf -p yourscript.scr

應當在布局布線(PAR)完成后再執行這一命令,即當NCD和PCF文件完成后。

FPGA Editor真的是一項強大的用戶工具,盡管并非每個人都希望或需要在設計過程中用到它。但當需要一些特殊處理或需要在某些地方突破規則以使設計功能更強時,沒有其它工具能夠像FPGA Editor一樣提供如此強大的能力。你的FAE能夠向你展示其功能,展示FPGA Editor如何幫助你完成設計調試和驗證,當然還包括對規則的突破。

電子發燒友App

電子發燒友App

評論