1.引言

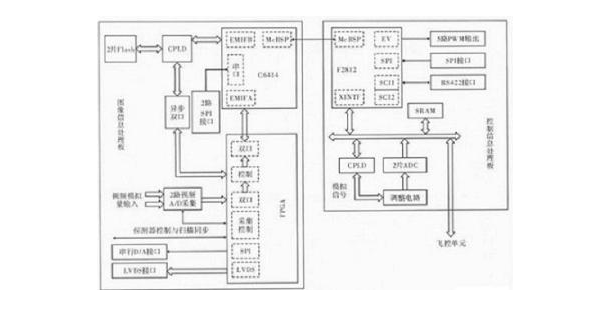

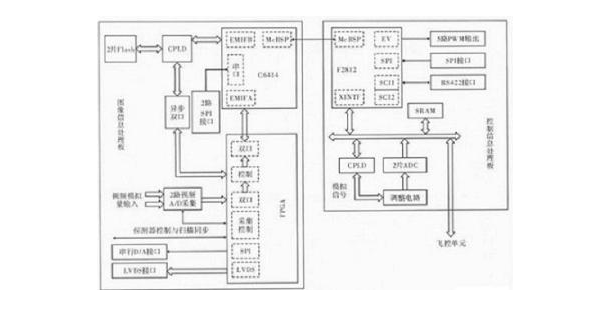

本文針對(duì)紅外圖像處理系統(tǒng)的實(shí)時(shí)性要求,提出了基于DSP+FPGA+ASIC的圖像處理架構(gòu)。

隨著紅外焦

2010-07-22 15:18:50 796

796 DSP+FPGA架構(gòu)的最大特點(diǎn)是結(jié)構(gòu)靈活、有較強(qiáng)的通用性、適合于模塊化設(shè)計(jì),從而能夠提高算法效率,同時(shí)其開(kāi)發(fā)周期短、系統(tǒng)易于維護(hù)和升級(jí),適合于實(shí)時(shí)視頻圖像處理。

2015-02-03 15:20:47 1166

1166

新一代紅外成像導(dǎo)引系統(tǒng)須具備高精度、處理速度快、實(shí)時(shí)性強(qiáng)且反應(yīng)時(shí)間短等特點(diǎn),這便要求圖像處理計(jì)算機(jī)能滿足圖像處理中大數(shù)據(jù)量、復(fù)雜運(yùn)算、實(shí)時(shí)性強(qiáng)、高傳輸率和穩(wěn)定可靠等要求。文中從工作原理、硬件及軟件3個(gè)方面介紹了基于DSP和FPGA芯片的紅外信息數(shù)據(jù)處理系統(tǒng)設(shè)計(jì)方法。

2015-07-30 14:43:57 503

503

設(shè)計(jì)了一種基于FPGA的實(shí)時(shí)視頻圖像采集處理電路系統(tǒng)。采用FPGA作為整個(gè)系統(tǒng)的控制和圖像數(shù)據(jù)處理中心。DDR2 SDRAM為高速儲(chǔ)存模塊核心器件,CMOS 7670為視頻圖像采集器件。

2018-02-10 02:43:55 19311

19311

什么是DSP圖像處理系統(tǒng)?DSP圖像處理系統(tǒng)中信號(hào)完整性的問(wèn)題是什么?有哪些解決方案?

2021-06-01 06:40:35

本帖最后由 mr.pengyongche 于 2013-4-30 02:57 編輯

FPGA+DSP 在空中背景下運(yùn)動(dòng)目標(biāo)實(shí)時(shí)跟蹤系統(tǒng)中的應(yīng)用 摘要:針對(duì)電視跟蹤系統(tǒng)對(duì)飛行目標(biāo)的檢測(cè)與跟蹤受到速度瓶頸

2012-12-28 11:19:07

本人剛?cè)腴T(mén)FPGA,不知道如何實(shí)現(xiàn)FPGA+DSP,FPGA+ARM接口設(shè)計(jì),網(wǎng)上查詢有的說(shuō)FPGA+DSP可以通過(guò)EMIF,IP核實(shí)現(xiàn),FPGA+ARM可以通過(guò)SPI,有沒(méi)有具體硬件參考的?

2016-08-27 11:30:26

來(lái)說(shuō),濾除噪聲、擴(kuò)展對(duì)比度、銳化以及色彩增強(qiáng)等處理能顯著提升視覺(jué)效果。這里設(shè)計(jì)一個(gè)基于FPGA的實(shí)時(shí)視頻圖像處理系統(tǒng),包含增強(qiáng)對(duì)比度擴(kuò)展和色飽和度兩種處理方法,相比于DSP和ASIC方案來(lái)說(shuō),FPGA在性能和靈活性方面具有絕對(duì)優(yōu)勢(shì),應(yīng)用FPGA設(shè)計(jì)視頻通信系統(tǒng)更普遍。

2019-08-22 08:22:29

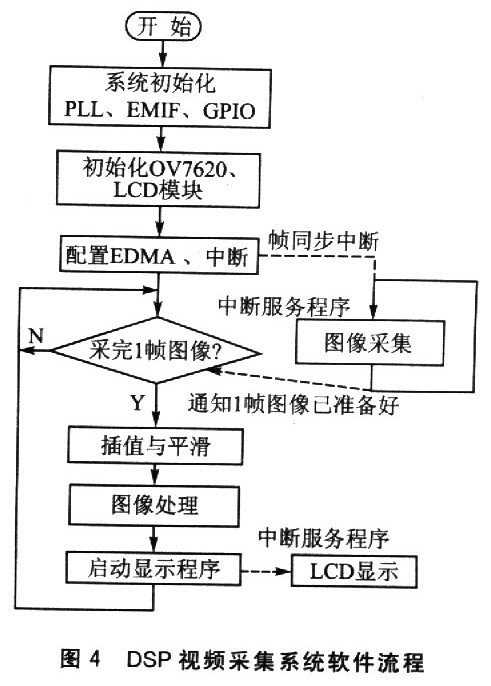

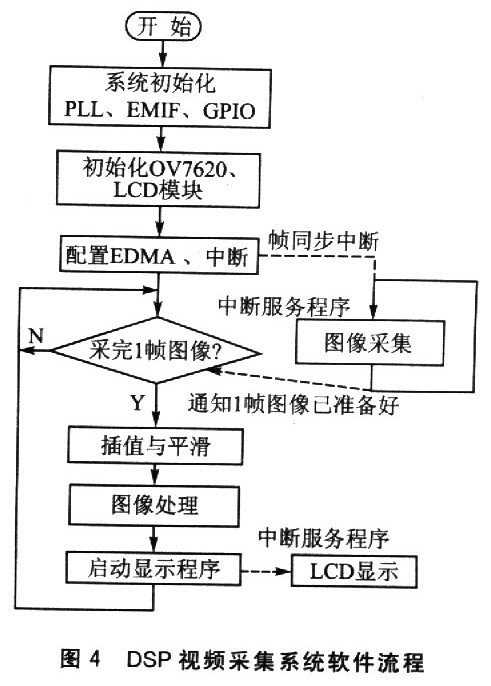

為什么要推出DM642型處理器?DM642的EDMA控制器是什么?它有什么功能?EDMA的控制機(jī)制是怎樣的?EDMA是如何進(jìn)行傳輸操作的?EDMA在實(shí)時(shí)圖像處理系統(tǒng)中有哪些應(yīng)用?

2021-04-19 10:27:02

,中斷結(jié)束。重復(fù)該過(guò)程,直至全部譯碼結(jié)果輸出結(jié)束。整個(gè)軟件處理過(guò)程控制在0.3 s以內(nèi),完全可以滿足系統(tǒng)實(shí)時(shí)性要求。 本文對(duì)基于FPGA以及Nios的圖像采集與處理系統(tǒng)設(shè)計(jì)進(jìn)行了深入研究,并在設(shè)計(jì)完成

2018-10-31 16:54:52

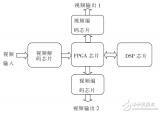

本系統(tǒng)采用基于FPGA與DSP協(xié)同工作進(jìn)行視頻處理的方案,實(shí)現(xiàn)視頻采集、處理到傳輸?shù)恼麄€(gè)過(guò)程。實(shí)時(shí)視頻圖像處理中,低層的預(yù)處理算法處理的數(shù)據(jù)量大,對(duì)處理速度要求高,但算法相對(duì)比較簡(jiǎn)單,適合于用

2019-07-01 07:38:06

為解決高速數(shù)字圖像處理系統(tǒng)和實(shí)時(shí)性相沖突的要求,設(shè)計(jì)了以多DSP(數(shù)字信號(hào)處理器TMS320C6416)和現(xiàn)場(chǎng)可編程門(mén)陣列(FPGA)相結(jié)合的實(shí)時(shí)圖像處理系統(tǒng)。重點(diǎn)介紹了該系統(tǒng)的硬件資源選擇、基本組

2021-04-28 06:14:48

引信的核心部件,是方位識(shí)別功能和目標(biāo)檢測(cè)功能的主要實(shí)現(xiàn)單元。其結(jié)構(gòu)和性能對(duì)引信的整體性能有著至關(guān)重要的影響。隨著FPGA、DSP技術(shù)的發(fā)展,數(shù)字信號(hào)處理技術(shù)在引信中的應(yīng)用大幅增強(qiáng)了引信信號(hào)的處理能力

2020-04-20 07:24:20

介紹了基于浮點(diǎn)DSP處理器與雙CMOS頭的數(shù)字圖像采集處理系統(tǒng),探討了系統(tǒng)的基本原理和設(shè)計(jì)方法,并給出了系統(tǒng)的實(shí)現(xiàn)方案。在該系統(tǒng)中,數(shù)據(jù)采集由兩個(gè)相互獨(dú)立的CMOS攝像頭完成,并由DSP進(jìn)行圖像處理

2014-11-05 14:44:51

基于DSP的圖像處理系統(tǒng)的應(yīng)用研究摘要 本文介紹了一種基于FPGA+DSP結(jié)構(gòu)的具有通用性、可擴(kuò)充性的高速數(shù)字圖像處理系統(tǒng)硬件平臺(tái)。重點(diǎn)介紹了以高速數(shù)字信號(hào)處理器TMS320DM642

2012-12-19 11:05:08

本系統(tǒng)采用基于FPGA與DSP協(xié)同工作進(jìn)行視頻處理的方案,實(shí)現(xiàn)視頻采集、處理到傳輸?shù)恼麄€(gè)過(guò)程。 實(shí)時(shí)視頻圖像處理中,低層的預(yù)處理算法處理的數(shù)據(jù)量大,對(duì)處理速度要求高,但算法相對(duì)比較簡(jiǎn)單,適合于

2019-06-28 08:10:26

圖像數(shù)據(jù)處理的工作原理是什么?基于FPGA+DSP的圖像處理系統(tǒng)待如何去設(shè)計(jì)?

2021-06-02 06:54:28

數(shù)據(jù)量特別大、運(yùn)算復(fù)雜,單純依靠通用PC很難達(dá)到實(shí)時(shí)性要求,不能滿足現(xiàn)行高速三維圖像處理應(yīng)用。 本系統(tǒng)中,采用FPGA實(shí)現(xiàn)底層的信號(hào)預(yù)處理算法,其處理數(shù)據(jù)量很大,處理速度高,但算法結(jié)構(gòu)相對(duì)

2019-06-24 06:11:03

本系統(tǒng)采用基于FPGA與DSP協(xié)同工作進(jìn)行視頻處理的方案,實(shí)現(xiàn)視頻采集、處理到傳輸?shù)恼麄€(gè)過(guò)程。 實(shí)時(shí)視頻圖像處理中,低層的預(yù)處理算法處理的數(shù)據(jù)量大,對(duì)處理速度要求高,但算法相對(duì)比較簡(jiǎn)單,適合于

2019-06-19 06:12:05

處理系統(tǒng)的發(fā)展有著千絲萬(wàn)縷的聯(lián)系。在實(shí)時(shí)圖像處理系統(tǒng)中,關(guān)鍵的技術(shù)是對(duì)實(shí)時(shí)圖像的采集和處理,圖像采集的速度、質(zhì)量直接影響到這個(gè)系統(tǒng)的性能。

2019-09-27 07:19:37

本帖最后由 lee_st 于 2017-10-31 08:26 編輯

基于FPGA的視頻圖像處理系統(tǒng)

2017-10-30 17:26:16

基于FPGA的視頻圖像處理系統(tǒng)

2015-05-27 20:34:49

基于FPGA的視頻圖像處理系統(tǒng)。

2015-05-23 12:18:23

基于fpga的實(shí)時(shí)視頻處理系統(tǒng)難點(diǎn)在哪,解決方案,誰(shuí)能幫下忙

2014-04-08 19:03:45

隨著紅外探測(cè)技術(shù)迅猛的發(fā)展,當(dāng)今紅外實(shí)時(shí)圖像處理系統(tǒng)所要處理的數(shù)據(jù)量越來(lái)越大,速度要求也越來(lái)越快,利用目前主流的單DSP+ FPGA硬件架構(gòu)進(jìn)行較為復(fù)雜的圖像處理算法運(yùn)算時(shí),有時(shí)就顯得有些捉襟見(jiàn)肘了

2019-11-08 06:31:26

目前,由于運(yùn)算速度快、片上資源豐富和能夠?qū)崿F(xiàn)復(fù)雜的線性和非線性算法等原因,DSP已成為通信、計(jì)算機(jī)和消費(fèi)電子產(chǎn)品等領(lǐng)域的基礎(chǔ)器件,其中在數(shù)字圖像處理技術(shù)中顯得尤為突出。本文就是介紹基于DSP的數(shù)字圖像處理系統(tǒng)中的抗干擾設(shè)計(jì)。

2019-10-17 06:14:39

所處理的數(shù)據(jù)量少,算法結(jié)構(gòu)復(fù)雜,適于運(yùn)算速度快,尋址靈活的DSP數(shù)字信號(hào)處理器進(jìn)行處理。這里提出了一種FPGA+DSP相結(jié)合的實(shí)時(shí)圖像處理系統(tǒng),并應(yīng)用于傳像光線束傳遞圖像。

2019-10-16 07:14:00

隨著圖像處理技術(shù)及傳感器技術(shù)的不斷發(fā)展,高清數(shù)字圖像取代模擬圖像成為一種趨勢(shì)。設(shè)計(jì)了一種基于HD-SDI技術(shù)的高清圖像處理系統(tǒng),可通過(guò)FPGA+DSP架構(gòu)對(duì)1080P全高清圖像進(jìn)行采集和字符疊加,并

2021-06-01 07:03:16

隨著紅外探測(cè)技術(shù)迅猛的發(fā)展,當(dāng)今紅外實(shí)時(shí)圖像處理系統(tǒng)所要處理的數(shù)據(jù)量越來(lái)越大,速度要求也越來(lái)越快,利用目前主流的單DSP+ FPGA硬件架構(gòu)進(jìn)行較為復(fù)雜的圖像處理算法運(yùn)算時(shí),有時(shí)就顯得有些捉襟見(jiàn)肘了

2019-08-23 08:29:27

今天給大俠帶來(lái)基于FPGA的實(shí)時(shí)圖像邊緣檢測(cè)系統(tǒng)設(shè)計(jì),由于篇幅較長(zhǎng),分三篇。今天帶來(lái)第二篇,中篇,話不多說(shuō),上貨。導(dǎo)讀隨著科學(xué)技術(shù)的高速發(fā)展,FPGA在系統(tǒng)結(jié)構(gòu)上為數(shù)字圖像處理帶來(lái)了新的契機(jī)。圖像中

2021-07-28 06:06:26

雖說(shuō)FPGA+DSP的數(shù)字硬件系統(tǒng)正好結(jié)合了兩者的優(yōu)點(diǎn),但有什么方法去證明FPGA+DSP系統(tǒng)中FPGA的關(guān)鍵技術(shù)是存在的呢?

2021-04-08 06:54:33

淺談大數(shù)據(jù)視頻圖像處理系統(tǒng)技術(shù)近年來(lái),隨著計(jì)算機(jī)、網(wǎng)絡(luò)以及圖像處理、傳輸技術(shù)的飛速發(fā)展,視頻監(jiān)控系統(tǒng)正向著高清化、智能化和網(wǎng)絡(luò)化方向發(fā)展。視頻監(jiān)控系統(tǒng)的高清化、智能化和網(wǎng)絡(luò)化為視頻監(jiān)控圖像處理技術(shù)

2013-09-24 15:22:25

怎么設(shè)計(jì)一個(gè)基于FPGA的實(shí)時(shí)視頻圖像處理系統(tǒng)?

2021-05-06 08:21:45

介紹了一種用單片FPGA實(shí)現(xiàn)的實(shí)時(shí)、多任務(wù)、高速圖像處理系統(tǒng)。該系統(tǒng)承擔(dān)著提高信噪比、壓縮數(shù)據(jù)量、Stokes參數(shù)觀測(cè)和儀器及觀測(cè)模式控制等任務(wù)。針對(duì)一個(gè)星載系統(tǒng),采用了

2008-11-20 11:57:08 15

15 應(yīng)用兩片TI公司的數(shù)字信號(hào)處理器TMS320C6416為核心,以可編程邏輯陣列CPLD進(jìn)行邏輯控制,采用2片現(xiàn)場(chǎng)可編程門(mén)陣列FPGA分別作為圖像預(yù)處理和2片DSP之間的通信,實(shí)現(xiàn)了實(shí)時(shí)的基于

2009-05-09 14:41:20 21

21 為了對(duì)給定的標(biāo)記圖像進(jìn)行識(shí)別定位,該文討論了一種基于嵌入式操作系統(tǒng)VxWorks 的實(shí)時(shí)圖像采集及處理系統(tǒng),給出了該系統(tǒng)的主要架構(gòu)和系統(tǒng)采用的圖像處理算法,并對(duì)上位機(jī)和下

2009-06-11 10:27:27 23

23 設(shè)計(jì)了一種基于FPGA 和DSP 的光纖信號(hào)實(shí)時(shí)處理系統(tǒng),介紹了系統(tǒng)的硬件組成和工作原理。該系統(tǒng)采用FPGA 實(shí)現(xiàn)數(shù)據(jù)的高速采集和邏輯控制,用DSP 實(shí)現(xiàn)傳感信號(hào)的全數(shù)字解調(diào),分析了載

2009-06-19 11:17:43 24

24 以DSP TMS320C6416 為核心處理器, 設(shè)計(jì)了一種通用的MPEG-4實(shí)時(shí)圖象處理系統(tǒng)。文中對(duì)系統(tǒng)的硬件系統(tǒng)及軟件設(shè)計(jì)進(jìn)行了詳細(xì)的介紹。其中視頻采集、運(yùn)動(dòng)估計(jì)算法和軟件的優(yōu)化是保證本

2009-08-21 11:07:29 15

15 為了滿足干涉超光譜復(fù)原處理系統(tǒng)對(duì)數(shù)據(jù)及實(shí)時(shí)性要求,本文提出了一種基于多ADSP-TS101 的FPGA+DSP[1]的并行圖像處理系統(tǒng)的解決方案,并給出了具體硬件實(shí)現(xiàn)。目前,該系統(tǒng)能夠滿

2010-01-06 15:31:32 8

8 基于DSP和DSP/BIOS的實(shí)時(shí)雷達(dá)信號(hào)采集與處理系統(tǒng):介紹了一種在實(shí)時(shí)操作系統(tǒng)DSP和DSP/BIOS 平臺(tái)下的雷達(dá)信號(hào)實(shí)時(shí)采集" 處理與傳輸系統(tǒng)的設(shè)計(jì)和實(shí)現(xiàn)! 利用Tms320c6416DSP強(qiáng)大的數(shù)據(jù)處理

2010-01-16 16:59:46 25

25 介紹一種基于ADSP21060和Virtex II的星載圖像處理系統(tǒng)。分析了圖像處理系統(tǒng)的功能和任務(wù),給出了處理系統(tǒng)的硬件結(jié)構(gòu)、FPGA的功能模塊、DSP的軟件框架和模塊。通過(guò)地面原理樣機(jī)開(kāi)發(fā)

2010-07-16 15:14:20 15

15 基于DSP的圖象采集與處理系統(tǒng)的設(shè)計(jì)

圖像處理系統(tǒng)的一個(gè)關(guān)鍵問(wèn)題就是數(shù)據(jù)量龐大,數(shù)據(jù)處理相關(guān)性高,實(shí)時(shí)實(shí)現(xiàn)比較困難。即使采用高速單片機(jī)也無(wú)法

2009-04-22 20:01:19 820

820

基于DSP的實(shí)時(shí)圖像處理系統(tǒng)

引言

本文設(shè)計(jì)了基于TMS320C6000系列DSP的MPEG-4編碼器。將攝像頭獲取的圖像以MPEG-4標(biāo)準(zhǔn)進(jìn)行實(shí)時(shí)壓縮并通過(guò)VGA實(shí)時(shí)顯示,

2009-11-23 17:26:40 4938

4938

基于DSP TMS320C6416的實(shí)時(shí)圖像處理系統(tǒng)

本文設(shè)計(jì)了基于TMS320C6000系列DSP的MPEG-4編碼器。將攝像頭獲取的圖像以MPEG-4標(biāo)準(zhǔn)進(jìn)行實(shí)時(shí)壓縮并通過(guò)VGA實(shí)時(shí)顯示,

2009-11-25 10:00:35 2563

2563

基于雙DSP的實(shí)時(shí)圖像處理系統(tǒng)

介紹了基于雙DSP的實(shí)時(shí)圖像處理系統(tǒng)。該系統(tǒng)通過(guò)兩片TMS320C6201作為系統(tǒng)計(jì)算中心,通過(guò)可重構(gòu)成的FPGA計(jì)算系統(tǒng)獲得系

2009-12-08 14:25:35 1009

1009

基于DSP的最小圖像采集處理系統(tǒng)設(shè)計(jì)

采用TI公司的TMS320C6713,通過(guò)地址譯碼和總線隔離,直接將數(shù)字圖像傳感器芯片OV7620接入;利用EDMA獨(dú)立傳送的特點(diǎn),在不增加DSP軟

2010-01-12 10:44:03 1007

1007

基于DSP+FPGA+ASIC的實(shí)時(shí)圖像處理系統(tǒng)

1.引言

隨著紅外焦平面陣列技術(shù)的快速發(fā)展,紅外成像系統(tǒng)實(shí)現(xiàn)了高幀頻、高分辨率、高可靠性及微型化,在目標(biāo)跟蹤

2010-01-13 10:39:49 1115

1115

摘要:以開(kāi)發(fā)的實(shí)際系統(tǒng)為背景,論述了基于PCI總線和DSP的實(shí)時(shí)圖像采集與處理系統(tǒng)的硬件及軟件設(shè)計(jì)方案和實(shí)現(xiàn)方法。系統(tǒng)以數(shù)字CCD相機(jī)為圖像采集設(shè)備,利用PCI總線的高速數(shù)據(jù)傳輸能力和DSP強(qiáng)大的數(shù)據(jù)處理能力,實(shí)現(xiàn)了圖像的實(shí)時(shí)采集、處理和傳輸。 關(guān)鍵詞:C

2011-02-25 23:24:41 40

40 在以DSP為核心的視頻處理系統(tǒng)中,視頻采集的方法通常可以分為兩大類(lèi):自動(dòng)的視頻采集和基于DSP的視頻采集。前者通常采用CPLD/FPGA控制視頻解碼芯片,通過(guò)FIFO或者雙口RAM向DSP傳送數(shù)據(jù)

2011-09-14 17:05:31 2302

2302

針對(duì)圖像處理要求運(yùn)行復(fù)雜靈活的圖像處理算法和大數(shù)據(jù)量的數(shù)據(jù)傳輸處理的要求,提出了一種基于DSP和FPGA架構(gòu)的嵌入式圖像處理系統(tǒng),簡(jiǎn)要介紹了系統(tǒng)的工作原理,詳細(xì)介紹了系統(tǒng)硬

2011-12-05 14:12:28 62

62 在雷達(dá)信號(hào)處理、數(shù)字圖像處理等領(lǐng)域中,信號(hào)處理的實(shí)時(shí)性至關(guān)重要。由于FPGA芯片在大數(shù)據(jù)量的底層算法處理上的優(yōu)勢(shì)及DSP芯片在復(fù)雜算法處理上的優(yōu)勢(shì),DSP+FPGA的實(shí)時(shí)信號(hào)處理系統(tǒng)

2012-07-05 15:01:40 7272

7272

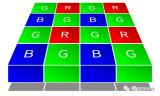

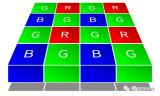

基于FPGA的Bayer到RGB圖像格式轉(zhuǎn)換設(shè)計(jì)

2016-08-29 16:05:01 35

35 基于FPGA的玻璃缺陷圖像采集預(yù)處理系統(tǒng)設(shè)計(jì)

2016-08-30 15:10:14 13

13 一種基于FPGA和PCI總線的天文圖像實(shí)時(shí)采集與處理系統(tǒng)的設(shè)計(jì),感興趣的小伙伴們可以看一看。

2016-09-14 17:17:07 8

8 基于FPGA+DSP實(shí)時(shí)圖像采集處理系統(tǒng)設(shè)計(jì)

2017-01-03 11:41:35 9

9 基于FPGA的視頻圖像處理系統(tǒng)設(shè)計(jì)_李蓮

2017-03-19 11:38:26 21

21 基于雙DSP和雙FPGA的高速圖像處理系統(tǒng)設(shè)計(jì)_吳雷

2017-03-16 09:28:51 2

2 基于DSP_FPGA的LFMCW雷達(dá)測(cè)距信號(hào)處理系統(tǒng)設(shè)計(jì)_陳林軍

2017-03-19 19:07:17 4

4 基于FPGA的軟硬件協(xié)同實(shí)時(shí)紙病圖像處理系統(tǒng)_齊璐

2017-03-19 19:07:17 0

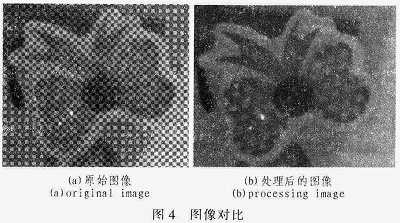

0 所處理的數(shù)據(jù)量少,算法結(jié)構(gòu)復(fù)雜,適于運(yùn)算速度快,尋址靈活的DSP數(shù)字信號(hào)處理器進(jìn)行處理。這里提出了一種FPGA+DSP相結(jié)合的實(shí)時(shí)圖像處理系統(tǒng),并應(yīng)用于傳像光線束傳遞圖像。CMOS實(shí)際采集的是光線束的出端圖像,FPGA將CMOS采集的Bayer格式

2017-10-10 16:36:38 6

6 基于FPGA和DSP的高速圖像處理系統(tǒng)

2017-10-19 13:43:31 19

19 基于DSP和FPGA的模塊化實(shí)時(shí)圖像處理系統(tǒng)設(shè)計(jì)

2017-10-23 14:09:42 9

9 基于雙DSP的全方位視覺(jué)圖像處理系統(tǒng)硬件設(shè)計(jì)與研究

2017-10-23 14:16:16 11

11 O 引言 隨著紅外探測(cè)技術(shù)迅猛的發(fā)展,當(dāng)今紅外實(shí)時(shí)圖像處理系統(tǒng)所要處理的數(shù)據(jù)量越來(lái)越大,速度要求也越來(lái)越快,利用目前主流的單DSP+ FPGA硬件架構(gòu)進(jìn)行較為復(fù)雜的圖像處理算法運(yùn)算時(shí),有時(shí)就顯得

2017-10-25 16:55:34 2

2 所處理的數(shù)據(jù)量少,算法結(jié)構(gòu)復(fù)雜,適于運(yùn)算速度快,尋址靈活的DSP數(shù)字信號(hào)處理器進(jìn)行處理。這里提出了一種FPGA+DSP相結(jié)合的實(shí)時(shí)圖像處理系統(tǒng),并應(yīng)用于傳像光線束傳遞圖像。CMOS實(shí)際采集的是光線束的出端圖像,FPGA將CMOS采集的Bayer格式的

2017-10-26 15:44:56 2

2 隨著紅外探測(cè)技術(shù)迅猛的發(fā)展,當(dāng)今紅外實(shí)時(shí)圖像處理系統(tǒng)所要處理的數(shù)據(jù)量越來(lái)越大,速度要求也越來(lái)越快,利用目前主流的單DSP+ FPGA硬件架構(gòu)進(jìn)行較為復(fù)雜的圖像處理算法運(yùn)算時(shí),有時(shí)就顯得有些捉襟見(jiàn)肘

2017-10-31 11:02:41 0

0 本文提出了一種實(shí)時(shí)圖像采集和處理系統(tǒng)的設(shè)計(jì)方法,該系統(tǒng)以TMS320DM642[1-2]為核心,結(jié)合視頻解碼芯片SAA7115H和OSD FPGA構(gòu)成實(shí)時(shí)圖像采集和處理系統(tǒng)電路。 1 系統(tǒng)總體設(shè)計(jì)

2017-10-31 16:56:33 7

7 所處理的數(shù)據(jù)量少,算法結(jié)構(gòu)復(fù)雜,適于運(yùn)算速度快,尋址靈活的DSP數(shù)字信號(hào)處理器進(jìn)行處理。這里提出了一種FPGA+DSP相結(jié)合的實(shí)時(shí)圖像處理系統(tǒng),并應(yīng)用于傳像光線束傳遞圖像。CMOS實(shí)際采集的是光線束的出端圖像,FPGA將CMOS采集的Bayer格式的

2017-10-31 17:00:34 12

12 為解決高速數(shù)字圖像處理系統(tǒng)和實(shí)時(shí)性相沖突的要求,設(shè)計(jì)了以多DSP(數(shù)字信號(hào)處理器TMS320C6416)和現(xiàn)場(chǎng)可編程門(mén)陣列(FPGA)相結(jié)合的實(shí)時(shí)圖像處理系統(tǒng)。重點(diǎn)介紹了該系統(tǒng)的硬件資源選擇、基本組

2017-11-18 12:34:02 4034

4034

通過(guò)研究視頻圖像處理和視頻圖像幀格式以及FIF0緩存技術(shù),提出了基于FPGA的視頻圖像處理系統(tǒng)設(shè)計(jì)。該設(shè)計(jì)運(yùn)用幀間差分法、同步FIF0緩存設(shè)計(jì),有效避免了圖像處理系統(tǒng)設(shè)計(jì)中亞穩(wěn)態(tài)和異步信號(hào)處理等時(shí)序

2017-11-22 09:13:03 4629

4629 三維圖像信息處理一直是圖像視頻處理領(lǐng)域的熱點(diǎn)和難點(diǎn),目前國(guó)內(nèi)外成熟的三維信息處理系統(tǒng)不多,已有的系統(tǒng)主要依賴高性能通用PC完成圖像采集、預(yù)處理、重建、構(gòu)型等囊括底層和高層的處理工作。三維圖像處理數(shù)據(jù)量特別大、運(yùn)算復(fù)雜,單純依靠通用PC很難達(dá)到實(shí)時(shí)性要求,不能滿足現(xiàn)行高速三維圖像處理應(yīng)用。

2018-07-19 13:25:00 1280

1280

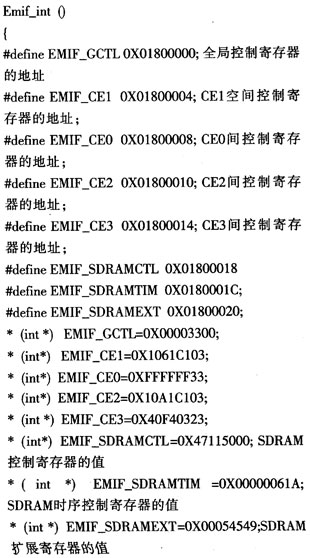

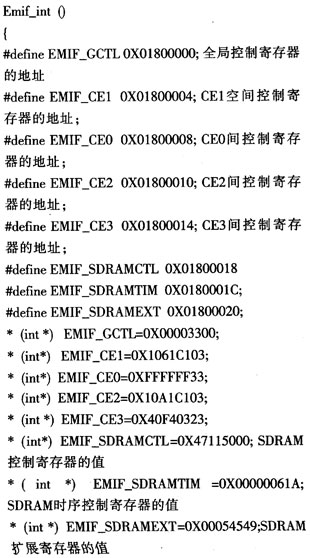

本文主要介紹了一種基于DSP+FPGA的實(shí)時(shí)圖像去霧增強(qiáng)系統(tǒng)設(shè)計(jì),FPGA通常作為一種調(diào)度使用,圖像處理算法實(shí)現(xiàn)主要靠高速處理信號(hào)處理芯片DSP完成,在跟蹤等領(lǐng)域圖像數(shù)據(jù)只需單向進(jìn)入DSP,處理后輸出相應(yīng)參數(shù)即可,在實(shí)時(shí)視頻圖像處理中大量圖像數(shù)據(jù)只需通過(guò)EMIF輸入,且輸出數(shù)據(jù)量較小可以實(shí)時(shí)完成。

2017-12-25 10:24:21 3380

3380

本文主要介紹了一種基于DSP+FPGA視頻圖像采集處理系統(tǒng)的設(shè)計(jì)與實(shí)現(xiàn),DSP-BF561作為主處理器,負(fù)責(zé)整個(gè)算法的調(diào)度和數(shù)據(jù)流的控制,完成圖像數(shù)據(jù)的采集與顯示及核心算法的實(shí)現(xiàn),FPGA作為DSP的協(xié)處理器,依托其高度的并行處理能力,完成圖像預(yù)處理中大量的累乘加運(yùn)算。實(shí)驗(yàn)證明系統(tǒng)達(dá)到了實(shí)時(shí)性要求。

2017-12-25 10:39:47 4504

4504

本文主要介紹了一種基于FPGA+DSP的視頻控制的智能交通燈設(shè)計(jì)。該交通燈由視頻采集、圖像處理和控制模塊組成,使用FPGA核心搭建專用高速視頻采集模塊,使用DSP處理器進(jìn)行實(shí)時(shí)圖像運(yùn)算,通過(guò)圖像算法提取車(chē)流量信息,最終結(jié)合模糊算法實(shí)現(xiàn)智能控制。

2018-01-09 14:15:41 1853

1853

隨著圖像處理技術(shù)及傳感器技術(shù)的不斷發(fā)展,高清數(shù)字圖像取代模擬圖像成為一種趨勢(shì)。設(shè)計(jì)了一種基于HD-SDI技術(shù)的高清圖像處理系統(tǒng),可通過(guò)FPGA+DSP架構(gòu)對(duì)1080P全高清圖像進(jìn)行采集和字符疊加

2018-01-22 07:02:13 2136

2136

bayer格式圖片是伊士曼·柯達(dá)公司科學(xué)家Bryce Bayer發(fā)明的,Bryce Bayer所發(fā)明的拜耳陣列被廣泛運(yùn)用數(shù)字圖像。

2018-07-12 14:01:00 6165

6165 FPGA+DSP的數(shù)字硬件系統(tǒng)正好結(jié)合了兩者的優(yōu)點(diǎn),兼顧了速度和靈活性。本文以導(dǎo)引頭信號(hào)處理系統(tǒng)為例說(shuō)明FPGA+DSP系統(tǒng)中FPGA的關(guān)鍵技術(shù)。

2019-01-08 08:36:00 2449

2449

大,運(yùn)算簡(jiǎn)單,但是要求運(yùn)算速率高,可以用FPGA硬件來(lái)處理,上層所處理的數(shù)據(jù)量少,算法結(jié)構(gòu)復(fù)雜,適于運(yùn)算速度快,尋址靈活的DSP數(shù)字信號(hào)處理器進(jìn)行處理。這里提出了一種FPGA+DSP相結(jié)合的實(shí)時(shí)圖像處理系統(tǒng),并應(yīng)用于傳像光線束傳遞圖像。CMOS實(shí)際采集的是光線束

2018-10-22 22:00:01 392

392 由于現(xiàn)場(chǎng)實(shí)時(shí)測(cè)量的需要,機(jī)器視覺(jué)技術(shù)越來(lái)越多地借助硬件來(lái)完成,如DSP芯片、專用圖像信號(hào)處理卡等。但是,DSP做圖像處理也面臨著由于數(shù)據(jù)存儲(chǔ)與處理量大,導(dǎo)致處理速度較慢,系統(tǒng)實(shí)時(shí)性較差的問(wèn)題。本文

2018-10-23 17:34:44 17

17 設(shè)計(jì)了一套高速線陣CCD信號(hào)采集系統(tǒng),采用FPGA+DSP的數(shù)字處理方案,能滿足光信號(hào)的實(shí)時(shí)識(shí)別和處理,可用于研究靜態(tài)和動(dòng)態(tài)小粒子的光散射彩虹特性。

2019-11-21 17:32:39 24

24 利用FPGA處理數(shù)據(jù)量大、處理速度快,結(jié)合CMOS圖像傳感器MT9M001和BayerCFA格式圖像的特點(diǎn),設(shè)計(jì)一種基于FPGA的圖像數(shù)據(jù)轉(zhuǎn)換處理系統(tǒng),提出用硬件實(shí)現(xiàn)Bayer格式到RGB格式轉(zhuǎn)換

2021-01-25 16:04:13 6

6 ,使用~tera的Quartus II軟件,完成了其中的核心模塊——F盯算法的硬件實(shí)現(xiàn),提高了處理速度;并運(yùn)用DSP處理器,設(shè)計(jì)了一個(gè)基于FPGA的實(shí)時(shí)數(shù)字圖像處理系統(tǒng).文中給出了系統(tǒng)的硬件電路和軟件算法模塊.仿真和調(diào)試結(jié)果表明:用FPGA與高速數(shù)字信

2021-02-05 15:54:00 139

139 基于FPGA+DSP彈載SAR信號(hào)處理系統(tǒng)設(shè)計(jì)

2021-12-27 18:58:51 21

21 Bayer俗稱為“拜耳陣列”,是實(shí)現(xiàn) CCD 或 CMOS?傳感器拍攝彩色圖像的主要技術(shù)之一,是伊士曼·柯達(dá)公司科學(xué)家Bryce Bayer發(fā)明的,并于1976年注冊(cè)專利,是工業(yè)相機(jī)領(lǐng)域中最為常見(jiàn)的彩色成像格式。

2023-05-29 12:05:55 4006

4006

點(diǎn)擊上方 藍(lán)字 關(guān)注我們 由于現(xiàn)場(chǎng)實(shí)時(shí)測(cè)量的需要,機(jī)器視覺(jué)技術(shù)越來(lái)越多地借助硬件來(lái)完成,如DSP芯片、專用圖像信號(hào)處理卡等。但是,DSP做圖像處理也面臨著由于數(shù)據(jù)存儲(chǔ)與處理量大,導(dǎo)致處理速度較慢

2023-06-15 15:20:02 876

876

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論