引 言

隨著航空事業的發展,空中流量的增加使空中交通管理系統的作用顯得非常重要。空管人員利用雷達為已被識別的航空器提供管制服務,可以從雷達屏幕上看到飛機的信息參數。在航管體系中,常規模式及S模式技術用于監視功能,建立在獨立編址,選擇詢問的基礎之上,信息交換是通過將上行詢問內容和下行應答內容進行脈沖編碼實現。編碼器是整個雷達的中心,用于產生整機同步信號和詢問信號。因此,具有高優良性能詢問機編碼器脈沖編碼信號處理技術至關重要。同時對雷達信號處理的實時性提出了嚴格的要求,在毫秒級的時間內完成對應答信號的處理,完成目標識別,給出目標飛行器的信息參數;同時在設備體積、功耗方面的嚴格要求使信號處理設備必須向小型化、智能化、可編程的趨勢發展,又要求信號處理系統具有高可靠性和系統升級的需要。

現場可編程邏輯器件及其相關技術是當代微電子技術迅速發展的產物,FPGA是一種多用途、高密度的可重復編程邏輯門陣列。與傳統技術相比,FPGA不僅具有設計方便,靈活和校驗快等特點,可以大大縮減研發時間,減少設計費用,降低設計風險;同時將:FPGA技術、微控制器、雷達顯控界面結合的系統應用于設計高性能的雷達信號處理機,可提高系統集成度,減小電路規模,從而提高可靠性,無論在速度、體積方面,還是在設計的靈活性上都能適應現代雷達信號處理系統的要求。

1 航管二次雷達地面詢問編碼器的工作原理

1.1 編碼器功能描述

航管二次雷達地面站收發系統由編碼器、詢問器、接收機三部分組成。如圖1所示,編碼器是整個雷達的中心,它有三個作用:

(1)產生整機的同步脈沖。它可以工作于外同步和內同步兩種方式。當同步脈沖工作于內同步,即當二次雷達獨立工作時,產生重復頻率f=150~450 Hz的整機同步信號S0。當二次雷達和一次雷達配合工作時,由一次雷達提供整機同步觸發信號,即外同步時,二次雷達的重復頻率f2和一次雷達的重復頻率 f1有以下的關系:

①當150 Hz≤f2≤450 Hz時,f2=f1;

②當450 Hz

③當900 Hz

民航規定f2≤450 Hz。重復頻率的選擇取決于作用距離的大小。

(2)產生各種詢問模式。

發射機在詢問脈沖的調制下,產生1 030 MHz的射頻脈沖,經三端環形器送到天線。天線在同步脈沖的控制下,將P1,P3進入和通道,P2進入差通道。接收機在將1 090 MHz的射頻應答信號轉換成視頻信號,送至終端裝置進行處理。

1.2 編碼器同步信號S0產生原理

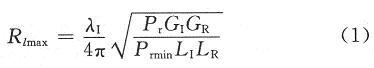

式中:Rlmax為最大詢問距離;λI為詢問射頻波長;GI為詢問天線增益;GR為應答天線增益;Prmin為應答器接收機靈敏度;Pr為地面發射機的發射功率;LI為三端環形器和饋線系統損耗;LR為應答器饋線增益。

詢問周期對應S0同步信號周期。結合實際工程的參數,按照上面公式計算出詢問時間每1μs對應的詢問距離為150 m的比例。由人工航線監視的二次雷達的作用距離為450 km時,對應詢問周期為3.5 ms;為370 km左右時,對應詢問周期為2.5 ms。機場終端區域Ⅲ監視用的作用距離為140 km時,對應詢問周期為0.000 9 ms。

?????? 1.3 編碼器系統結構

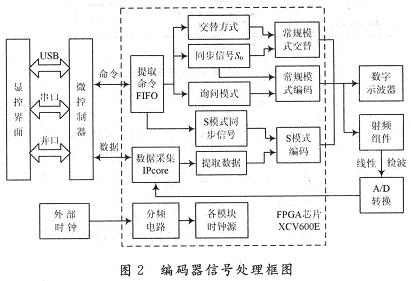

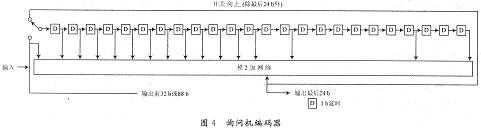

圖2所示為編碼器信號處理框圖。它采用雷達顯控界面、微處理器和FPGA芯片相結合的信號處理系統。對于編碼器的設計主要實現上述三個功能(見1.1小節),采用IPcore技術提取界面下傳數據采集和微處理器命令,采用分頻電路產生各模塊所需的時鐘,依據詢問命令產生同步編碼信號S0。由此編碼產生常規模式及其交替模式,S模式的詢問信號。可用數字示波器進行實時測量;射頻組件可對編碼信號進行測試并產生線性檢波信號,經A/D轉換后,送入 IPcore采集數字信號,并上傳至界面定性顯示波形。

2 編碼器的詢問信號格式

2.1 常規模式

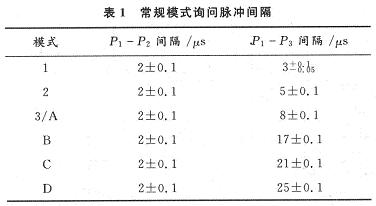

按照國際民航組織的規定有六種常規詢問模式,分別稱為1,2,3/A,B,C,D模式,各種模式的P1與P2,P1與P3之間的時間關系如表1所示。

其中,1,2兩種模式專用于軍用識別詢問;3/A模式用于軍用和民用識別詢問;C模式用于高度詢問;D模式作為備用詢問模式,其詢問內容目前還在商議之中。這些詢問模式,由間隔不同的脈沖對組成,其時間關系如表1所示。其中,第一個脈沖稱為P1;第二個脈沖稱為P2;第三個脈沖稱為P3。脈沖P1, P2,P3格式為脈寬(O.8±O.1)μs,上升沿在1~5 μs之間,延遲在0.2~5μs之間。脈沖P1和P3都是通過詢問通道傳輸的,它們之間允許不同的時間間隔。

2.2 S模式詢問信號格式

?

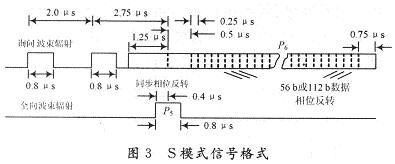

圖3表示S模式詢問格式。前兩個脈沖P1和P2的脈寬為0.8μs,間隔為2.0μs。在P2脈沖后是一個長脈沖P6,它的持續期為其脈寬,取16. 25μs或者30.25μs,其中有許多相位為反轉脈沖,用其攜帶發射數據。P6的最后24位為飛機地址,是通過全呼詢問獲得的。其中,第一個反相位于脈沖前沿后1.25μs,即P5為“同步相位反轉”信號,提供給S模式應答器作為始終同步,從而對后續的數據進行對應解碼;同步相位反轉脈沖也用作應答信號發射的時鐘參考。詢問機通過計算同步相位反轉脈沖的發射與接收到的第一個應答脈沖之間的時間間隔來測量飛機的距離。數據通過DPSK信號來發射反相位置的間隔為0.25μs,從而產生4 MHz的數據比特率。根據要求,整個發射數據的比特為56 b或者112 b。

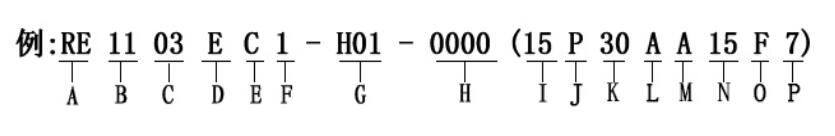

2.3 S模式奇偶與地址

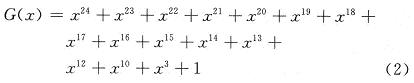

S模式P6數據位的最后奇偶24 b信息通過改進的循環冗余(CRC)編碼來計算,其多項式如下:

奇偶性在發射端計算,并與24個比特位飛機地址加入到信息中。在接收端,奇偶性再次被計算,并與信號中的奇偶和地址信息做比較,這樣可以確定信息是否發送無誤。多項式G(x)有助于錯誤探測和糾正,可以利用移位寄存器來實現,其電路如圖4所示。前32個比特位(或長S模式的88個比特位)無修改地發送,但在其發送時,會在移位寄存器反饋端乘以G(x)。對于最后循環反饋端探測信息的最后24 b會被斷開,并由24 b地址比特位代替。其結果就是信息的最后24 b包含了24 b的奇偶區域,并與飛機地址相加再乘以G(x)。

3 編碼器設計流程

編碼器的FPGA設計流程圖如圖5所示。首先提取雷達控制界面的控制命令,判斷出詢問模式和詢問方式(詢問交替方式)。結合S0產生原理和雷達詢問距離理論,用計數分頻編碼產生S0同步信號。

若是常規模式,在S0同步信號沿觸發下,按照軟件控制界面不同的控制命令,分別編碼產生周期性的6種單模式(見表1)詢問信號;并且產生對應的周期性提取信號,結合交替模式產生相應的編碼信號。

若是S模式詢問,設計流程是:首先產生S模式的前導脈沖P1,P2和數據位同步信號P5,然后判斷是短S模式(P5數據位56 b),還是長S模式(P6數據位112 b),再調用XCV600E內部的雙口RAM IPcore模塊進行數據采集,對s模式最后24 b的飛機地址數據位進行奇偶地址校驗編碼,校驗規則如圖4所示。之后再對校驗結果進行DPSK調制編碼,然后按照S模式的信號格式,在數據同步位信號P5 (見圖3)控制下,產生S模式詢問信號。

4 詢問信號的仿真波形

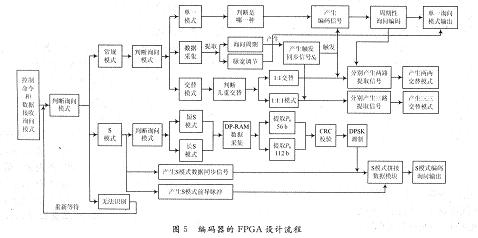

4.1 常規模式1:1:1交替詢問信號的仿真波形

首先是同步觸發信號S0的產生,由雷達顯控界面人工操作改變,對應二次雷達監視的范圍不同而具有不同的周期。一般S0的周期有2.5 ms,3.5 ms,0.000 9 ms 。

當S0的周期為3.5 ms時,其仿真結果如圖6所示。XCV600E的FPGA時鐘為40 MHz,產生周期性的S0信號。采用計數4倍、8倍、1O倍分頻產生各模塊所需的時鐘。如果改變S0的周期,可用類似的方法產生;其次是三三交替詢問模式的產生。如圖6所示,在詢問控制界面中,任選6種常規模式中的3種。在同步編碼信號S0的上升沿進行觸發,在第一個S0周期內產生詢問模式mode_1,第二個S0周期內產生詢問模式mode_2,第三個S0周期內產生詢問模式mode_3 A,第四個S0周期內產生詢問模式mode_1。按此規律周期性的產生即為三三交替詢問模式。其中,S1_revert,S2_revert, S3_revert是循環狀態機產生的周期性提取信號,分別周期性提取mode 1,mode 2,mode 3 A的編碼信號,其他單模式的編碼產生方式類似。

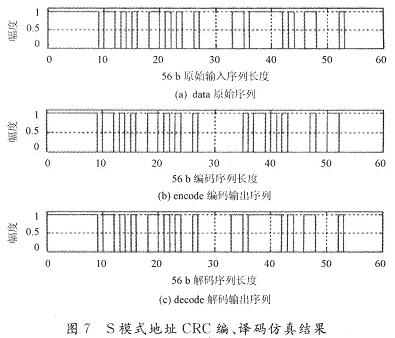

4.2 S模式CRC校驗編碼和譯碼仿真波形

依據S模式詢問機編碼器的P5位奇偶地址校驗的多項式電路規則(見圖4),應用Matlab軟件建立24個D觸發器組成的移位寄存器進行仿真。如圖7所示,仿真結果中以P5。為56 b為例,data為原始的P6數據信號,data為 “11111111101101010011010100100000011011111101001100001000”序列。其中,最后24 b表示飛機地址(初次獲得飛機地址是由“全呼詢問”獲得該校驗是“點名詢問”方式);encode為校驗輸出,其序列為 “11111111101101010011010100100000000101101010000100110000”;然后把encode作為輸入按照應答器解碼電路進行譯碼,譯碼結果為decode。由此發現譯碼結果與原始輸入數據相同,保證了校驗編碼設計的正確性。

?

5 結 語

利用FPGA的高速運算能力和IPcore技術設計高性能的二次雷達地面詢問編碼器,不但在數據采集、信號編碼時具有自適應性和可控性,而且解決了雷達信號的實時性問題,完成了多種復雜信號處理的單片FP-GA集成,有效地解決了小電路板尺寸與大存儲空間的矛盾,從而提高了系統的集成性,進一步節約了資源。同時利用“軟件顯控界面+FPGA+MCU”結合的架構技術使之更容易成為微型系統。

電子發燒友App

電子發燒友App

評論