嵌入式設(shè)計(jì)人員面臨的最大挑戰(zhàn)之一就是界定系統(tǒng)的性能需求。用以確定實(shí)際性能需求所需的信息要么無法獲取,要么難以獲得。最精確的估算有時(shí)也會因無法預(yù)料的計(jì)算負(fù)荷而失效。分析通常會指出,對于數(shù)據(jù)處理需求而言嵌入式處理系統(tǒng)的成本效益太低。因此,系統(tǒng)設(shè)計(jì)人員高度渴望擁有可擴(kuò)展的能夠適應(yīng)性能需求潛在變化以及能夠執(zhí)行高性能數(shù)據(jù)處理的架構(gòu)。而在FPGA內(nèi)部實(shí)施的控制平面/數(shù)據(jù)平面處理架構(gòu)就能夠有效滿足上述要求。

什么是控制平面/數(shù)據(jù)平面處理?為什么您的下一代嵌入式系統(tǒng)可能會需要它?

在無法用軟件完成所有處理工作的系統(tǒng)中,設(shè)計(jì)人員可以通過多種途徑來獲得其他性能。他們可以采用對稱或者非對稱處理配置的多處理器;使用硬件協(xié)處理器;或者將數(shù)據(jù)處理任務(wù)拆分給一個(gè)或多個(gè)專用處理單元——就像在控制平面/數(shù)據(jù)平面內(nèi)進(jìn)行處理一樣。

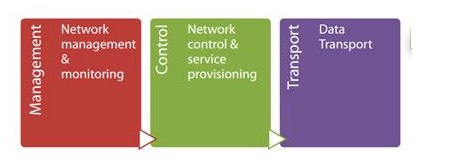

在這種編程方式下,數(shù)據(jù)處理被分成兩個(gè)不同的平面。控制平面代表著對性能影響不大的算法元素,比如管理性任務(wù)、用戶界面和操作系統(tǒng)功能。同時(shí),數(shù)據(jù)平面代表著數(shù)據(jù)在系統(tǒng)中的流動,例如視頻流或音頻流及其處理。在數(shù)據(jù)平面上,設(shè)計(jì)人員采用諸如流水線這樣的技術(shù)來增強(qiáng)數(shù)據(jù)吞吐能力。控制平面/數(shù)據(jù)平面處理的典型應(yīng)用包括流視頻、網(wǎng)絡(luò)包處理以及高速信號處理。

讓我們來近距離觀察一個(gè)涉及流數(shù)據(jù)實(shí)時(shí)處理的控制平面/數(shù)據(jù)平面應(yīng)用。我們將面臨高清視頻流特有模式的識別。該實(shí)要求混合使用高性能數(shù)據(jù)處理和包含嵌入式微處理器的控制功能的多種應(yīng)用的典型代表。

720p/60Hz的HD視頻流的像素頻率為74.25MHz。這就要求222.75MB每秒的處理速率。假定采用2.5GHz的雙核雙指令處理器來處理該數(shù)據(jù),最佳的指令率為10G指令每秒。這樣的處理器可針對所處理數(shù)據(jù)的每一字節(jié)執(zhí)行22.4條指令。對某些應(yīng)用而言這已經(jīng)足夠了,但22.4條指令表明所能處理的數(shù)據(jù)非常有限。復(fù)雜的視頻處理功能,比如內(nèi)核卷積(kernelconvolution)、噪音消減和其他過濾功能需要更高的指令執(zhí)行效率。本文的解決方案準(zhǔn)備在數(shù)據(jù)平面上創(chuàng)建并行或流水線處理單元。

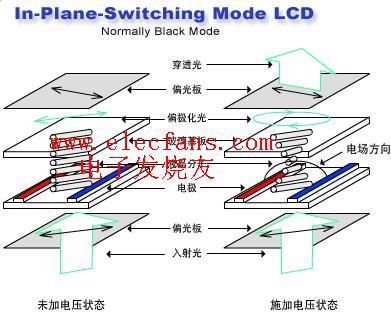

HD視頻處理是一種可以把問題劃分為控制平面和數(shù)據(jù)平面予以高效處理的常見的現(xiàn)實(shí)應(yīng)用。作為一種高度并行處理單元,F(xiàn)PGA在本例中負(fù)責(zé)視頻處理,同時(shí)由FPGA內(nèi)部的中等性能處理器負(fù)責(zé)視頻處理流水線。該處理器可專用于單個(gè)應(yīng)用,也可以運(yùn)行諸如Linux這樣的操作系統(tǒng)。最終形成的硬軟件混合實(shí)施方案可以把處理交付給能夠進(jìn)行最佳處理的部分,實(shí)現(xiàn)低成本、高性能數(shù)據(jù)處理解決方案。圖1顯示的是典型的控制平面/數(shù)據(jù)平面系統(tǒng)。

?

?

?

?

圖1:典型的控制平面/數(shù)據(jù)平面處理系統(tǒng)。

采用FPGA實(shí)現(xiàn)計(jì)算負(fù)載均衡

除了不菲的ASIC,F(xiàn)PGA是性能最高、最具經(jīng)濟(jì)效益的流數(shù)據(jù)處理單元實(shí)施方法。FPGA因其靈活的架構(gòu)而能讓設(shè)計(jì)人員實(shí)施包含并行和流水線單元的處理系統(tǒng)。這樣設(shè)計(jì)人員即可優(yōu)化系統(tǒng)的性能和時(shí)延。

設(shè)計(jì)人員隨后可以將該數(shù)據(jù)平面解決方案應(yīng)用于外部的分立微處理器以進(jìn)行控制。在FPGA內(nèi)部加入該處理器能夠帶來多項(xiàng)優(yōu)勢。內(nèi)部處理器能夠大大減少處理器和數(shù)據(jù)平面單元之間的控制時(shí)延。時(shí)延的減少可以釋放出許多處理器周期。外部處理器必須與數(shù)據(jù)平面保持通信。通信通道可以是32位或者更多位數(shù),并同時(shí)需要更多導(dǎo)線用于尋址和控制。增加的導(dǎo)線可能會要求更強(qiáng)大的處理器和FPGA封裝,從而導(dǎo)致系統(tǒng)成本增加。而采用PCIExpress(PCIe)能大幅度減少引腳數(shù)量。遺憾的是,不是所有的處理器和FPGA都支持這種相對新型的接口,而且即便支持,PCIe器件的成本也大大高于不采用PCIe的同類器件。

在FPGA內(nèi)部實(shí)施控制平面處理器和數(shù)據(jù)平面可以減少器件數(shù)量、板級空間和功耗,最終形成一個(gè)低成本的解決方案。在FPGA內(nèi)既有諸如PowerPC等硬核處理器,也有賽靈思MicroBlaze等軟核處理器,可以根據(jù)應(yīng)用要求配置基于FPGA的處理器。基于FPGA的系統(tǒng)能夠在處理器和FPGA邏輯之間移植決策和計(jì)算功能,從而實(shí)現(xiàn)系統(tǒng)級的優(yōu)化。

控制平面/數(shù)據(jù)平面系統(tǒng)的實(shí)施

某些工具可以簡化基于FPGA的控制平面/數(shù)據(jù)平面系統(tǒng)的實(shí)施。使用向?qū)Щ蛘咄ㄟ^調(diào)整現(xiàn)有參考設(shè)計(jì)來編譯系統(tǒng)是其中兩種常用的方法。

通過向?qū)PGA工具可迅速匯編微處理器系統(tǒng)。使用下拉列表或者復(fù)選框,您可以輕松地指定目標(biāo)部件以及需要的處理器和外設(shè)。同時(shí),可以使用諸如MATLAB軟件這樣的工具來迅速編譯具有處理器總線接口的信號處理流水線以用于控制。另外,還可以使用C-to-HDL工具構(gòu)建數(shù)字信號流水線。控制平面/數(shù)據(jù)平面的連接可以簡單地通過匹配總線接口來完成。圖2顯示的是啟動向?qū)У恼f明窗口和用向?qū)?gòu)建的最終系統(tǒng)。

?

圖2:向?qū)悠聊唤貓D和已完成的系統(tǒng)。

第二種方法是調(diào)整現(xiàn)有的參考設(shè)計(jì)。FPGA參考設(shè)計(jì)不斷發(fā)展并已成為市場的焦點(diǎn)。在我們的案例研究中使用的參考設(shè)計(jì)具有完整的微處理器系統(tǒng)、存儲器、外設(shè)和720pHD數(shù)字信號處理流水線。因此,該系統(tǒng)相當(dāng)于一款完整的控制平面/數(shù)據(jù)平面解決方案。在該參考設(shè)計(jì)中,由處理器控制增益和流水線中的FIR濾波器。使用C-to-FPGA工具創(chuàng)建目標(biāo)探測和高亮顯示模塊,讓整個(gè)系統(tǒng)具備功能所化的時(shí)間不到20個(gè)小時(shí)。

該處理器可以使用板卡支持包(BSP)提供的補(bǔ)充驅(qū)動程序來控制數(shù)據(jù)流水線。目前已有面向Linux的驅(qū)動程序,可以讓處理器直接控制數(shù)據(jù)處理流水線。Linux調(diào)用包括從Linux應(yīng)用中打開I/O器件,然后針對該器件進(jìn)行讀出或者寫入。

HD視頻識別系統(tǒng)案例研究

目標(biāo)檢測和識別廣泛應(yīng)用于監(jiān)控、醫(yī)學(xué)成像和工廠自動化等行業(yè)。圖像的分辨率越高,目標(biāo)識別的準(zhǔn)確度越高。因此,對HD攝影機(jī)和相關(guān)的HD視頻流處理功能的需求較為強(qiáng)勁。我們的案例研究從這個(gè)問題(受一部著名的動畫電影啟發(fā))出發(fā):我們能否檢測并高亮顯示720pHD視頻流中的小丑魚?

該設(shè)計(jì)需要16位色譜,以便識別小丑魚的條紋圖案。一旦識別,小丑魚在屏幕上將被移動的聚光燈并高亮顯示。此外,聚光燈的大小經(jīng)設(shè)計(jì)后可以隨匹配的似然性而調(diào)整(實(shí)際上,系統(tǒng)降低了聚光燈外的其他區(qū)域的圖像亮度)。聚光燈的尺寸變化和形狀計(jì)算以及為在每個(gè)像素位置搜索克隆魚所進(jìn)行的比較,將需要大量的計(jì)算以使其工作于74.25MHz的時(shí)鐘周期。顯然,這樣的處理要求大大超出了一般嵌入式處理器的能力。

在這種情況下,最好的解決辦法是把流數(shù)據(jù)處理轉(zhuǎn)移到協(xié)處理器上。在FPGA內(nèi)部實(shí)施協(xié)處理器能夠以最低成本靈活構(gòu)建能夠滿足性能要求的解決方案。因此,基于FPGA的控制平面/數(shù)據(jù)平面架構(gòu)就是最佳的選擇。FPGA嵌入式處理可以通過總線接口控制負(fù)責(zé)接收視頻數(shù)據(jù)、探測小丑魚、高亮顯示小丑魚并輸出供顯示之用的視頻數(shù)據(jù)的數(shù)字信號處理流水線。

因此,在本目標(biāo)檢測和高亮顯示案例中,我們選擇50MHz的MicroBlaze嵌入式處理器來管理和控制74.25MHz的數(shù)據(jù)處理流水線,同時(shí)管理用戶界面。在免除了實(shí)際執(zhí)行視頻處理的責(zé)任后,處理器可以處理許多其他的功能,比如托管以太網(wǎng)數(shù)據(jù)通信、管理圖形用戶界面、對數(shù)據(jù)處理流水線進(jìn)行精細(xì)控制(例如,逐幀增益控制)等。

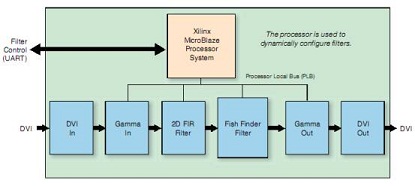

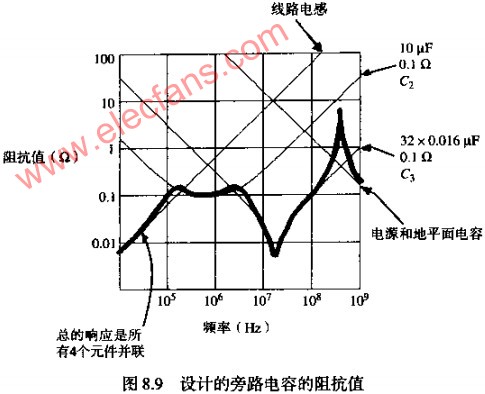

諸如Linux這樣的操作系統(tǒng)是提供多任務(wù)功能、網(wǎng)絡(luò)協(xié)議棧和用戶界面語言支持的理想選擇。圖3顯示了所實(shí)施系統(tǒng)的方框圖。該解決方案可以在高數(shù)據(jù)處理帶寬需求和用軟件控制數(shù)據(jù)處理方式之間實(shí)現(xiàn)理想的平衡。

?

圖3:小丑魚探測器控制平面/數(shù)據(jù)平面系統(tǒng)。

采用C-to-FPGA工具實(shí)現(xiàn)軟硬件協(xié)同設(shè)計(jì)

C-to-FPGA編譯器可以讓開發(fā)人員使用新的開發(fā)工具集和新技術(shù)解決軟件/硬件開發(fā)問題。開發(fā)人員可以先在軟件中進(jìn)行算法編碼。經(jīng)驗(yàn)告訴我們,在軟件中開發(fā)算法較在硬件中開發(fā)算法的效率更高。具體原因如下:首先,諸如C語言能夠讓編程人員在高級軟件語言的層面上開發(fā)算法,而這是使用Verilog或者VHDL硬件描述語言所不能達(dá)到的;其次,與同類的硬件開發(fā)工具相比,針對C語言的調(diào)試和測試工具運(yùn)行速度更快、效率更高,通常也更易于使用。相當(dāng)于硬件算法,C語言算法可以在目標(biāo)處理器上全速運(yùn)行,而硬件算法需要先在仿真程序上完成測試和調(diào)拭;最后,C語言開發(fā)工具較同類硬件開發(fā)工具的成本要低得多。因此,工程人員一般傾向于在C語言或者類似的高級語言中開發(fā)算法。

一旦使用C語言這樣的軟件語言完成對某個(gè)算法的驗(yàn)證,設(shè)計(jì)人員必須測量其性能,并確定該算法是否能夠完全在嵌入式處理器或是完全在硬件上運(yùn)行、或者硬軟件混合協(xié)處理實(shí)施方案是否為最佳選擇。在這種判斷過程中可以采用性能分析工具。如果代碼必須被轉(zhuǎn)到硬件上,則設(shè)計(jì)人員必須手工轉(zhuǎn)換算法,或者使用C-to-FPGA工具。

C-to-FPGA工具可以讓開發(fā)人員迅速把算法轉(zhuǎn)換成HDL代碼,優(yōu)化生成的硬件處理器,并執(zhí)行假設(shè)場景平衡性能和FPGA資源。該工具還能夠讓軟件工程師使用FPGA內(nèi)部的高性能數(shù)據(jù)處理邏輯,從而變身為硬件工程師。

使用Linux把處理器連接到FPGA

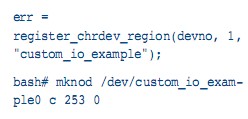

與FPGA制造商合作的Linux供應(yīng)商已經(jīng)開發(fā)完成了可讓處理器與FPGA通信并對其進(jìn)行控制的驅(qū)動程序。首先,您必須針對該I/O器件配置Linux。配置步驟由兩個(gè)步驟組成。首先,把定制的驅(qū)動程序加載到Linux內(nèi)核中:

?

隨后,將驅(qū)動程序注冊到特定的器件號碼(比如253):

?

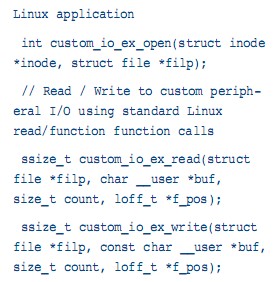

通信是通過開啟該I/O器件、然后對該器件進(jìn)行讀寫而完成的,示例代碼段如下所示:

?

?

FPGA的優(yōu)勢

信號處理器系統(tǒng)的數(shù)據(jù)帶寬要求往往會超過通用處理器能經(jīng)濟(jì)地獲得的水平。在這種情況下,設(shè)計(jì)人員一般會把他們的數(shù)據(jù)處理系統(tǒng)劃分為兩個(gè)處理功能:使用通用處理器進(jìn)行控制處理,另外使用諸如FPGA等硬件加速器進(jìn)行數(shù)據(jù)處理。這樣就構(gòu)成了一個(gè)控制平面/數(shù)據(jù)平面處理系統(tǒng)。

FPGA非常適用于同時(shí)實(shí)施控制平面和數(shù)據(jù)平面功能。一個(gè)FPGA可以包含一個(gè)或者多個(gè)像MicroBlaze這樣軟處理器,和/或像PowerPC這樣的硬處理器。將它們集成到FPGA中可以實(shí)現(xiàn)控制平面處理器和數(shù)據(jù)平面處理系統(tǒng)之間的低時(shí)延、高帶寬通信。

借助向?qū)Ш皖A(yù)先構(gòu)建的參考設(shè)計(jì),針對嵌入式和數(shù)據(jù)處理功能的系統(tǒng)編譯簡單明了。通過把在C語言中構(gòu)建的算法原型轉(zhuǎn)換到高性能硬件處理單元,C-to-FPGA工具有助于優(yōu)化這一進(jìn)程。最后,可以利用現(xiàn)在可用的Linux驅(qū)動程序方便地完成處理器和FPGA信號處理流水線之間的通信及控制編碼。

電子發(fā)燒友App

電子發(fā)燒友App

評論