1 引 言

雷達(dá)、聲納探測和超聲成像等系統(tǒng)中為了提高對目標(biāo)變化實時跟蹤和測量,就必須盡量縮短信號處理的時間,過長的運算處理時間會對水下目標(biāo)的探測性能產(chǎn)生較大的影響。聲納的檢測能力就會迅速下降,以至完全失去檢測能力,而自適應(yīng)波束形成技術(shù)(ABF)就是聲納能夠根據(jù)周圍環(huán)境噪聲場的變化,不斷地自動調(diào)節(jié)本身的參數(shù)以適應(yīng)周圍環(huán)境,抑制干擾并檢出有用信號。因此采用FPGA來實現(xiàn)自適應(yīng)波束形成算法是滿足復(fù)雜海洋環(huán)境超聲陣列波束形成的較好途徑。

最小均方自適應(yīng)算法(Least Mean Square,LMS)較其他自適應(yīng)算法具有結(jié)構(gòu)簡單,計算量小,易于實現(xiàn)等特點。FPGA實現(xiàn)LMS自適應(yīng)波束形成算法比采用現(xiàn)有DSP來實現(xiàn)可以明顯提高信號的處理速度,節(jié)約資源,能更好地滿足復(fù)雜多變的海洋環(huán)境,具有廣泛的實用價值。

波束形成系統(tǒng)相當(dāng)于一個時空濾波器,自適應(yīng)波束形成系統(tǒng)可采用IIR和FIR兩種結(jié)構(gòu)。與IIR濾波器相比,F(xiàn)IR濾波器具有以下優(yōu)點:可得到嚴(yán)格的線性相位;主要采用非遞歸結(jié)構(gòu),從理論上以及從實際的有限精度運算中,都是穩(wěn)定的;由于沖激響應(yīng)是有限長度的,因此可以用快速傅里葉變換算法,運算速度快;FIR濾波器設(shè)計方法靈活。

本文采用自適應(yīng)的FIR濾波器結(jié)構(gòu),結(jié)合時延最小均方(DLMS)算法,充分利用FPGA芯片運算速度快,存儲資源豐富等優(yōu)點設(shè)計和實現(xiàn)了基于FIR超聲陣列自適應(yīng)波束形成。主動聲納信號為窄帶信號,通常采用復(fù)數(shù)形式表示,在空間濾波器模塊采用了循環(huán)移位流水乘加器,使復(fù)數(shù)乘加運算節(jié)約了大量資源,同時用并行乘法器完成了DLMS算法,并給出了系統(tǒng)軟、硬件模塊和仿真分析。

2 超聲陣列波束形成系統(tǒng)模型及原理

2.1 系統(tǒng)架構(gòu)及原理

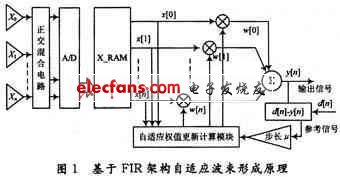

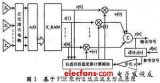

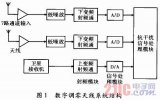

自適應(yīng)波束形成又稱自適應(yīng)空域濾波,他是通過對各陣元加權(quán)進(jìn)行空域濾波,來達(dá)到增強(qiáng)有用信號、抑制干擾的目的,而且他可以根據(jù)信號環(huán)境的變化,來改變各陣元的加權(quán)因子。在理想的條件下,自適應(yīng)波束形成技術(shù)可以有效地抑制干擾而保留期望(有用)信號,從而使陣列的輸出信號干擾噪聲比(SINR)達(dá)到最大。自適應(yīng)過程的實現(xiàn)可以采用任何一種適用于橫向結(jié)構(gòu)濾波器的自適應(yīng)迭代算法,比如Wiener濾波器,或者最小均方(LMS)算法。本設(shè)計采用最小均方(LMS)算法,系統(tǒng)結(jié)構(gòu)原理如圖1所示。

基于FIR自適應(yīng)波束形成系統(tǒng)過程如下:一方面,輸入信號與表示在n時刻的值可調(diào)節(jié)權(quán)系數(shù)ω1(n),ω2(n),…,ωm(n)相乘后相加得到輸出;另一方面,將輸出信號與期望信號進(jìn)行對比,所得的誤差值通過一定的DLMS自適應(yīng)控制算法再用來調(diào)整權(quán)值,以保證空間濾波器處在最佳狀態(tài),實現(xiàn)濾波的目的。

FIR由線性系統(tǒng)理論可知,在某種適度條件下,輸入到線性系統(tǒng)的一個沖擊完全可以表征系統(tǒng)。當(dāng)我們處理有限的離散數(shù)據(jù)時,線形系統(tǒng)的響應(yīng)(包括對沖擊的響應(yīng))也是有限的。若線性系統(tǒng)僅是一個空間濾波器,則通過簡單地觀察它對沖擊的響應(yīng),我們就可以完全確定該濾波器。通過這種方式確定的濾波器稱為有限沖擊響應(yīng)(FIR)濾波器。

FIR濾波器是在數(shù)字信號處理(DSP)中經(jīng)常使用的兩種基本的濾波器之一,另一個為IIR濾波器。IIR濾波器是無限沖激響應(yīng)濾波器。

在延時LMS算法(the Delayed LMS Algoritms,DLMS)中,將系數(shù)更新延遲幾個采樣周期,只要延遲小于系統(tǒng)階數(shù),也就是濾波器長度,則誤差梯度▽[n]=e[n]x[n],也就是▽[n]≈▽[n-D],但對于由FPGA實現(xiàn)的乘法器和系數(shù)更新需要額外的流水線級,如果引入一個延遲因子D,μ為步長因子,LMS算法就變成:

2.2 系統(tǒng)FPGA軟件模塊設(shè)計

FPGA(Field-Programmable Gate Array),即現(xiàn)場可編程門陣列,它是在PAL、GAL、CPLD等可編程器件的基礎(chǔ)上進(jìn)一步發(fā)展的產(chǎn)物。它是作為專用集成電路(ASIC)領(lǐng)域中的一種半定制電路而出現(xiàn)的,既解決了定制電路的不足,又克服了原有可編程器件門電路數(shù)有限的缺點。

目前以硬件描述語言(Verilog 或 VHDL)所完成的電路設(shè)計,可以經(jīng)過簡單的綜合與布局,快速的燒錄至 FPGA 上進(jìn)行測試,是現(xiàn)代 IC 設(shè)計驗證的技術(shù)主流。這些可編輯元件可以被用來實現(xiàn)一些基本的邏輯門電路(比如AND、OR、XOR、NOT)或者更復(fù)雜一些的組合功能比如解碼器或數(shù)學(xué)方程式。在大多數(shù)的FPGA里面,這些可編輯的元件里也包含記憶元件例如觸發(fā)器(Flip-flop)或者其他更加完整的記憶塊。

系統(tǒng)設(shè)計師可以根據(jù)需要通過可編輯的連接把FPGA內(nèi)部的邏輯塊連接起來,就好像一個電路試驗板被放在了一個芯片里。一個出廠后的成品FPGA的邏輯塊和連接可以按照設(shè)計者而改變,所以FPGA可以完成所需要的邏輯功能。

FPGA一般來說比ASIC(專用集成芯片)的速度要慢,無法完成復(fù)雜的設(shè)計,而且消耗更多的電能。但是他們也有很多的優(yōu)點比如可以快速成品,可以被修改來改正程序中的錯誤和更便宜的造價。廠商也可能會提供便宜的但是編輯能力差的FPGA。因為這些芯片有比較差的可編輯能力,所以這些設(shè)計的開發(fā)是在普通的FPGA上完成的,然后將設(shè)計轉(zhuǎn)移到一個類似于ASIC的芯片上。另外一種方法是用CPLD(復(fù)雜可編程邏輯器件備)。

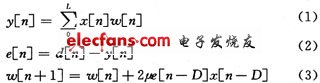

根據(jù)數(shù)字自適應(yīng)波束形成的原理和數(shù)學(xué)模型,本文設(shè)計的基于FPGA數(shù)字波束形成系統(tǒng)結(jié)構(gòu)如圖2所示。8路輸入信號x(n)經(jīng)過前端信號處理,A/D轉(zhuǎn)換后,在總控模塊的控制下進(jìn)入輸入數(shù)據(jù)存儲模塊雙口RAM,自適應(yīng)波束形成的具體實現(xiàn)步驟如下:

第一步:由式(1)得,實際輸入的x(n)和調(diào)整后的權(quán)值w(n)各分量相乘之后累加得到輸出y(n);

第二步:由式(2)得,實際輸出的y(n)與期望d(n)相減得到調(diào)整誤差e(n);

第三步:由式(3)得,延時后的調(diào)整誤差P(n)跟步長的2倍相乘,再和延時的輸入x(n-D)相乘得到的積與延時的權(quán)值相加,得到新的權(quán)值向量。

第四步:新的權(quán)值向量再與新的輸入向量循環(huán)進(jìn)行第一到第三步實現(xiàn)自適應(yīng)。

由此,我們可以將系統(tǒng)分為五大模塊:主控模塊:主要產(chǎn)生時鐘信號,給各模塊提供時序信號觸發(fā)各模塊的啟動和初始化;雙口存儲模塊(包括輸入數(shù)據(jù)存儲模塊、權(quán)值存儲模塊、誤差信號存儲模塊等):存儲各功能模塊所需的數(shù)據(jù)和參數(shù);自適應(yīng)權(quán)值計算模塊,誤差計算模塊:這兩個模塊可以合在一起,用于系數(shù)更新的白適應(yīng)算法;空間濾波器乘加模塊:完成濾波運算,得到輸出結(jié)果。

2.2.1 控制模塊

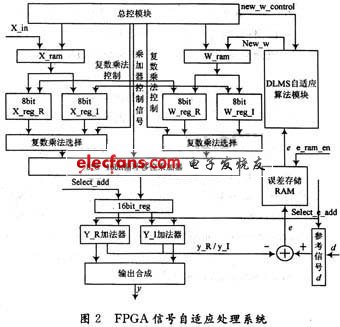

輸入信號和權(quán)值是8位的復(fù)數(shù)數(shù)據(jù),通過控制模塊選擇乘法操作的操作數(shù),兩個復(fù)數(shù)信號相乘的4種組合00,11,01,10可以完成實部和虛部之間4個乘法運算,四種情況控制模塊輸出的控制信號分別為ST0,ST1,ST2,ST3。

其中,clk_regbt用來控制乘法器完成乘法,counterbt用來控制乘數(shù)的位選,clk_reg用來控制運算新數(shù)的進(jìn)入、上次計算的完畢和結(jié)果的輸出。

2.2.2 存儲模塊

一種存儲模塊,它包括:用于根據(jù)外部指令/地址信號來產(chǎn)生內(nèi)部信號的指令/地址寄存器,且所述的指令/地址寄存器件帶有一個輸出晶體管;被分成第一和第二兩組的多個存儲器件;用于連接所述的指令/地址寄存器件和所述的存儲器件的布線;和用于安裝所述的指令/地址寄存器件和所述的存儲器件的基板;所述的布線包括:從所述的指令/地址寄存器件延伸至第一個分支結(jié)點的第一段布線;從第一個分支結(jié)點延伸至第二個分支結(jié)點的第二段布線;從第一個分支結(jié)點延伸至第三個分支結(jié)點的第三段布線;從第二個分支結(jié)點分出延伸至所述的第一組存儲器件的第四段布線;和從第三個分支結(jié)點分出延伸至第二組存儲器件的第五段布線;和所述的指令/地址寄存器件包括:阻抗調(diào)節(jié)器,用于調(diào)節(jié)從所述的指令/地址寄存器件和第一段布線之間的連接點看去所述的指令/地址寄存器件的輸出阻抗,通過調(diào)節(jié)該阻抗調(diào)節(jié)器,可使所述的輸出阻抗在內(nèi)部信號的工作電壓范圍內(nèi)基本保持不變;和上升時間/下降時間調(diào)節(jié)器,用于將內(nèi)部信號的上升時間和下降時間調(diào)節(jié)至特定值。

存儲模塊采用8位和16位雙口RAM(如圖3所示)作為信號數(shù)據(jù)和權(quán)值數(shù)據(jù)的存入和讀取存儲器,分別用來存放輸入信號x、權(quán)值ω和誤差e,分別由控制信號clkregbt,clk_regw和clk_rege來控制信號的寫入和讀出。其中x_ram用來存放輸入信號;w_ram存放權(quán)值,其輸入為系數(shù)更新模塊的輸出,輸出為更新后的權(quán)值。

2.2.3 自適應(yīng)處理及復(fù)數(shù)乘加器模塊

數(shù)字波束形成器是通過加權(quán)因子對空間不同陣元接收信號的加權(quán)求和而成的。由于加權(quán)因子相當(dāng)于濾波器系數(shù),而輸入的信號為空間位置不同的陣元的接收信號。所以可將數(shù)字波束形成器等同于一個空域濾波器來實現(xiàn)。

3 系統(tǒng)仿真與驗證

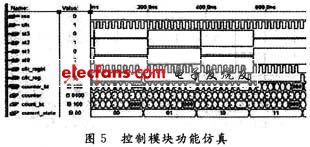

本文設(shè)計核心部分是基于Stratix系列EPlS10芯片設(shè)計的分別對I/Q兩路原始數(shù)據(jù)進(jìn)行DLMS自適應(yīng)算法和復(fù)數(shù)乘加運算,在QuartusⅡ環(huán)境下用VHDL語言編寫了各功能模塊,并進(jìn)行了仿真,共占用了2 703個邏輯單元,同時應(yīng)用Matlab對數(shù)字結(jié)果進(jìn)行波形仿真,以下為仿真驗證的結(jié)果。

圖5為主控模塊的仿真波形,其中ST0,ST1,ST2,ST3為復(fù)數(shù)乘法的4種組合,clk_regbt用來控制乘法器完成乘法,counter_bt用來控制乘數(shù)的位選,clk_reg用來控制運算新數(shù)的進(jìn)入、上次計算的完畢和結(jié)果的輸出。

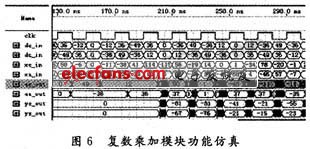

圖6為復(fù)數(shù)乘加模塊功能仿真結(jié)果,dc_out,ds_out,xc_out,xs_out分別是輸入信號和期望信號的實部和虛部,ec_out,es_out,yc_out,ys_out分別為誤差和濾波輸出的實部和虛部。

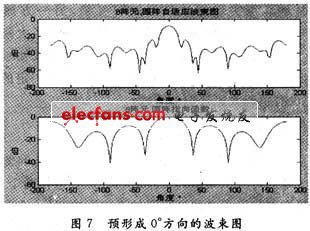

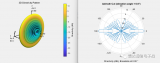

圖7為系統(tǒng)仿真測試結(jié)果:系統(tǒng)預(yù)形成波束方向為0°方向,干擾從45°傳來,通過仿真結(jié)果可以看出,主波束在0°方向形成,和預(yù)形成主波束吻合,在45°干擾方向形成零陷,并且提高了主波束的增益,滿足系統(tǒng)的設(shè)計要求。

4 結(jié) 語

本文介紹了利用FPGA芯片實現(xiàn)的自適應(yīng)BDF結(jié)構(gòu),給出了相應(yīng)的硬件設(shè)計和仿真驗證,采用FPGA結(jié)構(gòu),硬件成本低,在自適應(yīng)陣列信號處理系統(tǒng)中具有很好的應(yīng)用前景。

電子發(fā)燒友App

電子發(fā)燒友App

評論