在FPGA 上設計一個高性能、靈活的、面積小的通信體系結構是一項巨大的挑戰。大多數基于FPGA 的片上網絡都是運行在一個單一時鐘下。隨著FPGA 技術的發展,Xilinx 公司推出了Virtex-4 平臺

2011-10-21 16:13:51 1270

1270

01、如何決定FPGA中需要什么樣的時鐘速率 設計中最快的時鐘將確定 FPGA 必須能處理的時鐘速率。最快時鐘速率由設計中兩個觸發器之間一個信號的傳輸時間 P 來決定,如果 P 大于時鐘周期

2020-11-23 13:08:24 3565

3565

一般的FPGA的數據傳輸接送接口不都是用USB的么,我想用藍牙無線的接口,想買響應的藍牙模塊,有沒有能和Spartan-3 FPGA 系列 相匹配的藍牙模塊呢?

2019-08-14 16:33:55

一般的FPGA的數據傳輸接送接口不都是用USB的么,我想用藍牙無線的接口,想買響應的藍牙模塊,有沒有能和Spartan-6 FPGA 系列 相匹配的藍牙模塊呢?

2019-08-13 17:03:34

即可。

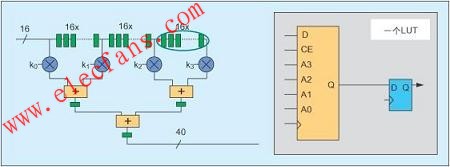

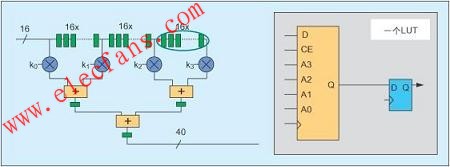

下面是一個4輸入與門的例子。

二、基于查找表(LUT)的FPGA的結構

我們看一看Xilinx Spartan-II的內部結構,如下圖:

Spartan-II主要包括CLBs

2023-11-03 11:18:38

FPGA 實現大型設計時,可能需要FPGA 具有以多個時鐘運行的多重數據通路,這種多時鐘FPGA 設計必須特別小心,需要注意最大時鐘速率、抖動、最大時鐘數、異步時鐘設計和時鐘/數據關系。設計過程中

2012-10-26 17:26:43

本帖最后由 lee_st 于 2017-10-31 08:58 編輯

FPGA多時鐘設計

2017-10-21 20:28:45

跨時鐘域處理是FPGA設計中經常遇到的問題,而如何處理好跨時鐘域間的數據,可以說是每個FPGA初學者的必修課。如果是還在校生,跨時鐘域處理也是面試中經常常被問到的一個問題。這里主要介紹三種跨時鐘域

2021-03-04 09:22:51

利用FPGA實現大型設計時,可能需要FPGA具有以多個時鐘運行的多重數據通路,這種多時鐘FPGA設計必須特別小心,需要注意最大時鐘速率、抖動、最大時鐘數、異步時鐘設計和時鐘/數據關系。設計過程中最重要的一步是確定要用多少個不同的時鐘,以及如何進行布線?

2019-08-30 08:31:41

(LUT)的FPGA的結構我們看一看xilinx Spartan-II的內部結構,如下圖: xilinx Spartan-II 芯片內部結構Slices結構Spartan-II主要包括CLBs,I

2012-04-28 14:57:28

FPGA的多時鐘系統設計 Multiple Clock System Design Clk1and Clk2are the clock which running at different frequency[/hide]

2009-12-17 15:46:09

FPGA設計中有多個時鐘域時如何處理?跨時鐘域的基本設計方法是:(1)對于單個信號,使用雙D觸發器在不同時鐘域間同步。來源于時鐘域1的信號對于時鐘域2來說是一個異步信號。異步信號進入時鐘域2后,首先

2012-02-24 15:47:57

[size=11.818181991577148px]FPGA開發中,遇到的最多的就是異步時鐘域了。[size=11.818181991577148px]檢查初學者的代碼,發現最多的就是這類

2014-08-13 15:36:55

(10)FPGA跨時鐘域處理1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA跨時鐘域處理5)結語1.2 FPGA簡介FPGA(Field Programmable

2022-02-23 07:47:50

的Spartan-3A的Spartan-3ESpartan-3系列的Spartan-IIE的Spartan-II謝謝&問候。以上來自于谷歌翻譯以下為原文Sir/ Madam, In our

2019-05-08 14:52:17

Spartan-II 應用指南XAPP058 -利用嵌入式微控制器進行Xilinx在系統(In-System)編程Xilinx 高性能CPLD、FPGA和可配置的PROM系列提供了在系統

2021-08-12 07:39:42

本帖最后由 lpc2292 于 2013-2-27 20:24 編輯

“部分 I: 用 Spartan-3 系列 FPGA 進行設計”第 1 章 “概述”第 2 章 “使用全局時鐘資源”第 3

2013-02-27 20:20:10

00000000000001000010....0...01111111111 二.基于查找表(LUT)的FPGA的結構 我們看一看xilinx Spartan-II的內部結構,如下圖:xilinx

2008-05-20 09:46:10

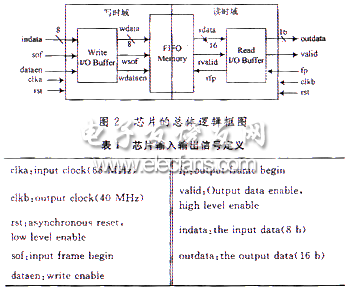

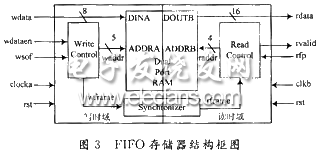

采用FPGA來設計一款廣泛應用于計算機、Modem、數據終端以及許多其他數字設備之間的數據傳輸的專用異步并行通信接口芯片,實現了某一時鐘域(如66 MHz)的8位并行數據到另一低時鐘域(如40 MHz)16

2011-09-07 09:16:40

出現問題,來自快時鐘域的控制信號必須寬于較慢時鐘的周期。否則如下圖所示,快時鐘域的控制信號無法被采樣到慢時鐘域。3、在時鐘域之間同步數據的兩種常用方法將數據從一個時鐘域傳遞到另一個時鐘域類似于傳遞多個

2022-04-11 17:06:57

HDL與VHDL的比較附錄C Virtex-II 和Spartan-II E的管腳####################################booklab1-resource包括附錄D

2013-06-02 10:13:17

組來定義策略。在多個時鐘域之間傳遞控制信號時,嘗試使用同步器的策略。嘗試使用FIFO和緩存的數據路徑同步器來提高數據完整性。現在討論重要的跨時鐘處理問題與策略及其在多時鐘域設計中的使用。多時鐘域設計有

2022-06-24 16:54:26

大家好:最近在做基于FPGA 的以太網數據通信,現在遇到的問題是利用nios i和以太網芯片通信已經實現,但是niosII 讀取的以太網傳遞的數據怎么傳遞到FPGA 頂層模塊,用硬件邏輯設計語言實現進一步處理,請大家指點,小弟不勝感激!

2016-07-13 15:59:26

雙口RAM如何實現跨時鐘域通信啊?怎么在quartus ii仿真???

2017-05-02 21:51:39

利用 FPGA 實現大型設計時,可能需要FPGA 具有以多個時鐘運行的多重數據通路,這種多時鐘 FPGA 設計必須特別小心,需要注意最大時鐘速率、抖動、最大時鐘數、異步時鐘設計和時鐘/數據關系

2012-03-05 14:42:09

跨越時鐘域FPGA設計中可以使用多個時鐘。每個時鐘形成一個FPGA內部時鐘域“,如果需要在另一個時鐘域的時鐘域產生一個信號,需要特別小心。隧道四部分第1部分:過路處。第2部分:道口標志第3部分:穿越

2012-03-19 15:16:20

跨時鐘域處理是FPGA設計中經常遇到的問題,而如何處理好跨時鐘域間的數據,可以說是每個FPGA初學者的必修課。如果是還在校生,跨時鐘域處理也是面試中經常常被問到的一個問題。這里主要介紹三種跨時鐘域

2021-02-21 07:00:00

跨時鐘域處理是FPGA設計中經常遇到的問題,而如何處理好跨時鐘域間的數據,可以說是每個FPGA初學者的必修課。如果是還在校生,跨時鐘域處理也是面試中經常常被問到的一個問題。 這里主要介紹三種跨

2021-01-08 16:55:23

嗨,在閱讀了大量文件和無數次嘗試之后,我不得不向你尋求指導。我有一個安裝了Spartan XCS1400A FPGA的ZESTET1以太網板。該板具有1 Gbps以太網接口和TCP-IP卸載引擎。我

2019-06-12 13:30:44

。像Spartan 6 XC6SLX9FPGA這樣的低端FPGA是否足以實現這種數據速度?我應該使用哪個記憶時間? 如果不是,任何想法?非常感謝您的關注。

2020-03-26 09:31:54

labview生成安裝程序(里面數據傳遞用共享變量) 在本電腦上可以傳遞數據,安裝到其他電腦上無法傳遞數據,何解?

2016-07-08 13:57:24

關于異步時鐘域的理解的問題: 這里面的count[25]、和count[14]和count[1]算是多時鐘域吧?大俠幫解決下我的心結呀,我這樣的理解對嗎?

2012-02-27 15:50:12

你好,我在Viv 2016.4上使用AC701板。我需要同步從一個時鐘域到另一個時鐘域的多位信號(33位)。對我來說,這個多位信號的3階段流水線應該足夠了。如果將所有觸發器放在同一個相同的切片

2020-08-17 07:48:54

平臺。該平臺支持同一時間內32 個時鐘運行,也就是說每個片上網絡的內核可以在一個獨立的時鐘下運行, 從而使每個路由器和IP 核都運行在最佳頻率上。因此適用于設計多時鐘片上網絡,實現高性能分組交換片上網絡。

2019-08-21 06:47:43

AD接口:時鐘對齊、根據幀同步實現串轉并數據對齊.本人非常熟悉Virtex-5/Virtex-6/7 Series FPGA的內置SERDES模塊,包括ISERDES,OSERDES,IODELAY

2014-03-01 18:47:47

本帖最后由 mingzhezhang 于 2012-5-23 20:05 編輯

大型設計中FPGA的多時鐘設計策略 利用FPGA實現大型設計時,可能需要FPGA具有以多個時鐘運行的多重數據

2012-05-23 19:59:34

利用FPGA實現大型設計時,可能需要FPGA具有以多個時鐘運行的多重數據通路,這種多時鐘FPGA設計必須特別小心,需要注意最大時鐘速率、抖動、最大時鐘數、異步時鐘設計和時鐘/數據關系。設計過程中

2015-05-22 17:19:26

嗨, 我正在使用Saturn Spartan6 numato板。我在董事會中實現了一個非常簡單的要求版本。現在我想將數據傳輸到FPGA或從FPGA傳輸到PC。請提出一些建議。謝謝。

2019-07-31 10:36:37

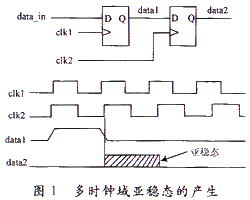

時鐘域轉換中亞穩態是怎樣產生的?多時鐘域數據傳遞的FPGA實現

2021-04-30 06:06:32

:int main (void){各種初始化while(1){ 觸摸屏 LCD刷新 串口通信 } }就像這個小例子,觸摸屏按鍵的操作和串口的數據要顯示在LCD上。換做u/cos II的話,就是建立3個任務,然后之間再有一些數據傳遞就可以了?

2019-04-04 06:36:23

跨時鐘域處理是 FPGA 設計中經常遇到的問題,而如何處理好跨時鐘域間的數據,可以說是每個 FPGA 初學者的必修課。如果是還在校生,跨時鐘域處理也是面試中經常常被問到的一個問題。這里主要介紹三種跨

2020-09-22 10:24:55

跨時鐘域處理是FPGA設計中經常遇到的問題,而如何處理好跨時鐘域間的數據,可以說是每個FPGA初學者的必修課。如果是還是在校的學生,跨時鐘域處理也是面試中經常常被問到的一個問題。在本篇文章中,主要

2021-07-29 06:19:11

跨時鐘域處理是什么意思?如何處理好跨時鐘域間的數據呢?有哪幾種跨時鐘域處理的方法呢?

2021-11-01 07:44:59

我無法訪問WebCase網站。如何獲得HW-USB-II-G平臺USB II和XC3S250E-4PQG208C Spartan FPGA的波動性聲明?謝謝。以上來自于谷歌翻譯以下為原文I am

2019-04-28 13:29:42

對多時鐘系統的同步問題進行了討論?提出了亞穩態的概念及其產生機理和危害;敘述了控制信號和數據通路在多時鐘域之間的傳遞?討論了控制信號的輸出次序對同步技術的不同要求,重點論述了常用的數據通路同步技術----用FIFO實現同步的原理及其實現思路

2012-05-23 19:54:32

親愛的朋友們, 我有一個多鎖設計。時鐘為50MHz,200MHz和400Mhz。如果僅使用400MHz時鐘并使用時鐘使能產生200Mhz和50Mhz時鐘域。現在我需要將信號從一個時鐘域傳遞到另一個

2019-03-11 08:55:24

跨時鐘域處理是 FPGA 設計中經常遇到的問題,而如何處理好跨時鐘域間的數據,可以說是每個 FPGA 初學者的必修課。如果是還在校生,跨時鐘域處理也是面試中經常常被問到的一個問題。這里主要介紹三種跨

2020-10-20 09:27:37

大型設計中FPGA的多時鐘設計策略利用FPGA實現大型設計時,可能需要FPGA具有以多個時鐘運行的多重數據通路,這種多時鐘FPGA設計必須特別小心,需要注意最大時鐘速率、抖動、最大時鐘數、異步時鐘

2020-04-26 07:00:00

實現數據傳遞需要做些什么?需要用到什么?怎么才能讓數據傳遞到另一端?服務端客戶端

2022-03-02 07:15:44

。雖然這樣可以簡化時序分析以及減少很多與多時鐘域有關的問題,但是由于FPGA外各種系統限制,只使用一個時鐘常常又不現實。FPGA時常需要在兩個不同時鐘頻率系統之間交換數據,在系統之間通過多I/O接口接收

2022-10-14 15:43:00

FPGA采用spartan 6 系列,現有個技術問題需要咨詢:FPGA采集10路串行同步信號,每路一根數據線一對差分時鐘線,時鐘最快可達40MHz,那么這10對時鐘線能否接到FPGA的普通IO上面

2017-12-08 14:52:58

嗨,我是FPGA的新手(也是Xilinx系列FPGA的新手),所以我想知道Xilinx Spartan-II(XC2S100)FPGA板中是否有內置/預編程的Verilog模塊或變量。這是因為我正在

2019-06-04 12:36:34

:LX:XC4VLX15,XC4VLX25,XC4VSX25,XC4VFX12Spartan?系列Spartan-II:所有Spartan-IIE:所有Spartan

2020-06-05 09:23:59

你好,我有一個用于VHART開發的SPARTAN II的舊FPGA設計。有沒有辦法使用當前的設計工具為SPARTAN II開發代碼?謝謝tower_dig.vhd 30 KB以上來自于谷歌翻譯以下

2019-06-17 09:23:59

`各位高手,請教下如何用隊列實現vi之間的數據傳遞,最好能給出個例子,我是初學者,謝謝`

2017-09-08 11:01:12

減少很多與多時鐘域有關的問題,但是由于FPGA外各種系統限制,只使用一個時鐘常常又不現實。FPGA時常需要在兩個不同時鐘頻率系統之間交換數據,在系統之間通過多I/O接口接收和發送數據,處理異步信號

2023-06-02 14:26:23

Multiple Clock System Design PLD設計技巧—多時鐘系統設計

Information Missing

Max+Plus II does

2008-09-11 09:19:41 25

25 單片機教程九:單片機數據傳遞類指令

單片機數據傳遞類指令

(3)以直接地址為目的操作數的指令

MOV direct,A 例: MOV 20H,A

2009-05-15 23:03:11 790

790

大型設計中FPGA的多時鐘設計策略

利用FPGA實現大型設計時,可能需要FPGA具有以多個時鐘運行的多重數據通路,這種多時鐘FPGA設計必須特別小心,需要注意最大時鐘速率

2009-12-27 13:28:04 645

645

賽靈思Spartan FPGA高清視頻參考設計,輕松實現“即插即用”

賽靈思公司(Xilinx)近日推出一款全新的消費視頻增強參考設計。該款參考設計基于一個低成本的Xilinx Sparta

2010-01-29 08:51:22 719

719 Spartan-3FPGA能以突破性的價位點實現嵌入式DSP功能。本文闡述了Spartan-3 FPGA針

2010-12-17 11:31:23 675

675

: Spartan-3E (50萬門,XC3S500E-4FG320C), CoolRunner-II (XC2C64A-5VQ44C)與Platform Flash (XCF04S-VO20C) 時鐘:

2011-01-18 16:23:32 110

110 為利用簡單的線纜收發器,實現中等數據率的串行數據傳輸,提出了一種基于電荷泵式PLL的時鐘數據恢復的方法。鑒相器由FPGA實現,用固定延時單元構成一條等間隔的延時鏈,將輸入信號經過每級延時單元后的多個輸出用本地的VCO時鐘鎖存,輸入信號的沿變在延時鏈

2011-03-15 12:39:34 90

90 通過Xilinx Spartan-6 FPGA 的Multiboot特性,允許用戶一次將多個配置文件下載入Flash中,根據不同時刻的需求,在不掉電重啟的情況下,從中選擇一個來重配置FPGA,實現不同功能,提高器件利用率,增加

2012-03-22 17:18:56 65

65 利用FPGA實現大型設計時,可能需要FPGA具有以多個時鐘運行的多重數據通路,這種多時鐘FPGA設計必須特別小心,需要注意最大時鐘速率、抖動、最大時鐘數、異步時鐘設計和時鐘/數

2012-05-21 11:26:10 1100

1100

NBP16 Xilinx Spartan-II PQ208 Rev1.01

2016-02-17 15:04:39 0

0 Memec Spartan II Demo Board Rev3,好東西,喜歡的朋友可以下載來學習。

2016-02-22 15:54:52 0

0 Spartan 3系列的FPGA原理圖,144針引腳

2016-06-03 16:16:53 13

13 時鐘設施提供了一系列的低電容、低抖動的互聯線,這些互聯線非常適合于傳輸高頻信號、最大量減小時鐘抖動。這些連線資源可以和DCM、PLL等實現連接。 每一種Spartan-6芯片提供16個高速、低抖動的全局時鐘資源用于優化性能。

2018-07-14 07:07:00 6504

6504

Spartan-6 FPGA Data Sheet

2017-10-24 08:39:19 21

21 PicoBlaze是8位微處理器,在Xilinx公司的Virtex、Spartan-II系列以上FPGA與CoolRunner-II系列以上的CPLD器件設計中以IP核的方式提供,使用是免費的?。常見的版本有KCPSM3和KCPSM6。其中KCPSM支持7系列的Xilinx FPGA。

2017-11-17 20:28:01 3437

3437

本演示介紹了 Spartan?-3A 入門套件如何讓您立即獲得 Spartan-3A FPGA 器件的節能模式,高速 I/O 選項,DDR2 SDRAM 存儲器接口,商用閃存配置支持,以及利用 Device DNA 實現的 FPGA/IP 保護等特性。

2018-05-22 13:45:01 2484

2484 了解如何描述Spartan-6 FPGA中的全局和I / O時鐘網絡,描述時鐘緩沖器及其與I / O資源的關系,描述Spartan-6 FPGA中的DCM功能。

2018-11-22 06:10:00 4862

4862 本文檔的主要內容詳細介紹的是spartan-6 FPGA的時鐘資源的用戶指南資料免費下載。

2019-02-15 16:39:07 27

27 Spartan-3an FPGA系列將領先、低成本的FPGA的最佳特性與廣泛密度范圍內的非易失性技術相結合。該系列結合了Spartan-3A FPGA系列的所有功能,以及系統閃存中的領先技術,用于配置和非易失性數據存儲。

2019-05-27 08:00:00 1

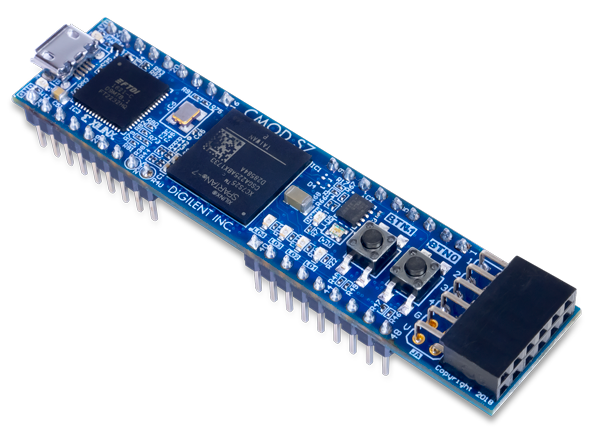

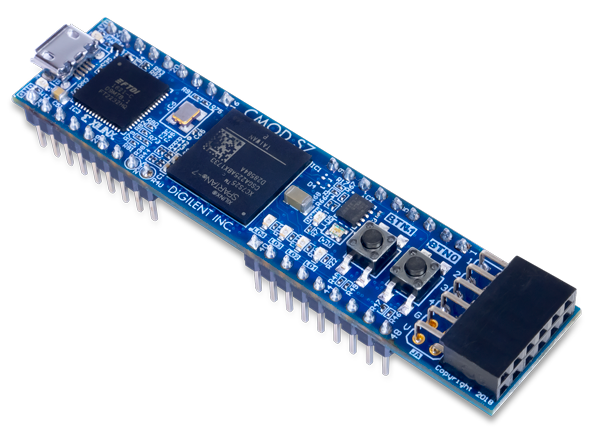

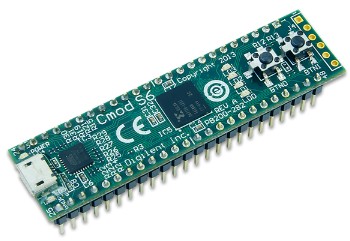

1 ,一個外部電源輸入和接地線路連接到100毫英寸間距內,使Cmod S7非常適合與面包板一起使用。它只有0.7英寸×3.05英寸,可以方便的開發嵌入式系統。該板還包括編程ROM,時鐘源,USB編程和數據傳輸電路,電源,LED和按鈕。

2019-11-14 15:55:53 2734

2734

DigilentCmod S6是一款基于Xilinx? Spartan?-6 LX4 FPGA芯片的小型的,48引腳DIP外形因素板。此板包括一個編程ROM,時鐘源,USB編程與數據傳輸電路,電源

2019-11-14 16:18:58 3469

3469

Spartan-6 FPGA 利用CCL 支持布線線路與邏輯單元之間的可配置互聯功能。Spartan-6 FPGA 是易失性器件- 電源移除時,不能保留原有配置。為了配置Spartan

2020-01-10 15:28:51 25

25 利用 FPGA 實現大型設計時,可能需要FPGA 具有以多個時鐘運行的多重數據通路,這種多時鐘FPGA 設計必須特別小心,需要注意最大時鐘速率、抖動、最大時鐘數、異步時鐘設計和時鐘/數據關系。設計過程中最重要的一步是確定要用多少個不同的時鐘,以及如何進行布線,本文將對這些設計策略深入闡述。

2021-01-15 15:57:00 14

14 減少很多與多時鐘域有關的問題,但是由于FPGA外各種系統限制,只使用一個時鐘常常又不現實。FPGA時常需要在兩個不同時鐘頻率系統之間交換數據,在系統之間通過多I/O接口接收和發送數據,處理異步信號,以及為帶門控時鐘的低功耗

2021-09-23 16:39:54 2763

2763 第9課:單片機數據傳遞類指令 2020/11/17

2021-11-20 11:51:06 0

0 Spartan-II主要包括CLBs,I/O塊,RAM塊和可編程連線(未表示出)。在spartan-II中,一個CLB包括2個Slices,每個slices包括兩個LUT,兩個觸發器和相關邏輯

2022-09-21 14:34:23 1049

1049 電子發燒友網站提供《在Spartan 6 FPGA上從頭開始實現全加器.zip》資料免費下載

2023-06-15 10:13:28 0

0 減少很多與多時鐘域有關的問題,但是由于FPGA外各種系統限制,只使用一個時鐘常常又不現實。FPGA時常需要在兩個不同時鐘頻率系統之間交換數據,在系統之間通過多I/O接口接收和發送數據,處理異步信號,以及為帶門控時鐘的低功耗

2023-08-23 16:10:01 336

336 域時,由于時鐘頻率不同,所以可能會產生元件的不穩定情況,導致傳輸數據的錯誤。此時我們需要采取一些特殊的措施,來保證跨時鐘域傳輸的正確性。 FPGA跨時鐘域通信的基本實現方法是通過FPGA內部專門的邏輯元件進行數據傳輸。發送方用一個邏輯電路

2023-10-18 15:23:51 578

578

電子發燒友App

電子發燒友App

評論