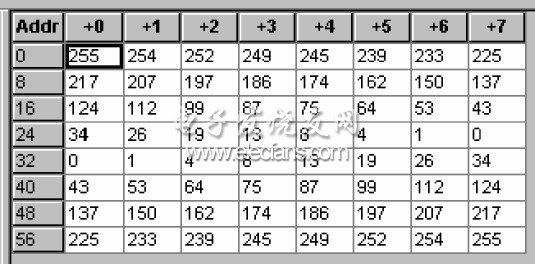

本設計相位累加器設定為32位,正弦表數據為8位,因此在ROM查找表里的容量為232×8=34,359,738,368(bits),在理論上這可以獲得精細的頻率分辨率,但是這么大容量的數據卻很難實現。

2022-06-21 10:54:35 5715

5715

信號發生器能夠產生頻率波形可調的信號輸出,目前僅限于1Hz~4999Hz頻率范圍,波形可選擇三角波,方波,鋸齒波,以及正弦波。本系統在Basys3上構建了一個簡易信號發生器。

2023-07-26 09:14:21 1676

1676

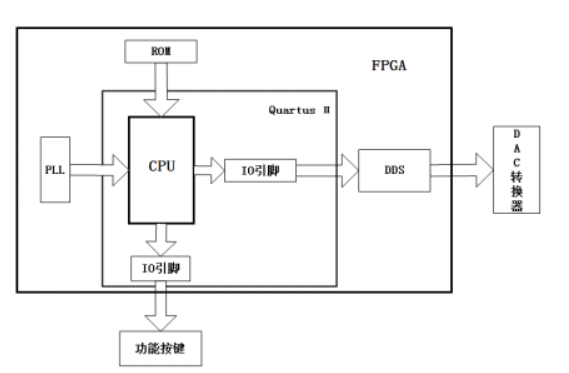

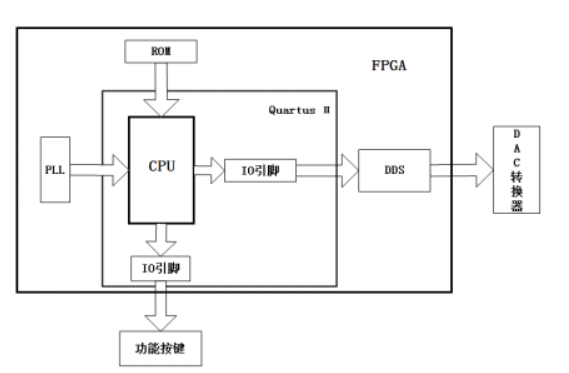

本設計以FPGA為控制核心,采用直接數字頻率合成(DDS)設計了一款信號可調的信號發生器,采用的FPGA是Altera公司研發的的Cyclnoe II系列,所選用的型號是EP4C6F17C8,外圍

2021-10-28 16:49:26

://bbs.elecfans.com/jishu_233968_1_1.html基于FPGA的信號發生器設計https://bbs.elecfans.com/jishu_229732_1_1.html

2012-07-19 10:40:57

FPGA數字信號發生器,怎么弄啊……跪求各路大神……

2013-04-18 13:38:22

前一段時間做信號發生器用的資料,僅供參考

2013-02-25 09:39:12

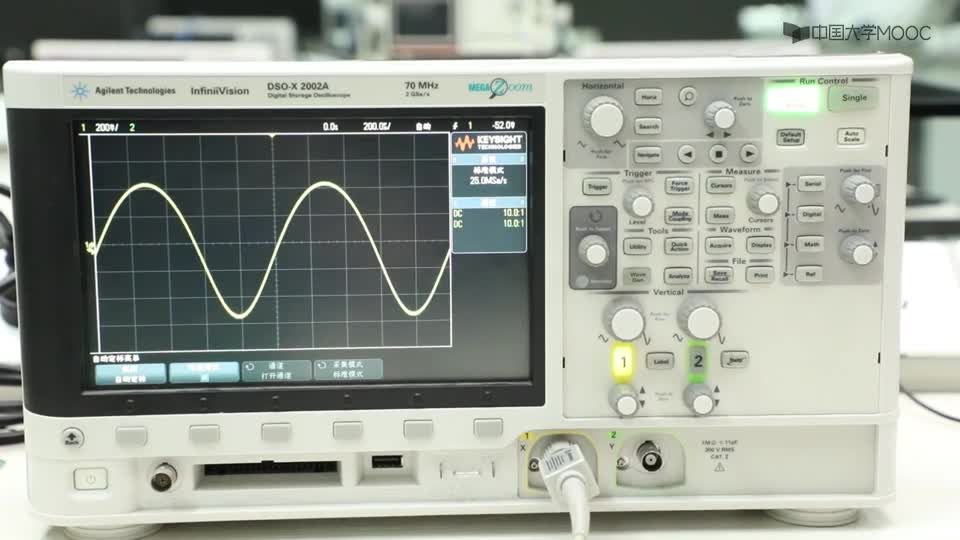

在晶體管共發射極電路調試中,信號發生器正弦波配置好后用示波器可以看到正確的正弦波形,但是把信號發生器接入到共發射極電路中的信號源中,則信號發生器沒有正弦波形輸出,這是怎么回事??? 請哪位高手幫忙解決一下,不勝感謝!

2012-11-06 17:45:50

想做一個信號發生器,使用什么方法做最優呢。求解求解~

2015-07-17 09:52:37

求助,這個信號發生器電路的設計原理是什么

2022-06-21 20:40:00

請問,信號發生器只能輸出有正有負的信號嗎?例如,我導入的峰峰值5V的信號,電壓范圍為0~5V,利用型號為AFG2021-SC的發生器輸出信號只能為-2.5~2.5V,可以調節嗎。

2018-01-02 11:28:09

信號發生器和DA轉換 FPGA案例教程

2019-08-17 09:01:48

信號發生器是是什么?信號發生器分為哪幾類?

2021-05-13 06:03:51

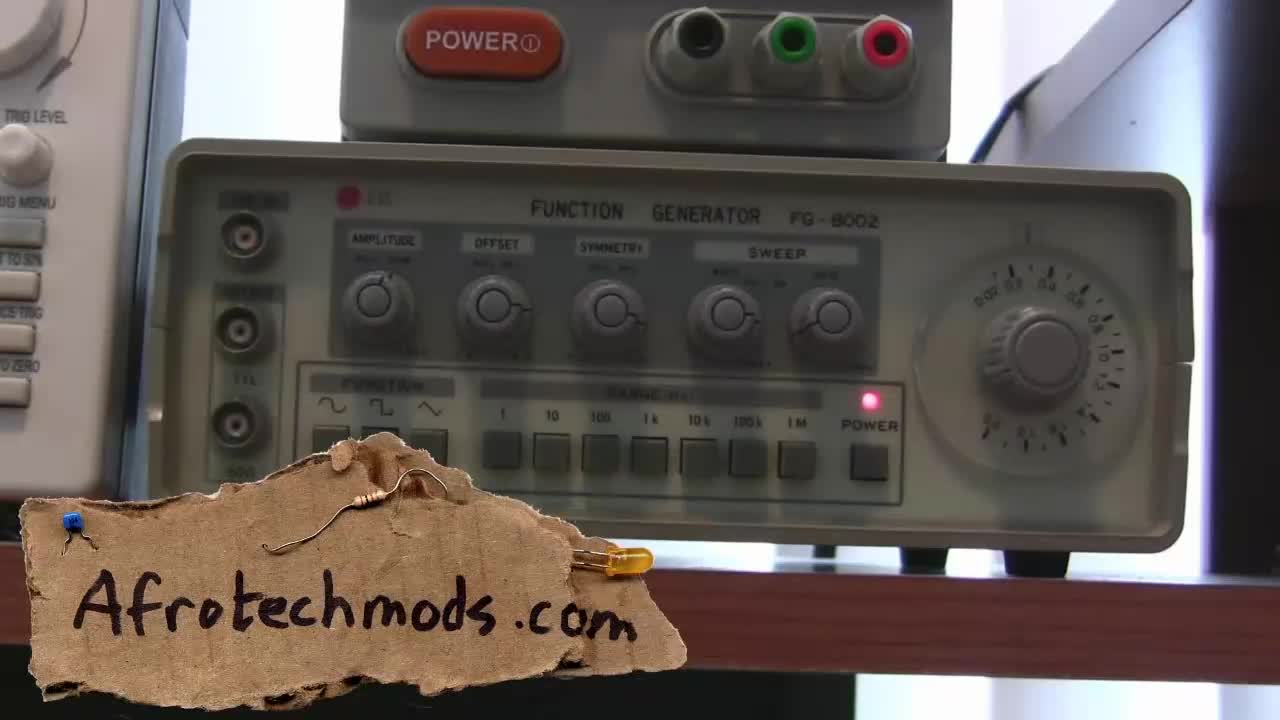

本文主要介紹信號發生器的基礎知識,首先介紹通用的信號發生器有哪些分類,并簡要說明了各種信號源的特點和作用,另外重點講解了信號發生器的主要指標,介紹了現有信號發生器一些特殊功能。關鍵詞:任意波形發生器、函數信號發生器、頻率分辨率、存儲深度

2019-06-04 07:52:41

基于labview的數字信號發生器設計

2012-05-18 19:01:42

請問一下這個信號發生器是產生什么信號的?和最開始那下振蕩是怎么來的??為什么沒產生信號?

2018-03-01 16:45:38

本帖最后由 eehome 于 2013-1-5 09:59 編輯

附件中是我的設計方案,希望各位大牛多多指導。

2012-05-11 21:04:10

詳情!DIY信號發生器方案資料:1、fpga信號發生器參考資料2、基于stc89c51和ADC0832的函數信號發生器3、基于LM324的簡易信號發生

2014-06-30 16:53:21

`對于信號發生器的設計,不論芯片的類型,只要所設計的邏輯單元夠用即可,還有就是內存要夠。好了,話不多說。直接來開始FPGA的信號發生器設計吧。直接上圖:該圖是quartus的開發環境,大家看下,感覺

2019-09-05 07:00:00

本帖最后由 Stark揚 于 2018-10-11 15:31 編輯

想請教各位,fpga設計的信號發生器的輸出脈沖在示波器中顯示的波形幅值特別低,請問這個幅值是與芯片的VCCIO口的電壓有關么,VCCIO電壓3.3v。這個幅值應該是3.3v的但是特別低,不知道是什么問題?

2018-10-11 11:17:41

利用FPGA實現信號發生器

2016-08-24 16:24:24

版本一:基于FPGA的信號發生器,四種波形可調,頻率相位可調,(1-hz)(幅度+-5V)正弦三角方波鋸齒這里使用了高速的DA模塊。所以是在數據發送的時候是并行發送的,至于輸出-+5是模塊自身集成

2022-04-06 18:31:10

脈沖波,經二階低通濾波和放大電路后即可得到所需波形信號。3.該多路信號發生器幅值分辨率高,頻率精度高,且具有良好的直流性能,各通道可獨立產生三角波、鋸齒波、正弦波、方波且輸出穩定求大神,講解講解思路,

2018-12-08 18:07:11

信號發生器又稱為波形發生器是一種常用的信號源并且廣泛應用于電子電路、通信、控制和教學實驗等領域的重要儀器之一。為了降低傳統函數信號發生器成本,改善信號發生器低頻穩定性。

2019-09-05 07:22:51

信號發生器種類很多,按是否利用頻率合成技術來分,可分為非頻率合成式信號發生器與頻率合成式信號發生器。其中頻率合成式信號發生器的頻率準確度和穩定度都很高,且頻率連續可調,是信號發生器的發展方向。頻率

2019-09-26 06:45:26

、帶插值為400ms/s的有效采樣率。滿足這樣要求的FPGA芯片和DA,現在不懂怎么選型,想買塊開發板來學習一下。這個采樣率是DA的采樣率不? 但是找了好久都沒有這樣的芯片,不是采樣率不滿足,就是幅值不滿足。

2019-03-07 06:35:13

現有開發板一塊,只是不知道VHDL的語言該如何寫。。。。

2013-03-17 19:42:35

求一個基于FPGA的DDS信號發生器設計,最好有DA模塊和相位累加器模塊的代碼。

2019-03-18 22:09:03

基于FPGA的雙路低頻信號發生器設計摘要 本設計是基于Altera公司的Cyclone II系列EP2C8Q208C8N芯片的雙路低頻信號發生器。系統應用FPGA內部特有的可配置IP核和鎖相環等

2018-08-23 15:32:05

硬件電路圖的連接關系。器件AD9709管腳原理圖信號FPGA管腳FPGA工程信號

2018-11-19 16:39:59

基于labview和fpga的信號發生器要求:【1】正弦波、方波、鋸齒波、三角波。【2】頻率、幅值、相位可調,調節步進值:頻率0.1,幅值0.1,相位1;【3】頻率最高:20k;峰值最高:3.3

2022-01-18 07:35:42

基于labview的信號發生器的設計

2013-12-27 20:41:12

DDS電路的工作原理是什么如何利用FPGA和DDS技術實現正弦信號發生器的設計

2021-04-28 06:35:23

DDS的工作原理和基本結構基于FPGA的DDS信號發生器的設計如何建立頂層模塊?

2021-04-09 06:46:42

信號發生器的系統構成部分AD9857結構與功能描述如何利用AD9857設計信號發生器

2021-04-14 06:27:38

信號發生器又稱信號源或振蕩器,在生產實踐和科技領域中有 著廣泛的應用。能夠產生多種波形,如三角波、鋸齒波、矩形波(含方波)、正弦波的電路被稱為函數信號發生器。

2019-11-11 08:07:57

`安捷倫信號發生器怎么產生的方波不是標準的方波,而是寬度發生變化的`

2020-10-24 12:12:17

本文在討論DDS的基礎上,介紹利用FPGA設計的基于DDS的信號發生器。

2021-05-06 09:54:10

怎么實現信號發生器系統的FPGA設計?

2021-09-30 06:35:31

m序列信號發生器由那幾部分組成?怎么實現m序列信號發生器的設計?

2021-05-10 06:09:23

介紹了DDS的發展歷史及其兩種實現方法的特點,論述了DDS的基本原理,并提出一種基于FPGA的DDS信號發生器的設計方法,使DDS信號發生器具有調頻、調相的功能,最后對其性能進行了分析。實驗表明該系統具有設計合理、可靠性高、結構簡單等特點,具有很好的實用價值。

2021-05-11 06:58:58

)。DDS是開環系統,無反饋環節,輸出響應速度快,頻率穩定度高。因此直接數字頻率合成技術是目前頻率合成的主要技術之一。文中的主要內容是采用FPGA結合虛擬儀器技術,進行DDS信號發生器的開發。

2019-09-29 08:08:12

怎樣去設計一種基于FPGA的正弦信號發生器?如何對基于FPGA的正弦信號發生器進行仿真?

2021-09-28 06:31:34

前言用FPGA做正弦信號發生器是我上大學期間在實驗室里做的,主要用的ROM-IP和DA數模轉化芯片,將數字信號轉為模擬信號后,通過示波器進行顯示。我記得當時用FPGA做了正弦、三角波、方波信號,然后

2021-07-26 07:19:19

哪個大神能提供一下E題的第五問的信號發生器的FPGA的程序,用的是STM32F1。提供一個標準矩形脈沖信號發生器,要求:a) 頻率為1MHz,誤差的絕對值不大于0.1%;b) 脈寬為100ns,誤差

2016-07-27 21:04:06

以前學習過一段時間stm32,算是入門了,現在又學了點fpga,想要做一個基于32和fpga的信號發生器,但是不知道從何下手,在網上查資料也是說得很籠統,不能給我以明示,不知道這里有沒有哪位做個或會做的,希望能指點一下

2019-04-22 23:05:44

給點思路,給點建議,大神在哪里

2014-06-14 18:31:16

本文介紹基于FPGA 和DDFS 技術,應用Altera 公司的FPGA 開發工具DSP Builder 設計數字移相信號發生器,該數字移相信號發生器的頻率、相位、幅度均可預置,分辨率高,精確可調。且可分

2009-12-18 11:59:54 44

44 根據直接數字合成器的基本原理,給出了基于FPGA 的直接數字合成器的設計與實現,利用FPGA有效地擴展了輸出波形的頻率范圍,實現了數字移相信號發生器。該信號發器主要采用了

2009-12-26 16:34:58 36

36 正弦信號發生器(A題)

一、任務 設計制作一個正弦信號發生器。

二、要求1、基本

2010-04-16 10:25:59 90

90 根據直接數字合成器的基本原理,給出了基于FPGA的直接數字合成器的設計與實現,利用FPGA有效地擴展了輸出波形的頻率范圍,實現了數字移相信號發生器。該信號發生器主要采用了直接

2010-07-21 17:30:47 69

69 為配合地震計電磁信息采集系統對地震計進行標定,設計一款基于FPGA的地震計標定 信號發生器 。以Altera EP2C8T144C8型 FPGA和16位串行DAC芯片DAC8560為核心,利用直接數字頻率合成技術、m序

2011-08-05 14:33:47 49

49 本文在介紹差分跳頻G函數算法原理基礎之上,對短波差分跳頻信號發生器進行了基于FPGA的整體系統優化設計,并分別在軟件和硬件環境下進行了仿真與實現。

2011-08-13 15:04:11 1535

1535

以FPGA芯片為載體,通過QuartusII的LPM_ROM模塊和VHDL語言為核心設計一個多功能 信號發生器 ,根據輸入信號的選擇可以輸出遞增鋸齒波、遞減鋸齒波、三角波、階梯波和方波等5種信號,通

2011-08-15 11:00:59 83

83 為了降低傳統函數信號發生器成本,改善函數信號發生器低頻穩定性,本文結合FPGA和51單片機設計并實現了產生以0.596Hz頻率精度各種函數信號。函數信號頻率、波形、幅度由51單片機控

2012-03-22 12:08:01 125

125 設計采用Altera公司CycloneII系列EP2C5Q208作為核心器件,采用直接數字頻率合成技術實現了一個頻率、相位可控的基本信號發生器。該信號發生器可以產生正弦波、方波、三角波和鋸齒波四種波形。仿真及硬件驗證的結果表明,該信號發生器精度高,抗干擾性好,此設計方案具有一定的實用性。

2013-01-22 14:45:33 472

472 為了提高數字調制信號發生器的頻率準確度和穩定度,并使其相關技術參數靈活可調,提出了基于FPGA和DDS技術的數字調制信號發生器設計方法。利用Matlab/Simulink、DSP Builder、QuartusⅡ 3個

2013-04-27 16:50:59 183

183 2015-04-17 09:32:17 6

6 本專題匯集了四十種DDS信號發生器各部分資料,包括信號發生器原理,DDS芯片及應用,信號發生器電路圖及DDS信號發生器設計,為你免除大量自行搜索的時間,讓你深入了解DDS信號發生器。

2015-06-23 10:41:36

基于FPGA的正弦信號發生器的 技術論文

2015-10-30 10:39:05 20

20 虛擬信號發生器基于labview的虛擬信號發生器的設計

2016-01-05 16:49:31 188

188 脈沖信號發生器是 信號發生器的一種。信號發生器按信號源有很多種分類方法,其中一種方法可分為混和信號源和邏輯信號源兩種。其中混和信號源主要輸出模擬波形;邏輯信號源輸出數字碼形。混和信號源又可分為函數

2017-10-26 17:09:54 20777

20777

FPGA和51單片機信號發生器設計

2017-10-31 09:15:37 22

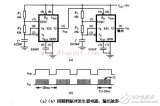

22 基于運放的信號發生器精度低且穩定性和可調節性差,而基于DDS的信號發生器則成本高、電路復雜。為此提出了基于FPGA+PWM的多路信號發生器設計方法。該方法硬件上無需DAC與多路模擬開關,由FPGA產生調制輸出波形信號所需的PWM脈沖波,經二階低通濾波和放大電路后即可得到所需波形信號。

2017-11-18 09:42:01 6332

6332

本文檔內容介紹了基于fpga實現信號發生器,供參考

2018-04-20 15:23:35 65

65 本文首先介紹了脈沖信號發生器的工作原理,其次詳細的闡述了脈沖信號發生器的設計案例。

2018-08-21 17:29:39 18636

18636 本文首先介紹了信號發生器的功能以及作用,其次介紹了四種信號發生器的用途,最后闡述了四種信號發生器的應用以及實例。

2018-08-21 18:33:21 33199

33199 針對信號發生器對輸出頻率精度高和幅值可調的要求,采用直接數字頻率合成(DDS)技術,提出一種基于FPGA的幅值、頻率均可調的、高分辨率、高穩定度的信號發生器設計方案。采用AT89S52單片機為控制器

2018-11-06 19:35:28 21

21 數字信號發生器是數字信號處理中不可缺少的調試設備,在生產生活中的應用非常廣泛。本文所設計的內容就是基于AItera公司的現場可編程門陣列(FPGA)實現數字信號發生器的設計,本設計中應用VHDL硬件描述語言進行描述,使該數字信號發生器可以產生正弦波、方波、三角波、鋸齒波四個獨立的波形。

2018-11-13 16:40:59 33

33 在這篇文章中,小編將對信號發生器在靈敏度調節方面的應用予以介紹,并告訴大家如何選擇一款合適的信號發生器,在文章最后還將對脈沖信號發生器加以簡單介紹。如果你對本文內容具有興趣,不妨繼續往下閱讀哦。

2021-02-09 17:45:00 4800

4800 論述了DDS的基本原理,給出了利用FPGA實現基于DDS的2ASK/2FSK信號發生器的設計方法,重點介紹了其原理和電路,最后給出了基于.FPGA設計的實驗結果.

2021-03-24 09:12:00 19

19 一、如何選擇一款合適的信號發生器? 據西安安泰信號發生器維修中心小編所知,函數/任意波形發生器是一種產生標準函數信號,并可以產生任意波形的儀器。函數/任意波形發生器的選型需要考慮幾個重要的參數,包括

2022-01-12 18:26:44 2578

2578 脈沖發生器: 顧名思義,脈沖發生器是一種產生脈沖的信號發生器。這些信號發生器通常采用邏輯脈沖發生器的形式,可以產生具有可變延遲的脈沖,有些甚至提供可變上升和下降時間。

2022-08-02 15:48:42 3762

3762 本設計以FPGA為控制核心,采用直接數字頻率合成(DDS)設計了一款信號可調的信號發生器,采用的FPGA是Altera公司研發的的Cyclnoe II系列,所選用的型號是EP4C6F17C8,外圍

2022-12-22 11:08:05 5

5 在日常實驗中信號發生器經常和功率放大器一起搭配使用,很多人都知道信號源,也就是信號發生器,但是對信號發生器的作用和組成都不太了解。安泰電子為大家帶來信號發生器的科普常識,希望大家對信號發生器能夠

2023-02-17 10:55:28 5

5 ?基于運用EDA技術,以FPGA器件為,用Verilog HDL硬件描述語言來設計各個功能模塊,采用DDS直接數字頻率合成技術設計信號發生器,通過CPU控制每個采樣點的輸出間隔來控制輸出波形的頻率

2023-04-14 15:15:02 672

672 信號發生器的占空比是什么 信號發生器占空比怎么設置? 信號發生器的占空比是指方波波形中高電平和低電平的時間比例。它是描述信號發生器輸出方波的高低電平持續時間的一個重要參數。在數字電子技術和通信系統

2023-12-21 14:02:26 996

996

電子發燒友App

電子發燒友App

評論