一、引 言

近年來,現場可編程門陣列(FPGA)技術以其獨有的優勢,在電子設計領域得到越來越廣泛的應用。FPGA除具有集成度高、體積小、功耗低、電路簡單、可靠性高等優點外,還有自身突出的優點,即“現場可編程性”,用戶可以很方便地通過相應的軟件,在較短時間內對FPGA內部邏輯反復設計或修改,直到滿意為止。這就大大縮短了開發周期,提高了最終產品的性能。

以太網是最廣泛使用的網絡標準。它成為最受歡迎的技術,不僅因為其在市場上最低的NIC(網絡接口卡)和HUB端口價格,還因為它具有維護簡單、易于擴充等優點。

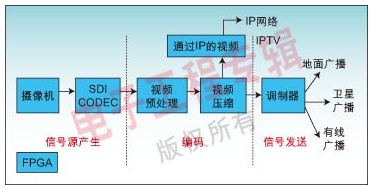

本文介紹的視頻廣播接收系統是基于標準以太網(10 Mbps)和快速以太網(100 Mbps)的系統。由于系統的主要部分采用了FPGA設計技術,使得系統的成本較低和開發周期較短,而且由于前端采用的是具有10M/100M兼容的芯片,并同時支持兩種特性的以太網(全雙工和半雙工),有助于實現全雙工和半雙工以太網之間的無縫連接,從而使得該系統具有廣闊的應用前景和實用性。

二、基本原理

系統實現中涉及到網絡方面的許多相關技術和各種相關的協議、標準,下面作一簡要介紹。

1.CSMA/CD協議

以太網用載波偵聽多路訪問/沖突檢測(CSMA/CD)作為它的媒體訪問控制協議,CSMA/CD定義了以太網節點為傳輸數據如何獲得對網絡媒體的訪問。其工作過程如下:

?? (1)如果介質空閑,則傳輸數據,否則,轉(2);

(2)如果介質忙,則堅持偵聽,直到介質空閑,立即傳送數據;

(3)如果在傳送過程中,檢測到沖突發生,發送一個短的阻塞碼,以確保讓所有終端都檢測到沖突發生,然后停止發送;

(4)發送完阻塞碼后,等待一個隨機時間,再試圖重新發送,即轉(1)。

目前,實際使用較多的沖突檢測方法是終端發送器把數據發送到線纜上,終端接收器又把數據接收回來和發送的數據比較,判別是否一致,若一致,沒有沖突;若不一致,表示沖突發生。

2.以太網幀格式

當應用程序用UDP(TCP)傳送數據時,數據被送入協議棧中,然后逐個通過每一層直到被當作一串比特流送入網絡,其中每一層對收到的數據都要增加一些首部信息(有時還要增加尾部信息)。UDP傳給IP的數據單元稱作UDP報文段或簡稱為UDP段,IP傳給網絡接口層的數據單元稱作IP數據報。

在OSI模型中,數據鏈路層傳輸的數據單位是幀。同樣,以太網CSMA/CD也是通過幀來發送實際數據的。以太網802.3u的MAC子層的幀結構中,前導碼用于物理信號的同步,為7個字節的10101010序列和1個字節的10101011序列;目的地址和源地址使用的是MAC地址,前3個字節稱為Block ID,它標志生產設備的廠家并由IEEE賦值;后3個字節稱為設備ID,它由廠家賦值,而且總是唯一的;數據長度指要傳送的數據的總長度;數據和填充字符可以從0到1 500字節不等,若實際數據小于所需的最小長度,MAC將追加一些可變的填充字符(PAD),以維持64字節的最小幀規模。若數據比1 500字節長,則更高層(一般是第三層)將把數據字段分成不同的幀進行傳送;幀校驗用來確保進行正確的傳送,循環冗余校驗(CRC)用來進行有效幀的檢查。在以太網數據包的數據部分,包含了各種上層協議的首部。在本文的系統中,包含了IP首部和UDP首部。

3.介質無關接口(MII)

??? MII是一個用于互連控制器和收發器的全新介質無關接口,它是100 Mbit/s快速以太網開發工作的一個組成部分。此接口提供了新的物理連接機制以及控制器和收發器的功能劃分。該接口主要由以下一些信號組成:

??? (1)發送信號

包括半字節寬(Nibble-wide)的發送數據信號,加上相關的發送時鐘、發送允許信號和發送差錯信號。數據用時鐘同步,時鐘率是數據率的1/4 (即100 Mbit/s以太網用25 MHz的時鐘),發送信號用于將數據從控制器移動到收發器,然后編碼并發送到LAN上。

??? (2)接收信號

包括半字節寬的接收數據,加上相關的接收時鐘、接收數據有效信號和接收差錯信號。數據用時鐘同步,時鐘率是數據率的1/4。接收信號用于將解碼的數據從收發器移動到控制器。

??? (3)以太網控制信號

這些信號是由收發器生成的載波偵聽和沖突檢測信號,用于控制器做介質訪問控制。它們只用于半雙工模式,在全雙工模式中被忽略。

??? (4)管理信號

包括一個串行管理I/O信號和相關的時鐘信號。用于在控制器和收發器之間雙向交換配置和控制的管理信息。

三、系統設計

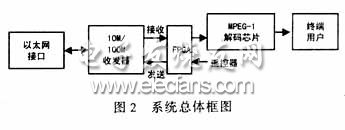

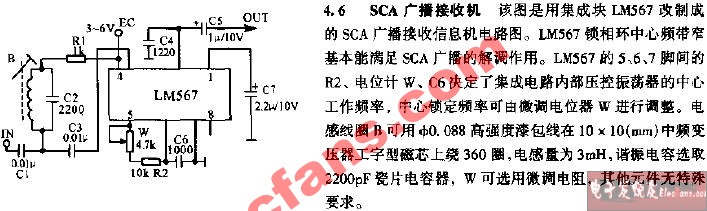

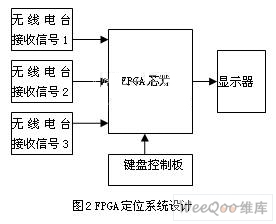

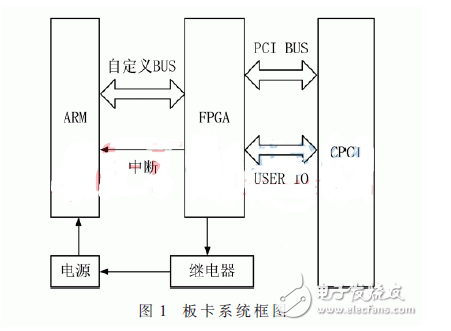

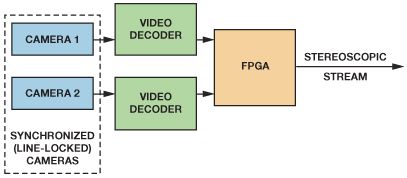

?? 該系統實現的總體框圖如圖2所示。

其中以太網接口采用的是傳統的RJ45接口,10M/100M收發器可以采用DM9101 單片實現,FPGA部分采用的是Xilinx公司的Spartan II系列的芯片,MPEG-1解碼芯片采用了C-Cube公司的解碼芯片。10M/100M收發器到FPGA之間采用MII標準的接口,FPGA到 MPEG-1解碼芯片之間采用I2S形式的接口。

1.DM9101

DM9101是一個物理層的、單片、低功耗的100Base-TX和10Base-T操作的轉換器。在介質這一邊,它既為用于100Base -TX快速以太網的非屏蔽雙絞線對(5類同軸電纜)提供一個直接的接口,也為用于10Base-T以太網的UTP5/UTP3提供直接的接口。通過 IEEE802.3u介質無關接口(MII),DM9101可以與介質接入控制(MAC)層相連接,確保了在不同生產商的產品之間的高度互操作性。

該芯片集成了MII標準接口、100Base-TX發送/接收器、10Base-T發送/接收器、自動協商、沖突檢測、載波偵聽、4B5B編/解碼器、加/解擾器、串口和并口之間的轉換等功能。

由于采用了MII標準接口,使得設計者可以通過該接口的管理信號線對該芯片的寄存器進行設置,從而完成對10 Mbps和100 Mbps兩種速率的選擇,突出了設計的靈活性。

2.FPGA設計

??? 由于要使數據能在以太網上傳輸,服務器端的發送程序應該把要傳輸的數據進行打包(或封裝)。本系統中所要傳輸的數據為視頻數據(VCD數據),而VCD數據一般是以dat格式存放在光盤中的。因而在接收端應對接收到的數據包進行解包,并同時完成數據格式轉換的功能,使得送到MPEG-1解碼芯片的數據格式為dat格式的數據,從而進行解碼,最后用普通的電視機就能夠接收。

因而該部分主要要實現的功能是:先完成對接收到的以太網數據幀進行解包,取出封裝在以太網數據幀中的數據部分,然后再分別解IP數據包和UDP數據包,把真正的具有VCD播放格式的數據取出來,經過一個先進先出(FIFO)緩沖器輸出到MPEG-1解碼芯片進行解碼。其中在解包的過程中,要對數據進行校驗,校驗正確的數據包才進行傳送,對于校驗不正確的數據包采用了直接丟棄的方法,所采用的校驗算法是循環冗余校驗算法(CRC)。

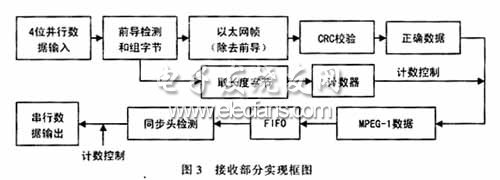

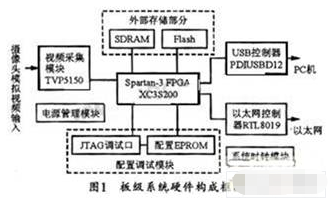

設計框圖如圖3所示。

?

(1)前導檢測:當系統檢測到連續出現了15個nibble的1010,同時隨后的一個nibble為1011時,說明一個以太網數據幀開始了,應該對該部分的數據作進一步的處理。

(2)組字節:由于從DM9101芯片出來的數據信號是以一次四位元組(nibble)的形式傳輸的,因而要對它進行組字節操作,每2個nibble組成一個字節,具體操作過程依據的是MII幀結構中的字節組成格式進行。

(3)CRC校驗:對以太網幀中的目的地址、源地址、長度、數據進行CRC校驗,并與幀的最后四個字節進行比較,如果一致,即為正確的以太網數據;若不一致,則丟棄這一幀。

(4)MPEG-1數據:取出以太網幀中的長度字節的值,用這個值來預置一個計數器,從而對數據進

行計數控制,取出其中的MPEG-1格式的有效數據。

(5)FIFO:由于普通的以太網的數據傳輸速率是10

Mbps或100 Mbps,而進行MPEG-1解碼時的速率一般為1.5 Mbps左右,因而要對數據流進行速率調整。該FIFO直接利用了Spartan II系列芯片內部的存儲模塊進行緩存。

(6)同步頭檢測:dat格式的數據幀有一個同步頭為:00FFFFFFFFFFFFFFFFFFFF00(十六進制),當檢測到該同步頭時,表明一個dat數據幀開始了,應將其后的數據連同該同步頭信息一起輸出至解碼芯片。

(7)串行輸出:把最后得到的數據轉換為串行數據,并以I2S的格式將數據和時鐘等信號輸出到 MPEG-1解碼芯片中進行解碼。

四、仿真結果

1.組字節仿真結果

數據從2個nibble組成一個字節的仿真結果如圖4所示。其中,CLK信號是25 MHz的時鐘信號,DA是由4位數據組成的數據信號,它們由DM9101芯片輸出;DATA為組成字節后的8位數據信號,CLK—B是由CLK信號二分頻所得到的Byte時鐘信號。

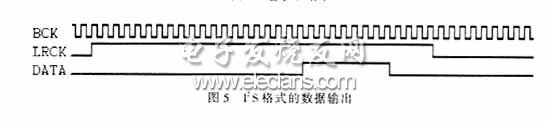

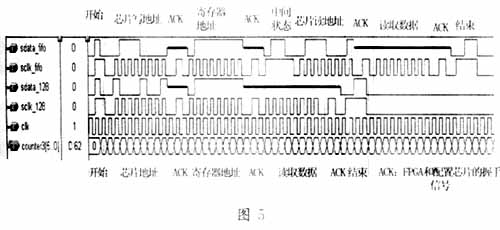

2.I2S格式仿真結果

以I2S格式輸出的數據的仿真結果如圖5所示。仿真中采用的格式是:32位BCK,MSB最先,右通道為低電平。其中BCK是位時鐘信號,LRCK是左右時鐘選擇時鐘,DATA是VCD格式的MPEG-1視/音頻數據。

?

?

五、小 結

本系統所采用的FPGA芯片為Xilinx公司的Spartan II系列芯片,用Foundation軟件工具開發。設計輸入完成后,進行整體的編譯和邏輯仿真,然后進行轉換、布局、延時仿真生成配置文件,最后下載至 FPGA器件,實現其硬件功能。由于系統的很多功能由一塊FPGA實現,外圍器件很少,所以系統體積小、可靠性高,且器件的可編程性使得系統功能易于完善。仿真結果表明,各信號的邏輯功能和時序配合完全達到了設計要求。

電子發燒友App

電子發燒友App

評論