,被賦值對象會比賦值對象差一個時鐘周期。 有了上述理解之后,我們就很容易明白為什么阻塞賦值的對象會立即發(fā)生改變,在fpga中我們多接觸到的是時序電路,并不希望被賦值對象立即改變,所以有對于組合電路而言,常用阻塞賦

2017-09-19 18:32:43 11967

11967 來源:《Verilog數(shù)字系統(tǒng)設(shè)計(夏宇聞)》 阻塞和非阻塞賦值的語言結(jié)構(gòu)是Verilog 語言中最難理解概念之一。甚至有些很有經(jīng)驗的Verilog 設(shè)計工程師也不能完全正確地理解:何時使用非阻塞

2021-08-17 16:18:17 6000

6000 FPGA關(guān)于pin交換xxxxxxxxxxxxxxx

2014-05-22 08:58:20

,被賦值對象會比賦值對象差一個時鐘周期。有了上述理解之后,我們就很容易明白為什么阻塞賦值的對象會立即發(fā)生改變,在fpga中我們多接觸到的是時序電路,并不希望被賦值對象立即改變,所以有對于組合電路而言

2017-04-05 09:53:11

:Wake_up_interruptible(&q); 輪詢操作 輪詢的概念與作用使用非阻塞I/O的應(yīng)用程序通常會使用select()和poll()系統(tǒng)調(diào)用查詢是否可對設(shè)備進(jìn)行無阻塞的訪問。select

2018-07-09 08:19:59

:Wake_up_interruptible(&q); 輪詢操作 輪詢的概念與作用使用非阻塞I/O的應(yīng)用程序通常會使用select()和poll()系統(tǒng)調(diào)用查詢是否可對設(shè)備進(jìn)行無阻塞的訪問。select

2018-07-04 07:23:24

ip1829a 是一種無阻塞、存儲轉(zhuǎn)發(fā)結(jié)構(gòu)的交換機(jī)控制器,它構(gòu)建了24端口10 / 100mbps 的快速以太網(wǎng) MAC 和物理層,5端口的吉比特以太網(wǎng) MAC,包括4端口 rgmii / mii

2019-11-18 10:01:15

最近公司數(shù)據(jù)庫同步機(jī)制常發(fā)生阻塞,時不時的導(dǎo)致PCB工程系統(tǒng)卡死現(xiàn)象,只有找到阻塞源頭并處理掉,才以消除阻塞,但數(shù)據(jù)庫中查看會話阻塞是通過二維表方式展示的父子會話進(jìn)程ID的,是很難清楚的展示各會話

2019-08-08 06:53:13

各位。我發(fā)送有關(guān)是否在 MCU 和 MC33HB2000 之間的 SPI 線上插入阻尼電阻 1kohm 的詳細(xì)波形數(shù)據(jù)。測試條件)休眠喚醒時,初始化100ms后運(yùn)行15秒SPI 頻率 500 kHz,最大電機(jī)電流 1.5A。SLK線有無阻尼電阻造成差異的原因是什么?

2023-03-31 07:39:46

Verilog阻塞和非阻塞原理分析在Verilog語言最難弄明白的結(jié)構(gòu)中“非阻塞賦值”要算一個。甚至是一些很有經(jīng)驗的工程師也不完全明白“非阻塞賦值”在仿真器(符合IEEE標(biāo)準(zhǔn)的)里是怎樣被設(shè)定執(zhí)行

2009-11-23 12:02:57

如果一個任務(wù)阻塞后這個任務(wù)的數(shù)據(jù)會不會丟失

2023-10-13 07:05:36

一般情況下串口通信中read()函數(shù)都是阻塞的。當(dāng)然也可以通過設(shè)置文件等方法把串口設(shè)為非阻塞的。這里就有一個問題,當(dāng)串口設(shè)置為阻塞狀況下,如果讀不到數(shù)據(jù)程序應(yīng)該掛起。這種所謂的讀不到數(shù)據(jù)是指讀不到

2011-07-14 15:57:26

,說selece函數(shù)沒有定義,頭文件也找不到。 不知道6748有沒有建立線程的方法,或者別的無阻塞接收網(wǎng)絡(luò)信息的方法?

2019-05-05 11:19:58

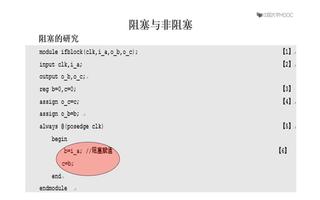

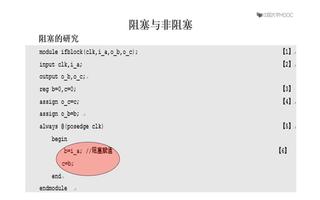

阻塞賦值與非阻塞賦值原理分析實(shí)驗?zāi)康模赫莆?b class="flag-6" style="color: red">阻塞賦值與非阻塞賦值的區(qū)別實(shí)驗平臺:無實(shí)驗原理:阻塞賦值,操作符為“=”,“阻塞”是指在進(jìn)程語句(initial和always)中,當(dāng)前的賦值語句阻斷了其后

2016-12-25 01:51:24

移位寄存器:如果把上述代碼中的兩個賦值語句相互交換,如下所示,結(jié)果和上面是一樣的。所以在一個begin---end中的非阻塞語句并不會因為放置的位置不同,出現(xiàn)不同的結(jié)果。關(guān)于非阻塞的例子,分析的貌似蠻

2016-11-03 20:26:38

本文和設(shè)計代碼由FPGA愛好者小梅哥編寫,未經(jīng)作者許可,本文僅允許網(wǎng)絡(luò)論壇復(fù)制轉(zhuǎn)載,且轉(zhuǎn)載時請標(biāo)明原作者。阻塞賦值,操作符為“=”,“阻塞”是指在進(jìn)程語句(initial和always)中,當(dāng)前

2020-02-24 20:09:13

阻塞與非阻塞作者:小黑同學(xué)一、 概述1、阻塞賦值對應(yīng)的電路往往與觸發(fā)沿沒有關(guān)系,只與電平的變化有關(guān)系。阻塞賦值符號“=”。2、非阻塞賦值對應(yīng)的電路結(jié)構(gòu)往往與邊沿觸發(fā)有關(guān)系,只有在觸發(fā)沿時才有可能發(fā)生賦值的情況。非阻塞賦值符號“

2020-04-24 14:49:45

本帖最后由 小梅哥 于 2016-1-18 12:51 編輯

大家好,今天,小梅哥繼續(xù)連載本人精心錄制和編輯的FPGA學(xué)習(xí)系列教程——《小梅哥FPGA設(shè)計思想與驗證方法視頻教程》。教程充分考慮

2015-09-24 14:02:15

清楚、誤碼少。 二、全繩路無阻塞, 國威集團(tuán)電話 ,那么模擬交 模擬交流機(jī)、數(shù)模混合機(jī)、數(shù)字程控交換機(jī)的差別 (1)數(shù)字程控交流機(jī)和模擬交換機(jī)的差別,數(shù)字程控交換機(jī)和模仿交換機(jī)的差別,數(shù)字程控交換

2016-12-14 17:16:52

大家好。我是菜鳥,有個問題希望大神可以幫我解決。是這樣的,我現(xiàn)在需要將一個數(shù)字信號處理的Matlab代碼用FPGA實(shí)現(xiàn),代碼的數(shù)據(jù)量很大,達(dá)到幾千個浮點(diǎn)數(shù)。在采用模塊化設(shè)計時,如何在模塊間進(jìn)行這些大量數(shù)據(jù)的交換,即如何把一個模塊的處理結(jié)果交給下個模塊?麻煩大神了

2016-05-15 17:24:20

初學(xué)DSP 想請教一下各位大神,怎么使F2812與FPGA進(jìn)行數(shù)據(jù)交換呢?

2013-12-07 11:12:30

利用FPGA自帶的IP核實(shí)現(xiàn)雙口RAM用于2片MCU進(jìn)行數(shù)據(jù)交換時多次讀數(shù)據(jù)后RAM中數(shù)據(jù)變?yōu)榱?,是什么意思,打什么幫幫忙!!!!!!!!!!!!!!

2018-01-15 16:22:16

FPGA?外圍的數(shù)據(jù)傳輸帶寬以及存儲器帶寬。但是在 FPGA 內(nèi)部,可編程邏輯部分隨著工藝提升而不斷進(jìn)步的同時,內(nèi)外部數(shù)據(jù)交換性能的提升并沒有那么明顯,所以 FPGA 內(nèi)部數(shù)據(jù)的交換越來越成為數(shù)據(jù)傳輸?shù)钠款i

2020-09-07 15:25:33

基于FPGA的數(shù)據(jù)無阻塞交換設(shè)計方案,不看肯定后悔

2021-04-29 06:48:07

如何去實(shí)現(xiàn)UART阻塞方式收發(fā)數(shù)據(jù)呢?如何去實(shí)現(xiàn)UART中斷方式收發(fā)數(shù)據(jù)呢?

2021-12-08 06:50:02

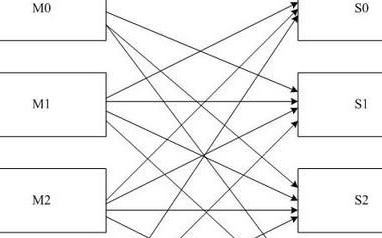

隨著FPGA和大規(guī)模集成電路的發(fā)展,數(shù)據(jù)交換的實(shí)現(xiàn)有了新的方法。

2019-08-16 06:11:26

本文設(shè)計了一個基于SRAM的交換矩陣的輸入端口,該設(shè)計有效的消除了輸入排隊鏈頭阻塞的問題,極大地提高交換開關(guān)的利用率,將輸入端口數(shù)據(jù)報文存放在片外SRAM中,可以顯著降低交換芯片的面積,提高虛擬隊列

2021-05-19 06:39:10

請教各位大神!是否可以通過FPGA內(nèi)核配置的雙口RAM,實(shí)現(xiàn)FPGA與DSP之間的數(shù)據(jù)交換?可以的話怎么實(shí)現(xiàn)?怎么設(shè)置FPGA的內(nèi)核RAM?如何連接DSP的外部存儲器XINTF的引腳和FPGA的引腳?謝謝!

2017-12-07 15:44:03

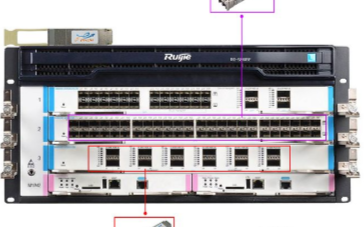

核心交換機(jī)采用模塊化結(jié)構(gòu),以適應(yīng)復(fù)雜的網(wǎng)絡(luò)環(huán)境和網(wǎng)絡(luò)應(yīng)用,超大容量的背板帶寬和線速的轉(zhuǎn)發(fā)速率可以有效地保證數(shù)據(jù)的無阻塞傳輸。

2020-03-26 09:03:39

我們這塊板子是用于圖像高速處理,ARM與FPGA進(jìn)行高速的數(shù)據(jù)交換,設(shè)計想法是在ARM與FPGA之間設(shè)計一塊兒存儲體作為二者之間通信的數(shù)據(jù)緩存。可是ARM的外部存儲的控制只有2個,一個是DDR用于

2018-05-15 01:53:19

想做一塊基于TMS320C6678的16路AD采集數(shù)據(jù),要求5MHz的采樣率,采用DSP+FPGA的模式,DSP與FPGA之間用SRIO方式連接,請問一下需要采樣tsi578交換機(jī)嗎?具體有什么方法?

2019-01-10 11:28:35

。交換機(jī)應(yīng)當(dāng)能夠?qū)崿F(xiàn)線速交換,即交換速率達(dá)到傳輸線上的數(shù)據(jù)傳輸速度,從而最大限度地消除交換瓶頸。對于三層核心交換機(jī)而言,若欲實(shí)現(xiàn)網(wǎng)絡(luò)的無阻塞傳輸,這個速率能≤標(biāo)稱二層包轉(zhuǎn)發(fā)速率和速率能≤標(biāo)稱三層包轉(zhuǎn)發(fā)速率

2020-12-01 15:59:24

交換速度也就越慢。也就是說,背板帶寬決定著交換機(jī)的數(shù)據(jù)處理能力,背板帶寬越高,所能處理數(shù)據(jù)的能力就越強(qiáng)。若欲實(shí)現(xiàn)網(wǎng)絡(luò)的全雙工無阻塞傳輸,必須滿足最小背板帶寬的要求。 (1) 背板帶寬計算公式如下

2021-01-12 15:44:23

MT90820 芯片是 MITEL 公司最新推出的大容量數(shù)字交換器件, 當(dāng)串行數(shù)據(jù)碼流速率為8. 192Mb/ s 時 ,單片可實(shí)現(xiàn) 2048×2048通道的無阻塞交換。利用該器件的組合可構(gòu)成更大容量的交換網(wǎng)絡(luò)或

2009-04-22 15:59:06 25

25 GSM交換局數(shù)據(jù):

在進(jìn)行交換維護(hù)與優(yōu)化時,很重要的一個工作就是對局數(shù)據(jù)進(jìn)行操作,局數(shù)據(jù)就是交換機(jī)中的各種數(shù)據(jù),交換機(jī)正是通過這些局數(shù)據(jù)進(jìn)行工作,交換優(yōu)化中很

2009-07-29 15:37:57 7

7 本文介紹了DMA 在DSP 處理器中的作用,分析了基于TMS320C6204 CSL 中的DAT 接口特性。提出并實(shí)現(xiàn)了一種基于TMS320C6204 DMA 操作無阻塞請求的方法,并說明了該方法較EDMA 中相關(guān)的高級特

2009-08-05 09:03:12 10

10 本文針對Java NIO 的特性做出分析與闡述,對網(wǎng)絡(luò)應(yīng)用中阻塞通信與非阻塞通信、NIO的非阻塞工作機(jī)制以及網(wǎng)絡(luò)通信中非阻塞套接字的實(shí)現(xiàn)等問題進(jìn)行了研究和探討,提出了系統(tǒng)地

2009-08-10 10:15:22 18

18 的綜合通信單元,專門為電力配網(wǎng)自動化、工業(yè)自動化、煤礦監(jiān)控、交通等行業(yè)數(shù)據(jù)通信領(lǐng)域而設(shè)計的工業(yè)以太網(wǎng)交換機(jī)。提供全線速無阻塞轉(zhuǎn)發(fā),提供全雙工下的IEEE802.3x

2023-06-29 10:00:47

針對靶場光電測量設(shè)備子系統(tǒng)互聯(lián)比較復(fù)雜、容易產(chǎn)生時序沖突的缺點(diǎn),設(shè)計了基于FPGA的數(shù)據(jù)交換中心。實(shí)踐表明,該系統(tǒng)工作穩(wěn)定、可靠,解決了多系統(tǒng)之間通信的時序沖突問題

2010-07-06 15:35:53 11

11 本文在研究了三層以太網(wǎng)交換技術(shù)后,設(shè)計了一種采用FPGA來實(shí)現(xiàn)以太口和ATM口之間的數(shù)據(jù)通道上HEC模塊的實(shí)現(xiàn)方法。文中給出了詳細(xì)的設(shè)計方案,并論述了采用FPGA設(shè)計的原因和思路

2010-08-09 15:20:33 16

16 采用Xlinx公司的Virtex5系列FPGA設(shè)計了一個用于多種高速串行協(xié)議的數(shù)據(jù)交換模塊,并解決了該模塊實(shí)現(xiàn)中的關(guān)鍵問題.該交換模塊實(shí)現(xiàn)4X模式RapidIO協(xié)議與4X模式PCI Express協(xié)議之間的數(shù)據(jù)交

2010-09-30 16:31:57 39

39 AT-x600系列交換機(jī)是安奈特公司最新推出的一款高性價比IPv4/v6千兆/萬兆可堆疊多層以太網(wǎng)交換機(jī)機(jī)身僅1U高,卻提供非常豐富的功能特性,全線速無阻塞交換架構(gòu),線速L2交換與L3路

2010-10-08 23:56:08 8

8 MAX4358 32x16、無阻塞視頻交叉點(diǎn)開關(guān),帶有屏幕顯示及I/O緩沖器

概述

MAX4358是一種高度集成的,帶輸入輸出緩沖器及OSD插入功能的32 x 16視頻

2009-12-26 08:14:18 1413

1413

阻塞和非阻塞語句作為verilog HDL語言的最大難點(diǎn)之一,一直困擾著FPGA設(shè)計者,即使是一個頗富經(jīng)驗的設(shè)計工程師,也很容易在這個點(diǎn)上犯下一些不必要的錯誤。阻塞和非阻塞可以說是血脈相連,但是又有著本質(zhì)的差別

2011-03-15 10:57:34 6892

6892 基于ARINC664規(guī)范第7部分,提出符合該規(guī)范的基于FPGA的AFDX交換機(jī)整體設(shè)計方案及其核心交換芯片中關(guān)鍵模塊的VerilogHDL實(shí)現(xiàn),并通過功能仿真、時序仿真、網(wǎng)絡(luò)仿真等手段對交換芯片的功

2011-05-14 11:03:49 81

81 以Cyclone FPGA 器件為核心,設(shè)計數(shù)據(jù)交換機(jī). 描述了Cyclone 器件中LVDS 接口、鎖相環(huán)PLL 、片內(nèi)M4KRAM模塊、芯片配置的應(yīng)用方法和技巧,給出了軟件設(shè)計思路,并研制了數(shù)據(jù)下載線. 經(jīng)實(shí)際測試和

2011-06-27 15:57:30 44

44 多路交換開關(guān)是高性能交換部件的核心,本文描述了基于Xilinx公司Virtex-11系列FPGA的特點(diǎn)設(shè)計和實(shí)現(xiàn)的一種高速多路交換開關(guān),它由輸入信道組織、內(nèi)部無阻塞crossbar交換和仲裁調(diào)度器三

2011-12-27 16:45:04 46

46 華為Cloud Fabric云數(shù)據(jù)中心解決方案,為用戶搭建360T無阻塞交換平臺,并可提供高達(dá)數(shù)萬個10GE/GE服務(wù)器接入能力。具備彈性云、虛擬云及融合云網(wǎng)絡(luò)三大核心優(yōu)勢。

2013-06-08 10:34:25 2493

2493

Altium Designer關(guān)于FPGA的PIN交換

2015-12-10 16:59:37 0

0 這是一個很好的學(xué)習(xí)阻塞和非阻塞的資料,對于FPGA的學(xué)習(xí)有很大幫助。

2016-04-22 11:00:45 11

11 基于FPGA技術(shù)的CATV核心網(wǎng)絡(luò)無阻塞ATM交換結(jié)構(gòu)

2017-01-17 19:54:24 5

5 學(xué)verilog 一個月了,在開發(fā)板上面寫了很多代碼,但是始終對一些問題理解的不夠透徹,這里我們來寫幾個例子仿真出阻塞和非阻塞的區(qū)別

2017-02-11 03:23:12 1194

1194 在一開始學(xué)到阻塞和非阻塞的時候,所被告知的兩者的區(qū)別就在于阻塞是串行的,非阻塞是并行的。但是雖然知道這個不同點(diǎn),有些時候還是很難真正區(qū)分用兩者電路的區(qū)別,下載資料內(nèi)以一個簡單的串行流水線寄存器為例進(jìn)行了分析。

2017-09-16 09:34:07 4

4 本文闡述了在CATV核心網(wǎng)絡(luò)中用于數(shù)字視頻廣播(DVB)業(yè)務(wù)傳輸?shù)囊环N新型簡單的無阻塞ATM 交換技術(shù)結(jié)構(gòu)的主要特點(diǎn),對系統(tǒng)性能進(jìn)行了簡單的評估,并對系統(tǒng)采用FPGA技術(shù)交換帶來的特點(diǎn)、相關(guān)

2017-11-02 16:41:41 10

10 DMA在DSP應(yīng)用中至關(guān)重要,本文給出了DMA操作非阻塞的請求方法,針對TMS320C620x,實(shí)現(xiàn)了與CSL中DAT接口一致的驅(qū)動模塊QDAT,并指出了EDMA相關(guān)的高級特征。 在DSP中,DMA

2017-11-03 15:13:02 1

1 FAST的目標(biāo)是面向SDN的教學(xué)與科研,基于開源方式開發(fā)出一套以FPGA為核心的SDN交換機(jī)實(shí)現(xiàn)代碼,包括FPGA硬件源碼以及交換機(jī)中CPU上運(yùn)行的相關(guān)軟件源碼。參與SDN科研與教學(xué)的研究人員、教師

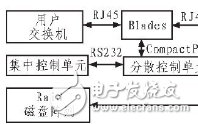

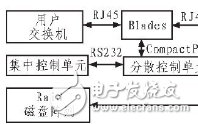

2017-11-16 17:00:01 3339

3339 新一代機(jī)架式服務(wù)器Blade Server(刀片服務(wù)器),應(yīng)用iSCSI協(xié)議,通過TCP/IP實(shí)現(xiàn)網(wǎng)絡(luò)存儲,利用Intemet,可將SCSI數(shù)據(jù)包傳到地球上的任何地方。 筆者著眼于刀片服務(wù)器的內(nèi)部構(gòu)架和整體方案的介紹,主要論述了基于FPGA的刀片與主板之間PCI數(shù)據(jù)交換的具體實(shí)現(xiàn)方法。

2017-11-24 16:37:37 2026

2026

設(shè)計背景: 阻塞 (=)和非阻塞(=)一直是在我們FPGA中討論的問題,資深的學(xué)者都是討論的是賦值應(yīng)該發(fā)生在上升下降沿還是在哪里,我們在仿真中看的可能是上升下降是準(zhǔn)確的,但是在時間電路中這就

2018-05-31 11:40:14 6358

6358

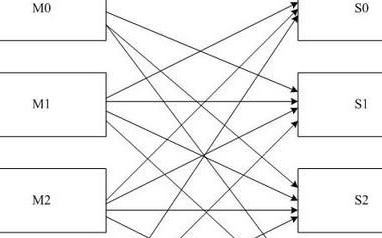

如果在FPGA設(shè)計中,需要多端口,大數(shù)據(jù)量的交換,那么交換矩陣則是一個不錯的實(shí)現(xiàn)方案。

2019-01-26 11:05:58 1909

1909

本文檔的主要內(nèi)容詳細(xì)介紹的是FPGA的視頻教程之Verilog中阻塞與非阻塞的詳細(xì)資料說明。

2019-03-26 17:16:31 2

2 QCA8334是一個高度集成的四端口千兆以太網(wǎng)交換機(jī),具有無阻塞的交換機(jī)結(jié)構(gòu),一個具有2048個MAC地址的高性能查找單元,以及一個四流量級服務(wù)質(zhì)量(QoS)引擎。QCA8334交換機(jī)具有支持各種

2019-05-22 08:00:00 57

57 本課程以目前流行的Xilinx 7系列FPGA的開發(fā)為主線,全面講解FPGA的原理及電路設(shè)計、Verilog HDL語言及VIVADO的應(yīng)用,并循序漸進(jìn)地從組合邏輯、時序邏輯的開發(fā)開始,深入到FPGA的基礎(chǔ)應(yīng)用、綜合應(yīng)用和進(jìn)階應(yīng)用。

2019-12-03 07:06:00 1707

1707

FPGA的引腳交換

2020-01-20 17:53:00 2843

2843 超大規(guī)模數(shù)據(jù)中心采用扁平的二層葉-脊(Leaf-Spine)架構(gòu)需要大量的互連,因為每個Leaf與Spine完全互連,最大限度地實(shí)現(xiàn)交換機(jī)之間的無阻塞網(wǎng)絡(luò)連接。

2019-09-10 15:19:10 700

700

對于VerilogHDL語言中,經(jīng)常在always模塊中,面臨兩種賦值方式:阻塞賦值和非阻塞賦值。對于初學(xué)者,往往非常迷惑這兩種賦值方式的用法,本章節(jié)主要介紹這兩種文章的用法。其實(shí),有時候概念稍微不清楚,Bug就會找到我們,下面一文掃清阻塞賦值和非阻塞賦值所有的障礙。

2020-01-30 17:41:00 20977

20977 ExpressLaneM PEX8796設(shè)備提供多主機(jī)PCI Express交換功能,使用戶能夠通過可擴(kuò)展的、高帶寬的、無阻塞的互連,將多臺主機(jī)連接到各自的端點(diǎn),連接到各種應(yīng)用程序,包括服務(wù)器、存儲系統(tǒng)和通信平臺PEX8796非常適合扇出、聚合和對等應(yīng)用程序。多主機(jī)體系結(jié)構(gòu)

2020-05-28 08:00:00 48

48 通信(ETU-LINK)為您重點(diǎn)介紹銳捷RG-S8600E系列交換機(jī)的特點(diǎn)及光模塊應(yīng)用方案。 銳捷RG-S8600E系列交換機(jī)的特點(diǎn) 1、CLOS架構(gòu)構(gòu)筑無阻塞交換 采用先進(jìn)的CLOS多級多平面交換架構(gòu),實(shí)現(xiàn)轉(zhuǎn)發(fā)與控制平面完全分離,即能夠配置獨(dú)立的交換網(wǎng)板與獨(dú)立的主控板,確

2020-07-03 17:56:48 3029

3029

16或24端口10/100/1000千兆交換機(jī)為您的10、100和1000兆網(wǎng)絡(luò)客戶端提供無阻塞、線速交換。將此交換機(jī)置于當(dāng)前工作組集線器或交換機(jī)的位置,您可以根據(jù)需要將高要求工作站升級到全千兆速度

2020-08-04 08:00:00 1

1 對于VerilogHDL語言中,經(jīng)常在always模塊中,面臨兩種賦值方式:阻塞賦值和非阻塞賦值。對于初學(xué)者,往往非常迷惑這兩種賦值方式的用法,本章節(jié)主要介紹這兩種文章的用法。其實(shí),有時候概念稍微

2020-11-19 15:48:56 927

927 采用Xlinx公司的Virtex5系列FPGA設(shè)計了一個用于多種高速串行協(xié)議的數(shù)據(jù)交換模塊,并解決了該模塊實(shí)現(xiàn)中的關(guān)鍵問題。該交換模塊實(shí)現(xiàn)4X模式RapidlO協(xié)議與4X模式PCI Express

2021-01-22 14:29:00 10

10 MAC實(shí)現(xiàn)雙RSGMMI-PLUS接口,用于在16端口交換機(jī)應(yīng)用中連接外部PHe(例如RTL8218)。RTL8376-GR集成了高速交換系統(tǒng)的所有功能:包括用于數(shù)據(jù)包緩沖的SRAM、無阻塞開關(guān)和寄存器管理到單個CMOS混合模式設(shè)備中。

2021-03-23 11:26:51 45

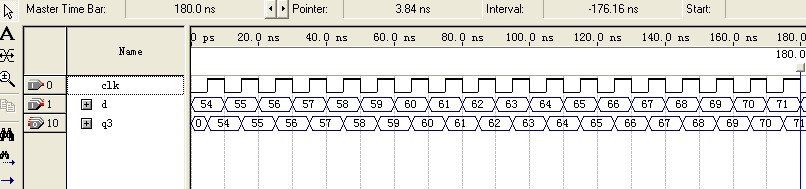

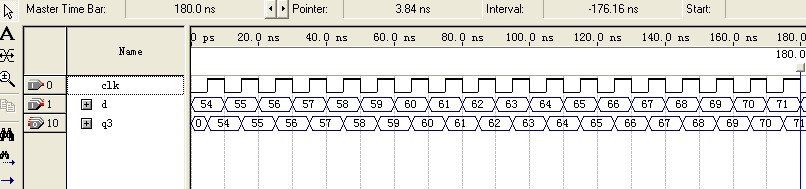

45 下面給出一個基于阻塞賦值和非阻塞賦值的多級觸發(fā)器級聯(lián)實(shí)例,要求將輸入數(shù)據(jù)延遲 3 個時鐘周期再輸出,并給出對應(yīng)的 RTL 級結(jié)構(gòu)圖和仿真結(jié)果。 (1)基于 D觸發(fā)器的阻塞賦值語句代碼如下

2021-05-08 14:47:05 1799

1799

阻塞賦值和非阻塞賦值的可綜合性 Blocking Assignment阻塞賦值和NonBlocking Assignment非阻塞賦值,原本是軟件進(jìn)程管理的術(shù)語。由于Verilog團(tuán)隊是從C語言發(fā)展

2021-05-12 09:45:09 2398

2398

? 在Verilog中有兩種類型的賦值語句:阻塞賦值語句(“=”)和非阻塞賦值語句(“=”)。正確地使用這兩種賦值語句對于Verilog的設(shè)計和仿真非常重要。 Verilog語言中講的阻塞賦值

2021-12-02 18:24:36 5005

5005

Verilog HDL的賦值語句分為阻塞賦值和非阻塞賦值兩種。阻塞賦值是指在當(dāng)前賦值完成前阻塞其他類型的賦值任務(wù),阻塞賦值由=來完成;非阻塞賦值在賦值的同時,其他非阻塞賦值可以同時被執(zhí)行,非阻塞賦值由《=來完成。

2022-03-15 13:53:08 2524

2524 阻塞賦值操作符用等號(即 = )表示。“阻塞”是指在進(jìn)程語句(initial和always)中,當(dāng)前的賦值語句阻斷了其后的語句,也就是說后面的語句必須等到當(dāng)前的賦值語句執(zhí)行完畢才能執(zhí)行。

2022-12-19 16:49:28 4607

4607 帶寬越大,提供給各端口的可用帶寬越大,數(shù)據(jù)交換速度越大;帶寬越小,給各端口提供的可用帶寬越小,數(shù)據(jù) 交換速度也就越慢。也就是說,背板帶寬決定著交換機(jī)的數(shù)據(jù)處理能力,背板帶寬越高,所能處理數(shù)據(jù)的能力就越強(qiáng)。若欲實(shí)現(xiàn)網(wǎng)絡(luò)的全雙工無阻塞傳輸,必須滿足最小背板帶寬的要求。

2023-05-04 17:19:09 215

215 對于VerilogHDL語言中,經(jīng)常在always模塊中,面臨兩種賦值方式:阻塞賦值和非阻塞賦值。對于初學(xué)者,往往非常迷惑這兩種賦值方式的用法,本章節(jié)主要介紹這兩種文章的用法。其實(shí),有時候概念稍微不清楚,Bug就會找到我們,下面一文掃清阻塞賦值和非阻塞賦值所有的障礙。

2023-06-01 09:21:57 514

514 阻塞通信(Blocking Communication):當(dāng)進(jìn)行阻塞通信時,調(diào)用者在發(fā)起一個I/O操作后會被阻塞,直到該操作完成返回才能繼續(xù)執(zhí)行后續(xù)代碼。

2023-06-15 17:32:21 3580

3580 優(yōu)化,兼容高清分辨率圖形,并且支持點(diǎn)對點(diǎn)通信和多播,最終實(shí)現(xiàn)最大性能指標(biāo) 高性能低數(shù)據(jù)延遲 PEX8747系統(tǒng)架構(gòu)兼容最大延遲為100ns(x16到x16)的數(shù)據(jù)直通。這與大數(shù)據(jù)存儲器、靈活性的通用型緩沖區(qū)/FC信用池和無阻塞內(nèi)部交換機(jī)框架相互結(jié)合,為服務(wù)器和交換機(jī)架構(gòu)等特性要求極高的應(yīng)用

2023-06-16 13:50:46 602

602 關(guān)于阻塞函數(shù)和非阻塞函數(shù)在CAN和LIN相關(guān)的開發(fā)庫里,不可避免的會出現(xiàn)“收”和“發(fā)”的函數(shù)。如何快速有效的處理數(shù)據(jù),是開發(fā)中重要的事項。

2022-07-05 14:38:43 692

692

今天給大家普及一下阻塞賦值和非阻塞賦值的相關(guān)知識

2023-07-07 14:15:12 1239

1239

Broadcom PEX8725設(shè)備提供多服務(wù)器PCIExpress交換功能,使用戶可以根據(jù)可擴(kuò)展性、高帶寬、無阻塞的互聯(lián)將數(shù)臺顯示器連接到各自端點(diǎn),以連接上各種應(yīng)用系統(tǒng),包括服務(wù)器、存儲、通信和圖型服務(wù)平臺。PEX8725特別適合扇出、匯聚和相等流量模式

2023-07-14 14:03:48 431

431 ”=“阻塞賦值與”<=“非阻塞賦值是verilog語言中的兩種不同的賦值方式,下面將對兩種賦值方式進(jìn)行比較。方便進(jìn)行理解和使用。

2023-09-12 09:06:15 587

587

從數(shù)據(jù)中心網(wǎng)絡(luò)架構(gòu)來看,基于現(xiàn)有的100G的方案,滿足相同規(guī)模數(shù)據(jù)中心的無阻塞網(wǎng)絡(luò)吞吐,需要添加更多的端口需要更多的機(jī)架空間用于服務(wù)器和交換機(jī),且需要更多的服務(wù)器機(jī)架空間,這些解決方案不經(jīng)濟(jì)且導(dǎo)致網(wǎng)絡(luò)架構(gòu)的復(fù)雜性呈幾何級提升。

2023-09-26 14:58:14 237

237

徹底完成后才返回到用戶空間;而非阻塞是指 IO操作被調(diào)用后立即返回給用戶一個狀態(tài)值,不需要等到 IO 操作徹底完成。 當(dāng)應(yīng)用進(jìn)程調(diào)用了 recvfrom 這個系統(tǒng)調(diào)用后,系統(tǒng)內(nèi)核就開始了 IO 的第一個階段 :準(zhǔn)備數(shù)據(jù)。 對于網(wǎng)絡(luò) IO 來說,很多時候數(shù)據(jù)在一開始還沒到達(dá)時,系統(tǒng)

2023-10-08 17:16:51 427

427

阻塞就是外部有阻塞干擾信號的時候,設(shè)備還可以正常運(yùn)行。一般分為帶內(nèi)阻塞和帶外阻塞,由于直放站都是做寬帶設(shè)備,一般只提帶外阻塞。

2023-10-10 11:22:37 546

546 全線速無阻塞轉(zhuǎn)發(fā),提供4個10/100/1000M自適應(yīng)網(wǎng)口(POE可選),2個1000M SFP光口擴(kuò)展槽。該交換機(jī)可以組建一個快速恢復(fù)的光纖自愈環(huán)網(wǎng),自愈時間

2023-07-03 17:40:48 0

0 。 一、常見原因 1. 網(wǎng)絡(luò)設(shè)備性能不足:網(wǎng)絡(luò)設(shè)備包括交換機(jī)、路由器等,如果設(shè)備處理能力不過關(guān),無法處理大量的數(shù)據(jù)流量,就會導(dǎo)致以太網(wǎng)阻塞。 解決方法:升級網(wǎng)絡(luò)設(shè)備,選擇更高性能、更適合當(dāng)前網(wǎng)絡(luò)負(fù)載的設(shè)備。 2. 網(wǎng)絡(luò)拓?fù)湓O(shè)計不

2023-12-27 13:58:15 381

381 Verilog是一種硬件描述語言,用于設(shè)計和模擬數(shù)字電路。在Verilog中,同步和異步是用來描述數(shù)據(jù)傳輸和信號處理的兩種不同方式,而阻塞賦值和非阻塞賦值是兩種不同的賦值方式。本文將詳細(xì)解釋

2024-02-22 15:33:04 202

202

電子發(fā)燒友App

電子發(fā)燒友App

評論