4、系統(tǒng)設(shè)計(jì)

4.1 圖像信號(hào)產(chǎn)生模塊的設(shè)計(jì)

產(chǎn)生圖像信號(hào)的核心器件采用Altera公司的Cyclone FPGA芯片EP1C3T144C8N。它具有多達(dá)20060個(gè)邏輯單元。最大用戶I/O數(shù) 104個(gè)。器件中M4K存儲(chǔ)塊提供288kbit存儲(chǔ)容量,能夠被配置來(lái)支持多種操作模式,包括RAM、ROM、FIFO及單口和雙口模式。

Cyclone器件具有高級(jí)外部存儲(chǔ)器接口,允許設(shè)計(jì)者將外部單數(shù)據(jù)率(SDR)SDRAM,雙數(shù)據(jù)率(DDR)、SDRAM和 DDR FCRAM 器件集成到復(fù)雜系統(tǒng)設(shè)計(jì)中,而不會(huì)降低數(shù)據(jù)訪問的性能。并且還具有兩個(gè)可編程鎖相環(huán)(PLL)和八個(gè)全局時(shí)鐘線,能提供時(shí)鐘管理和頻率合成,實(shí)現(xiàn)最大的系統(tǒng)功能。根據(jù)VGA顯示原理,圖象信號(hào)產(chǎn)生器的主要功能是:產(chǎn)生時(shí)序驅(qū)動(dòng)信號(hào)HS、VS及VGA彩色圖象編碼信號(hào),同時(shí)在正確的時(shí)序控制下,輸出ROM中的象素?cái)?shù)據(jù)至顯示器的VGA接口,進(jìn)行圖象顯示。FPGA內(nèi)部電路原理結(jié)構(gòu)如圖4。本文利用Altera公司QuartusⅡ6.0開發(fā)平臺(tái),遵循自頂向下的設(shè)計(jì)方法,針對(duì)各功能模塊,采用VHDL語(yǔ)言對(duì)FPGA器件編程,產(chǎn)生HS和VS掃描時(shí)序信號(hào)及各種圖象信號(hào)。

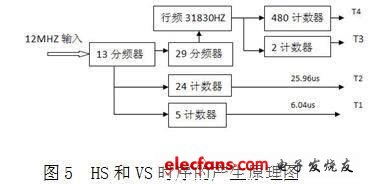

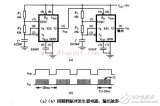

VGA時(shí)序信號(hào)是圖象顯示的關(guān)鍵,行場(chǎng)掃描時(shí)序的產(chǎn)生,是利用邏輯編程的方法實(shí)現(xiàn)的,即用VHDL編寫分頻器,計(jì)時(shí)器模塊,來(lái)獲得T1、T2、T3、T4時(shí)序。當(dāng)輸出數(shù)字、彩條信號(hào)和棋盤格圖象時(shí),由外部12M有源晶振提供時(shí)鐘輸入,其中行頻HS:12MHZ ÷13÷29=31830Hz、場(chǎng)頻VS:31830Hz÷480×0.93=61.67Hz、T1=1/31830Hz×4/29=25.96us、T2=1/31830Hz×5/29=6.04us、T3為兩個(gè)行周期(T1+T2),T4為480個(gè)行周期。

圖象信號(hào)包括數(shù)字、彩條、棋盤格,和ROM中定制的圖形等。數(shù)字信號(hào)和彩條信號(hào)的產(chǎn)生是按行場(chǎng)方向?qū)⑵聊桓鬟M(jìn)行8等分,相當(dāng)于一個(gè)8×8的點(diǎn)陣,在對(duì)應(yīng)位置顯示相應(yīng)顏色即可獲得所需圖像信號(hào);棋盤格信號(hào)是將橫彩條和豎彩條相異或獲得。ROM中定制的較為復(fù)雜的彩色圖像,需采用像素點(diǎn)輸出,即將圖像各像素點(diǎn)的信息存儲(chǔ)于ROM中,再以一定的頻率輸出。FPGA器件ROM的定制有兩種方法:第一種方法是利用FPGA器件的嵌入式存儲(chǔ)器定制LPM_ROM,用.MIF文件或.HEX文件對(duì)其進(jìn)行初始化,這種方法獲得的ROM最大尋址空間為2 12,可以存儲(chǔ)一幅分辨率為64×64的圖像信息;第二種方法是在FPGA邏輯資源的限度內(nèi)用VHDL語(yǔ)言定制一個(gè)ROM,采用CASE語(yǔ)句對(duì)其進(jìn)行初始化,這種方法獲得的ROM在存儲(chǔ)深度較大時(shí),編譯時(shí)對(duì)時(shí)間的開銷較大。ROM初始化完成后,在25MHz的時(shí)鐘頻率下輸出存儲(chǔ)的圖像信息。其圖象顏色種類的多少取決于存儲(chǔ)空間的大小。

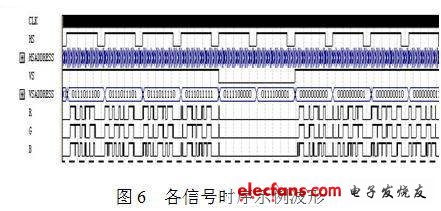

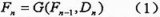

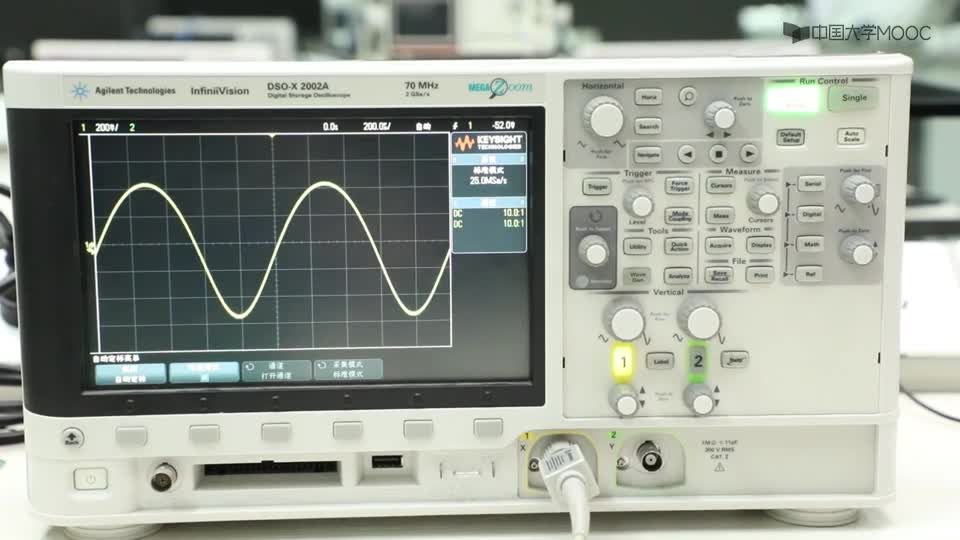

ROM定制的圖象信息是利用FPGA嵌入的存儲(chǔ)器定制LPM_ROM,可以用于存儲(chǔ)一幅64×64分辨率的圖像信息,數(shù)據(jù)線寬為3位,地址線12根,采用組合尋址方式,即行地址HSADDRESS占低6位,場(chǎng)地址VSADDRESS占高6位;若要顯示更為復(fù)雜的圖象信息,只需擴(kuò)展存儲(chǔ)器及尋址的數(shù)據(jù)線寬度,為了保證行地址信號(hào)輸出與行掃描信號(hào)輸出同步,場(chǎng)地址信號(hào)輸出與場(chǎng)掃描信號(hào)輸出同步,在VHDL編程時(shí),可用25MHz時(shí)鐘作為進(jìn)程的啟動(dòng)信號(hào)。輸出信號(hào)的時(shí)序波形如圖6所示。各種圖象信號(hào)的輸出是由數(shù)據(jù)選擇器通過(guò)VHDL編程實(shí)現(xiàn)的。

4.2 視頻輸出接口電路部分設(shè)計(jì)

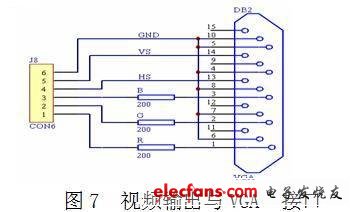

VGA 接口采用非對(duì)稱分布的15pin 連接方式,其工作原理是將顯存內(nèi)以數(shù)字格式存儲(chǔ)的圖像( 幀) 信號(hào)在RAMDAC 里經(jīng)過(guò)模擬調(diào)制成模擬高頻信號(hào),然后進(jìn)行輸出顯示,這樣VGA信號(hào)就不必像其它視頻信號(hào)那樣還要經(jīng)過(guò)矩陣解碼電路的換算。從視頻成像原理可知VGA的視頻傳輸過(guò)程是最短的,所以VGA 接口擁有許多的優(yōu)點(diǎn),如無(wú)串?dāng)_、無(wú)電路合成分離損耗等。視頻輸出與VGA 接口如圖7。

4.3 模式控制與顯示部分設(shè)計(jì)

為了實(shí)現(xiàn)人機(jī)對(duì)話,模式控制與顯示即人機(jī)接口的設(shè)計(jì),選用LCD顯示器和矩陣鍵盤,使接口和顯示更加友好。要求能根據(jù)鍵盤掃描結(jié)果,控制不同的圖象信號(hào)輸出,并進(jìn)行相應(yīng)的功能顯示。采用單片機(jī)89S51作為控制器,對(duì)鍵盤模塊和功能顯示模塊進(jìn)行控制。用C語(yǔ)言編程,對(duì)鍵盤進(jìn)行掃描和液晶顯示模塊的控制。當(dāng)然也可以對(duì)FPGA器件編程,實(shí)現(xiàn)對(duì)鍵盤模塊和功能顯示模塊的控制。但需占用FPGA器件的邏輯資源,會(huì)對(duì)定制圖像信息的存儲(chǔ)空間造成影響。

本設(shè)計(jì)采用4×4矩陣式鍵盤,行、列線占用單片機(jī)8個(gè)I/O口資源,鍵盤掃描過(guò)程是列掃描行輸出,逐列掃描,讀取鍵值,根據(jù)讀回的值判斷所按鍵的位置,按鍵消抖采用延時(shí)消抖方式,根據(jù)鍵值跳轉(zhuǎn)執(zhí)行相應(yīng)功能程序。顯示器采用TS-12864-3液晶顯示屏,由單片機(jī)控制及驅(qū)動(dòng),顯示系統(tǒng)當(dāng)前工作狀態(tài)等信息。

5、結(jié)束語(yǔ)

隨著數(shù)字圖像處理的應(yīng)用領(lǐng)域不斷擴(kuò)大,其實(shí)時(shí)處理技術(shù)成為研究的熱點(diǎn)。EDA(電子設(shè)計(jì)自動(dòng)化)技術(shù)的迅猛發(fā)展為數(shù)字圖像實(shí)時(shí)處理技術(shù)提供了硬件基礎(chǔ)。其中FPGA的特點(diǎn)使其非常適用于進(jìn)行一些基于像素級(jí)的圖像處理。 本文設(shè)計(jì)的基于FPGA的數(shù)字圖像實(shí)時(shí)生成系統(tǒng),可以實(shí)現(xiàn)各種數(shù)字、文字、彩條、ROM圖像信號(hào)輸出。其圖像顯示控制器的系統(tǒng)處理耗時(shí)小于20ms,完全達(dá)到了實(shí)時(shí)要求(50場(chǎng)/秒)。所進(jìn)行的原理試驗(yàn)取得了良好的效果。

本系統(tǒng)可以作為顯示器測(cè)試信號(hào)發(fā)生器,適用于顯示器生產(chǎn)廠或者維修人員 、計(jì)算機(jī)房、以及單位用戶、甚至個(gè)人用戶,進(jìn)行無(wú)需連接主機(jī)的畫面演示、測(cè)試、檢查,和維修后調(diào)試,通過(guò)對(duì)標(biāo)準(zhǔn)圖形的觀察和分析,能夠判斷顯示器的總體性能或維修后效果。

本設(shè)計(jì)還可以作一些擴(kuò)展,如添加語(yǔ)音處理電路,實(shí)現(xiàn)圖像輸出時(shí)同步輸出語(yǔ)音;還可以外接大容量存儲(chǔ)器,采用8位二進(jìn)制數(shù)據(jù)表示R、G、B三基色,實(shí)現(xiàn)256色輸出,使顯示的圖像色彩更加豐富。

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論