能耗給設計帶來的限制可能比任何一個其他因素都來的多。隨著一個新的概念的不斷發展,平衡新功能和能耗效率成為一個首要問題。

以此對大部分的功能做出限制是不可能的,所以能耗的管理就成為一個設計成功關鍵因素。

控制,并降低電子設計的能耗將使整個產品的開發流程受益。這樣可以將一個不合適的產品改進以適應市場,但是這也需要在成本和制造上做出變化。舉例來說,一個低能耗的設計使用更小的電源,更少的元件,和一個更小的外殼。這樣可以減低設計的復雜程度,并最終降低產品的成本。

在此之外,一個擁有低能耗的設計會有一個更簡單和低成本的熱解決方案。減少熱源,通過空氣流動的來降低溫度都對產品有很多的好處。對產品工作溫度的有效控制也對產品的耐用性有很大的貢獻。產品的工作溫度直接影響性能和產品壽命,所以電源管理對于高性能產品來說就很重要。但是這一切只有在原型機的階段才能實現。

讓電子產品的設計符合電源要求需要各個方面配合。系統工程師,軟件工程師,嵌入式工程師,和板級布線工程師都需要通盤考慮來達到目前對電源的要求。新技術和流程給工程師帶來了新的挑戰,而我們也要因此而做出改變。

新的困境

當產品尺寸在不斷縮小,便攜式產品到處都是的時候,電源管理就成為一個新的老問題。薄型電源電池,小尺寸外殼的復雜性,和對高性能的需求都對電源管理來說是一個很大的挑戰。

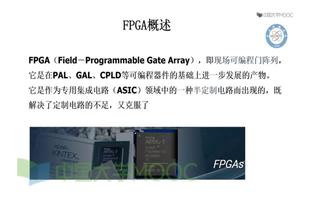

而類似FPGA的可編程器件的加入則更增加了管理的復雜性。可編程器件正在重新定電源的能耗。和可以預測的傳統的設備能耗相比,FPGA的能耗不能僅僅從簡單的數據來推測。FPGA的能耗和內部的程序的尺寸和種類有很大的關系。

在嵌入式FPGA設備理管理電源的難度和設備本身一樣的復雜。因為FPGA的能耗很大程度上取決于內部的程序,能耗僅可被可以計算嵌入式自身能耗的工具來預測。或者就是等到原型機的階段,通過真實的電源消耗來計算,以此來修改設計以達到性能和能耗的平衡。但是這樣的延遲計算使得傳統的設計流程無法支持目前的需求。

不管怎樣,FPGA提供許多了靈活的設計方式,并在性能上和ASIC拉近了差距,對現代的很多產品設計是很有吸引力的。但是能耗的不確定性和分析仍然是一個大問題。拉近看一下影響FPGA設備能耗的原因可以解釋管理的復雜程度和預測的難度。

FPGA電源分析

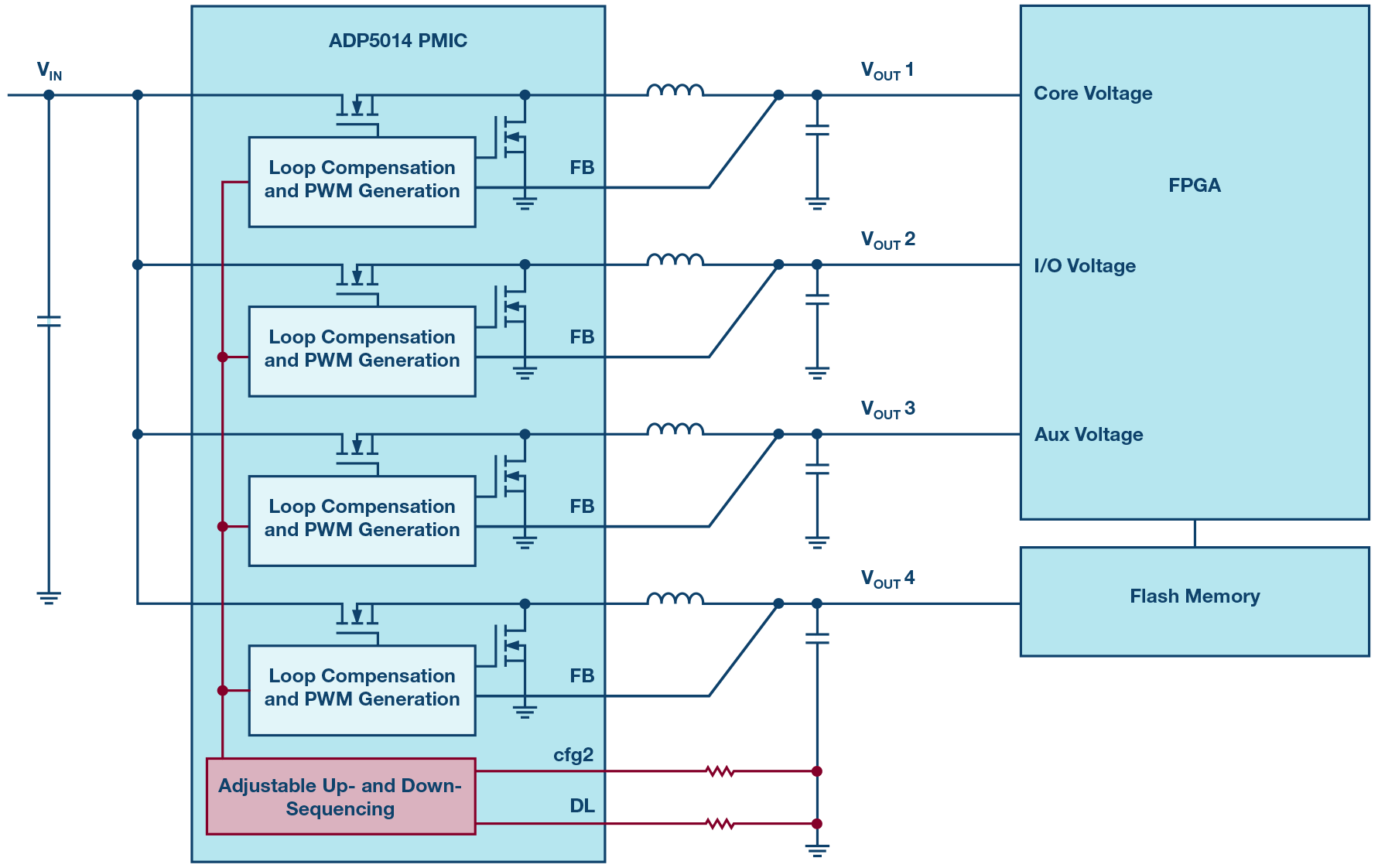

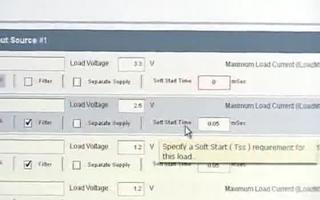

當FPGA設備在打開時候的電流消耗高峰以及當FPGA設備從休眠模式被喚醒以后會產生一個明顯的波動。這需要在設計中被考慮到,并且和低功耗模式一起的本很好的平衡。當模式被改變或者設備被關閉的時候,設備會被重新編程以適應恢復運行時所產生的能耗高峰。

增加控制功能以讓所有的嵌入式硬件關閉固然可以節約大量的能耗,但是在實際應用中這樣的節約需要用電源分析工具來進行預測。

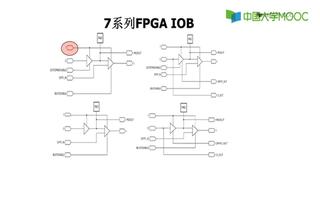

到目前位置,FPGA能耗控制中最大的變數是動態電源,也就是來自實時操作的影響。

從時鐘信號到I/O輸出,動態電源受到FPGA可編程內容的影響。而可編程內容則在產品的開發過程中不斷的在變化。當設備CMOS組的電容根據邏輯層面的變化而被充電時,能量就被消耗了

從設計角度來將動態電源消耗是一個包含頻率,電容和電壓的整體,降低時鐘頻率和電壓將會提高能耗效率。采用多處理器,并行低能耗處理,系列數據通道,適應性時鐘頻率都將降低能耗。動態能耗配置的目的是為了創建優化的電源模式,FPGA將被自動的重新編程以達到最佳的能耗狀態。但是,需要由能耗預測工具來證實添加這樣的復雜性是值得的。

相對來說,FPGA靜態能耗是比較穩定和容易被預測的。但是當工藝流程到了90nm的程度,另一個最大的障礙出現了。CMOS的尺寸縮小,和通道的縮短和更細的門導致電流容易溢出。FPGA的靜態能耗就隨著工藝流程的進步而逐漸增大,但是也會因為使用低電壓而相對減少。這對未來FPGA的設計是一個挑戰,尤其是當設計師希望在便攜式設備中越來越多的使用FPGA的時候會變得更明顯。

FPGA內部主要能耗單位的關系是復雜而互相影響的。例如,時鐘頻率的提高造成動態電源能耗的增加,會導致設備溫度的上升,最終會引起管腳的溢出和更高靜態能耗。這不像熱力逃逸,但是會成為FPGA能耗預測問題的一個不可避免的因素。

可用工具

管理嵌入式FPGA的能耗就像管理設備一樣的特別。因為FPGA的能耗大部分有可編程的內容所決定,能耗的數值需要由嵌入式設計本身來完成。

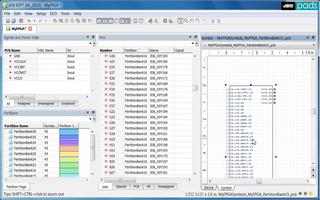

為了配合這樣的流程,FPGA設備的廠商會提供含有能耗預測的開發工具。這些工具將FPGA的許多參數和利用設計來分析并預測大致的能耗,并且還在不斷的改進中。在分析的早期,工程師需要輸入基本的信息例如時鐘頻率和功能模塊的數量等。更多的分析結果可以根據用戶的設計細節來推測。

這樣的方法僅可以提供一個關于嵌入式設備能耗的一些節本訊息,但是當設計被修改后,整個流程需要被重新運行。因為目前不支持不同廠商的FPGA設備,評估能耗效率的流程并不是那么容易,而且也不能真實的優化FPGA能耗來達到產品設計的要求。

目前管理FPGA電源的方式就像一個預測,然后被原型階段的測試所確認。為了解決能耗問題改變FPGA種類的方式并不可取,因為這樣的風險太大了。重新工程設計所需要的時間會導致設計計劃的延誤,因為這已經是一個硬件改變的案例了。

如果用戶在很大程度上依賴目前的工具來計算能耗,硬件和嵌入式的設計就必須在設計開始的時候就進行定義。在開發過程中進行調整的機會并不多。任何潛在的問題都最好被研究并利用FPGA電源管理工具進行處理。

實時的電源分析和優化

在不影響產品設計的前提下,使能耗設計達到電源的要求需要電源分析工具和應用其他一切可能的方法。需要在開發過程中提供很多的信息,使得在原型階段之前就完成最主要的產品設計。

從最終產品的角度來看,FPGA的能耗就只是問題的一部分了。電源分析和測試需要擴展到外設電路和支持設備,以達到能耗優化的目的。

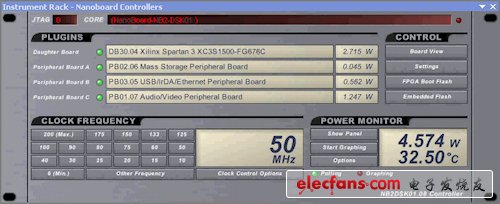

一種實時的方法可以讓FPGA設計達到設計的要求并完成優化工作。在開始的時候,設想FPGA開發板擁有通過一系列的感應器實時進行電源監控的能力,并將獲得的數據反饋會設計軟件。

電源監視可以集成到開發板的一個集成界面中去。FPGA和所有連接的外設板的讀數可以被顯示出來。

這樣,電源的實時情況就可以被監視,圖表化并被記錄。因為節點模式包括重新編程產生的高峰所產生的能耗可以被精確估計,嵌入式硬件和軟件的功能就可以被廣泛的開發了。關于能耗的預測則進入了量化的階段。

下一步就是讓最終產品和開發板以及設計軟件進行整合。這樣的整合需要開發板具有可插拔和很容易交換的FPGA卡板,而且每一個變化的數據都會回復到設計軟件。設計軟件可以根據一系列的系統驅動來支持很多不同的FPGA設備,用預先驗證的IP組合來支持所有它們。

如果設計軟件還包括嵌入式設計的高度抽象捕捉功能,例如原理圖或者圖形流程的界面,就可以讓和嵌入式的互動變得更為容易。嵌入式設計可以被容易的完成或者被修改,當FPGA設計被改變后電源能耗的變化可以被高級開發板即時的記錄。

該開發板還可以涵蓋擁有“智能電源探測器”的子板,記錄所有的硬件實施,以便從功能和電源有效性的角度進行分析。

更進一步來說,如果目標產品就是開發板,從開發到原型的時間就會大幅的縮短,對于能耗分析預測工具的要求也就不是那么多了。這樣,設計的開發板就可以代替原型,并且在產品開發的過程中精確的執行能耗控制。

這樣的方法可以讓用戶有效的開發最終產品,并可以應用在適合的即買即用或專門定制的板子上。這樣的系統不再需要依靠傳統的能耗預測工具提供精確的數值,相反可以讓用戶可以很方便的在不同的FPGA設備上遷移自己的設計,并將嵌入式的功能發揮出來。

為未來做準備

H在目前的設計理激發FPGA的所有特性,特別是在那些電池供電的設備中,意味著對FPGA電源控制的完全理解和控制。

FPGA廠商為了迎合市場對低功耗的需求,推出了基于flash的非波動設備,和有效能耗架構和高級節電模式。但是不管怎么樣,基于FPGA的設計總會在能耗的有效性和功能之間有所取舍。所以選擇一個合適的工具來平衡這樣的取舍就顯得至關重要。

為了今天和明天的設計,關鍵是要解決如何有效的通過快速的原型建立來解決能耗有效性的平衡問題。用戶不能僅僅依靠能耗的預測工具,而要引入先進的設計系統和在硬件上進行實時的開發。這樣工程師就可以充分的探索創新的設計來最大限度的激發FPGA的所有特性,并用于開發新一代的節能產品。

電子發燒友App

電子發燒友App

評論