電子發燒友網:針對目前電子發燒友網舉辦的“玩轉FPGA:iPad2,賽靈思開發板等你拿”,小編在電話回訪過程中留意到有很多參賽選手對Xilinx 公司的FPGA及其設計流程不是很熟悉,所以特意在此整理了一些相關知識,希望對大家有所幫助。當然也希望Xilinx? FPGA工程師/愛好者能跟我們一起來探討學習!

需要下載本文的話,請點擊以下鏈接下載:Xilinx FPGA設計實例介紹

一.概述

本文主要幫助大家熟悉利用ISE進行Xilinx 公司FPGA 代碼開發的基本流程。主要是幫助初學者了解和初步掌握 ISE 的使用,不需要 FPGA 的開發基礎,所以對每個步驟并不進行深入的討論。

本文介紹的內容從新建 project 一直到下載到硬件觀察現象為止,涵蓋整個開發過程。考慮到我們的開發一般以 Verilog HDL 或 VHDL 為主,在本文中未介紹原理圖輸入工具和 IP 核使用工具等。這同時是出于為了使文章脈絡更清晰,讓大家更快地學會 ISE 的考慮。關于這些專用工具,可以參看 HELP 或者其他文檔。

為了更直觀的理解,我們需要一個實驗平臺,在本文中,采用的是 Digital Power Studio 工作組 FPGA SPARK1.1 綜合開發平臺的 Xilinx 標準型開發系統。如圖 1 所示(圖中為 Altera 子板,只需改成 Xilinx 的即可)。在該開發系統中,所采用的芯片是SPARTANII系列的XC2S200 。

圖1 FPGA SPARK1.1 外觀圖

二.實現功能

在如上系統中右邊有一個 128×64 帶背光的點陣型液晶。我們的實驗就是用Verilog HDL 編寫一段代碼驅動液晶顯示一個流氓兔。其效果如圖 2 所示:

圖2 點陣液晶上顯示流氓兔的效果圖

三.軟件準備

本文介紹的是 Xilinx 公司的 ISE 開發環境。現在最新的版本是 ISE7.1,其界與 ISE5.x/ISE6.x 一致。為了更好地進行仿真,還需要安裝 Modsim。但是 ISE本身可以進行仿真,也可以不安裝 Modsim。

流程介紹:

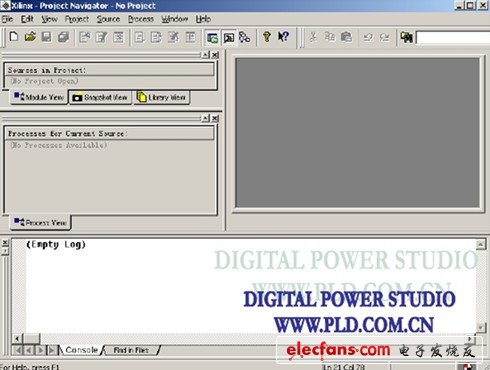

1.新建項目

在開始—〉程序—〉Xilinx ISE 中找到 Project Navigator,點擊打開。也可以通過雙擊桌面上 Project Navigator 的快捷方式打開。ISE 開發環境如圖 3 所示:

圖3 ISE 開發環境

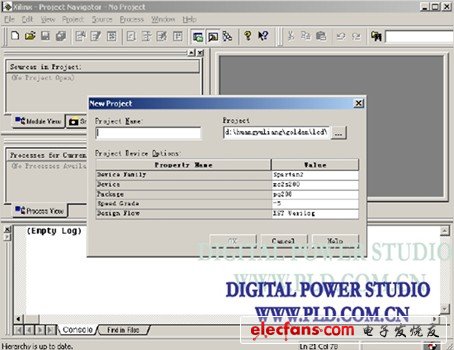

圖3 中選擇 File—〉New Project,進入圖 4;

圖4 新建 project 界面

在 Project Name 欄輸入項目名稱,Project 中填入該項目的目錄,Project Device Options 中,Device Family 為所用芯片所在系列,Device 為所用芯片,Package為所用芯片的封裝形式(每個芯片可能有不同封裝的幾種,如 XC2S200 有 3 種封裝的),Speed Grade 為速度等級,Design Flow 為所選用綜合方式(綜合工具

和代碼語言)。由于采用的是 FPGA SPARK1.1,采用如圖 5 的設置。

圖5 新建項目的信息輸入

其中 XST Verilog 表示采用 ISE 自帶的綜合器,代碼語言為 Verilog HDL,ISE支持其他綜合工具的調用,也支持標準 edif 文件的輸入。XST 是 ISE 自帶的綜合工具,由于 Xilinx 對自身的硬件了解程度比任何第三方軟件開發商都更深,故XST 的綜合性能有自身獨特的優點。

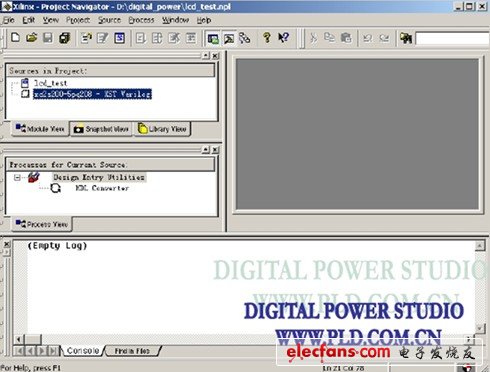

點擊 ok,新建項目完成。可以在相應目錄下看到生成的文件。效果如圖 6。如果要更改硬件的設置,可以雙擊圖 6 中模塊視窗內藍色選中的所示對應選單,即可進入 project properties 界面重新進行設置。

圖6 效果圖

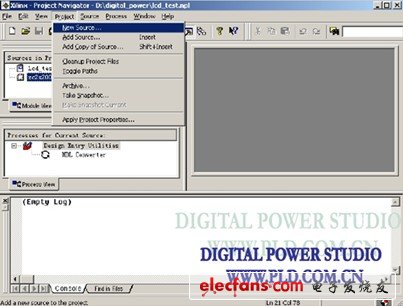

2.編寫和導入代碼文件

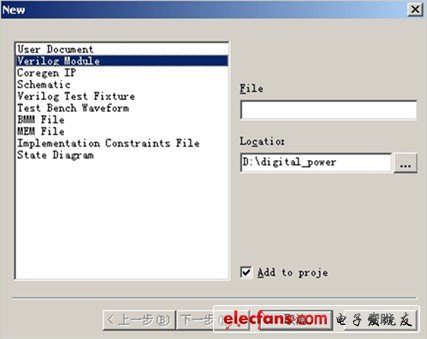

如圖 7 中所示,在 Project 菜單下,選擇 New Source 建立新的代碼文件。彈出的對話框如圖 8 所示。

圖7 Project 菜單

圖8 新建代碼文件對話框

在 File 中輸入文件名稱,Location 最好選用和 project 文件所在目錄同一個目錄。將 Add to project 選單選中,該文件將自動被加入當前 project 中。在左邊窗口中選擇建立的文件類型,如圖 8 選為 Verilog Module。點擊下一步,如圖 9所示。

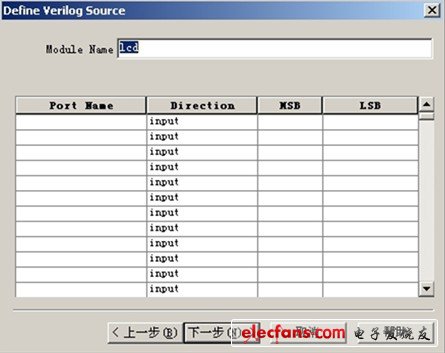

圖9 Verilog 代碼文件定義對話框

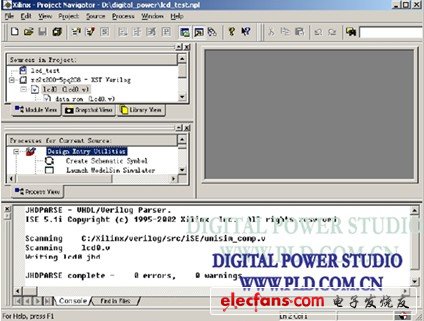

在圖 9 中,可以定義代碼文件的輸入輸出端口,可以不進行定義,直接點擊下一步。如果進行了定義的話,生成的代碼文本文件會自動加上定義好的輸入輸出端口。點擊下一步,進入下一對話框后點擊完成,即可。如圖 10 所示。在圖10 中,可見左面 Module View 中 project 中已經多處了剛才建立的 lcd 模塊,右

邊打開的 lcd 文件界面中,可以進行代碼的編寫。

圖10 代碼文件生成后界面

前面介紹的是編寫代碼,如果已經用其它工具編寫好了代碼,或者有現成的代碼,則不需要再重新編寫了,下面介紹如何將已有的 verilog 文件導入到 project中。

在圖 7 中不要選擇 New Source,而選擇 Add Source。在彈出的窗口中找到已有代碼文件(可同時加多個文件),并點擊“打開”即可。注意:Add Source 是將當前選擇的代碼加入到當前 project 中,而 Add Copy of Source 是將代碼文件復制到當前 project 所在目錄中,并將復制后的文件加到 project 中。建議使用后者。添加后結果如圖 11 所示。(在本文例子中,加入的是 Digital Power 提供的液晶程序 lcd.v。)可以看到在Module View 窗口中將顯示出 verilog 代碼中所有Module,并顯示出其層次結構以及其所在的文件。

圖11 Add Source 結果圖

3.調用 Modsim 進行仿真

由于 modsim 的性能非常優秀,以及它的普及程度廣,在本文中,介紹如何調用 modsim。首先,在 edit 菜單中選擇 Preferences 選項,彈出如圖 12 所示對話框。在 Partner Tools 中的 Model Tech Simulator 輸入框中填入您所安裝的 Modsim 應用程序文件的路徑。若您所裝的 Modsim 版本為專門為 Xilinx 編寫的 Modsim Xilinx

edition版本,可以省略該步驟。經過設置以后,回到如圖 13 所示界面。

圖12 Preferences 對話框

圖13 調用 Modsim

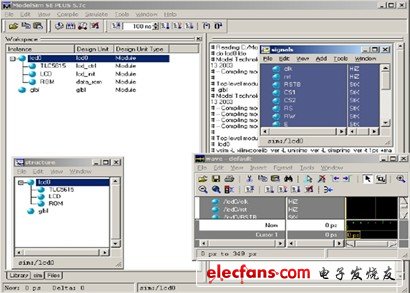

圖13 中Module View 窗口中選中代碼的最頂層模塊。而后如圖 13 藍色部位所示,在 Process View 窗口中的 Launch Modelsim Simlator,將自動打開 Modsim,并且已將當前 project 的相關信息加載到了 Modsim 中。如圖 14 所示。要注意的是,后仿真也是如此調用 Modsim。關于 Modsim 的使用請參考相關文檔。如果需要仿真的不是最頂層模塊,則在 Module View 窗口中選中相應的代碼文件,用同樣的步驟調用仿真。

圖14 調用的 Modsim

4.約束文件

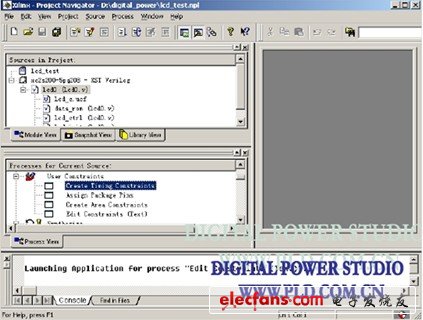

ISE 是一款基于約束的開發工具。在進行高速數字電路設計的時候,需要在綜合、映射、布線時附加約束條件,以便控制綜合、映射、布線過程,使設計滿運行速度,使用資源和引腳位置等要求。約束包括時序約束、分組約束和區域約束。在本文中,將介紹最常用的Constraints Editor 約束編輯器,以及時序約束和引腳綁定(該兩者最為基本)。首先,像第二步編寫代碼文件中一樣建立約束文件(.ucf 文件),在本文中,如圖 15 所示,可以看到 lcd_c.ucf 文件即為一個約束文件。新建時,唯一的不同是在圖 8 中左面對話框中應選擇 Implementation Constraints File。同樣地,如果已經有現成的約束文件,也可以通過和代碼文件相同的方法導入。如圖 15 所示,在 Module View 窗口中選中代碼的最頂層模塊,而后在 ProcessView 窗口中雙擊 Create Timing Constraints或者 Create Area Constraints,將自動打開 Constraints Editor 約束編輯器。

需要注意的是,雙擊 Assign Package Pins 將打開引腳與區域約束編輯器PACE,由于 Constraints Editor 約束編輯器完全可以完成引腳綁定的功能,對于PACE 的使用,本文不再進行詳細討論。Constraints Editor 如圖 16 所示。

圖15 ?在project navigator 中調用 Constraints Editor

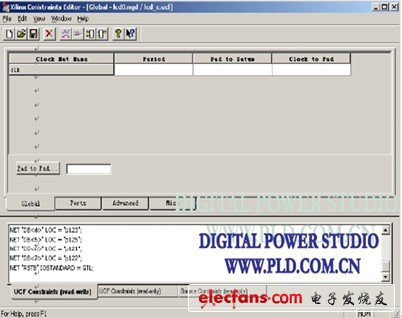

圖16 Constraints Editor 界面

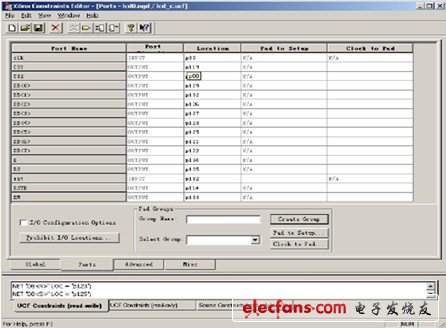

如圖 16 所示,共有四類約束界面,Global 為附加全局約束,Ports 為附加端口約束,Advanced 為附加分組約束和時序約束,Misc 為附加專用約束。常用的是 Ports,其中可以進行引腳綁定,如圖 17 所示。雙擊對應信號的Location 框,可以進行輸入。在引腳號前必須加上字母 p。在這次 LCD 實驗中,可以直接導入 digital power 提供的 lcd_c.ucf 文件,也可以自己在 Constraints Editor 中如圖 17 中所示一樣進行設置。

圖17 附加引腳約束

通過以上設置,就完成了約束,在這里附加提到一點就是,在 Constraints Editor 中,下方的對話框將顯示 ucf 文件的內容。約束文件也可以通過文本輸入的方式完成,在圖 15 中雙擊 Edit Constraints(Text)即可。

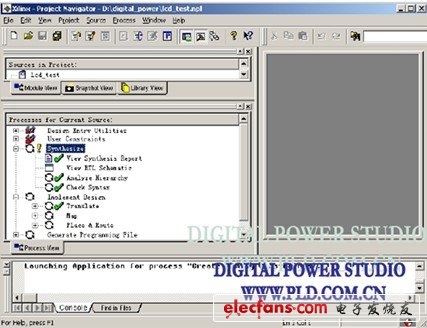

5.綜合與實現

在進行完約束以后,就可以進行綜合與約束了。綜合與實現的工作將由 ISE自動完成,用戶通過約束文件和對 properties 選項控制實現對整個過程的控制。整個過程將產生映射、布線等一系列時序報告以及 RTL schematic View,還可以利用 XPower 進行功耗分析,便于用戶對綜合與實現的結果有個詳細的了解。

綜合與實現如圖 18 所示。

圖18 實現與綜合

在 process view 中,Synthesize 為綜合過程,Implement Design 為實現過程。在其上點擊右鍵選擇 properties 選項,將進入 properties 對話框,可以對過程要求進行控制。一般直接點擊右鍵選擇 run all 即可。

6.下載

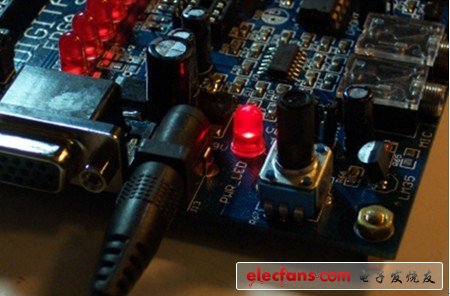

最后就只剩下下載工作了。在下載之前,必須先將硬件準備好。首先,如圖 19 所示,連接好電源線。

圖19 連接電源線

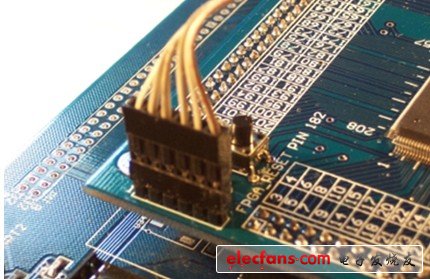

其次,如圖 20 所示,連接好下載線。

圖20 連接下載線

在硬件準備好后,如圖 21 所示,雙擊 Configure Device(iMPACT),打開 ISE中集成的芯片下載具 iMPACT。

圖21 打開 iMPACT

iMPACT 如圖 22 所示。

圖22 iMPACT

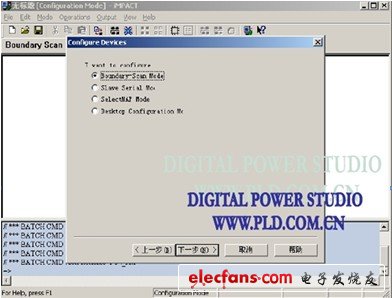

在圖 22 中,點擊下一步。

圖23 選擇配置 FPGA 的方式

如圖 23 所示,是選擇配置 FPGA 的方式,選擇第一項邊界掃描(JTAG)方式。點擊下一步。進入下一界面后,點擊完成。若硬件連接正確,將進入圖 24 所示界面,XC2S200 芯片將被自動搜索到,顯示出來。若硬件連接有問題,可以在正確改接硬件電路以后,在空白出點擊右鍵選擇 Initialize Chain 略過以上一些步驟直接開始搜索芯片。若連接有問題,將彈出對話框選擇連接端口,一般采用默認的 LPT 端口(并口)即可。

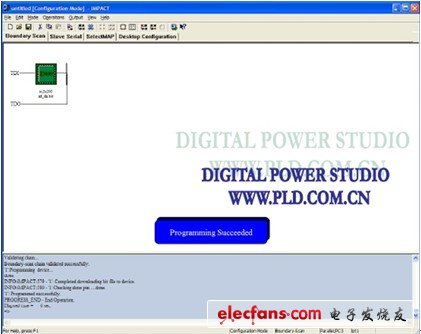

雙擊圖中 XC2S200 的圖標,在彈出的窗口中選擇你所需要下載的 bit 文件,點擊 ok 即可。在 XC2S200 上點擊右鍵選擇 PROGRAMME,并在彈出的對話框中選擇programme 將開始下載。

下載成功后如圖所示。

?

這時你就可以在液晶上看到如圖 2 所示的流氓兔效果了。

需要下載本文的話,請點擊以下鏈接下載:Xilinx FPGA設計實例介紹

想要了解更多關于Xilinx FPGA的相關資料,請繼續關注電子發燒友網,我們將陸續為您呈現!

電子發燒友App

電子發燒友App

評論