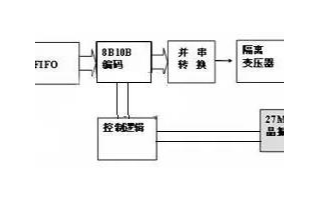

是使用非常廣泛的一種接口形式,該接口隨同SPI一起被歐洲電信標(biāo)準(zhǔn)化協(xié)會(ETSI)制訂,以使不同廠家生產(chǎn)的MPEG2單元可以方便地進(jìn)行互聯(lián)。本設(shè)計(jì)方案以FPGA為核心器件,制作出了SPI-ASI接口轉(zhuǎn)換器。這套方案成本較低,利用FPGA的可編程性,硬件的升級較容易

2023-10-18 12:13:04 1427

1427

傳統(tǒng)的Flash讀寫是通過CPU軟件編程實(shí)現(xiàn),其讀寫速度較慢,且占用CPU資源,另外由于Flash芯片本身功能指令較多,使得對芯片進(jìn)行直接操作變得非常困難。本文提出一個(gè)基于FPGA的SPI

2013-09-24 09:12:37 5517

5517

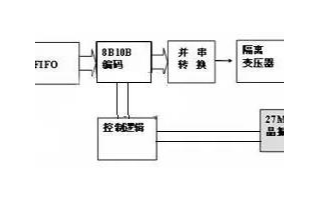

SERDES恢復(fù)出的數(shù)據(jù)進(jìn)入FPGA有一個(gè)解復(fù)用和時(shí)鐘域轉(zhuǎn)換的問題,Stratix GX包含了專用電路可以完成8/10bit數(shù)據(jù)到8/10/20bit數(shù)據(jù)的Mux/Demux,另外SERDES收端到FPGA內(nèi)部通用邏輯資源之間還有FIFO可以完成數(shù)據(jù)接口同步,其電路結(jié)構(gòu)如圖所示。

2018-04-08 08:46:50 9421

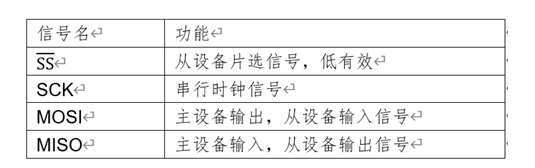

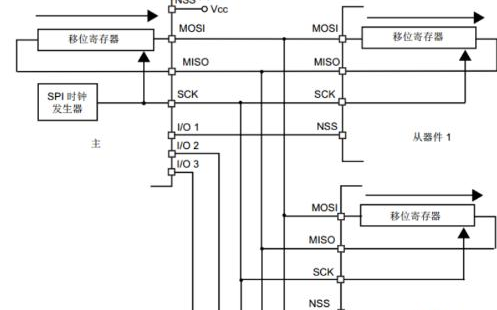

9421 SPI:Serial Peripheral Interface,是串行外設(shè)接口。

2022-09-30 15:02:51 2002

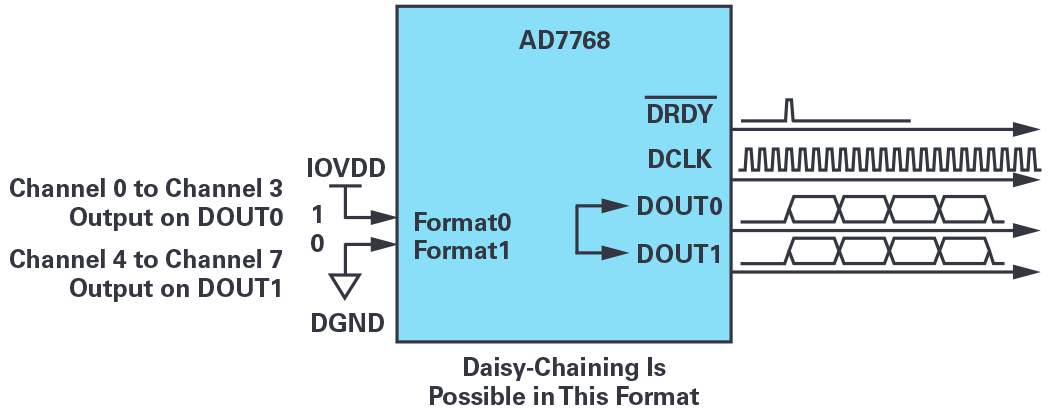

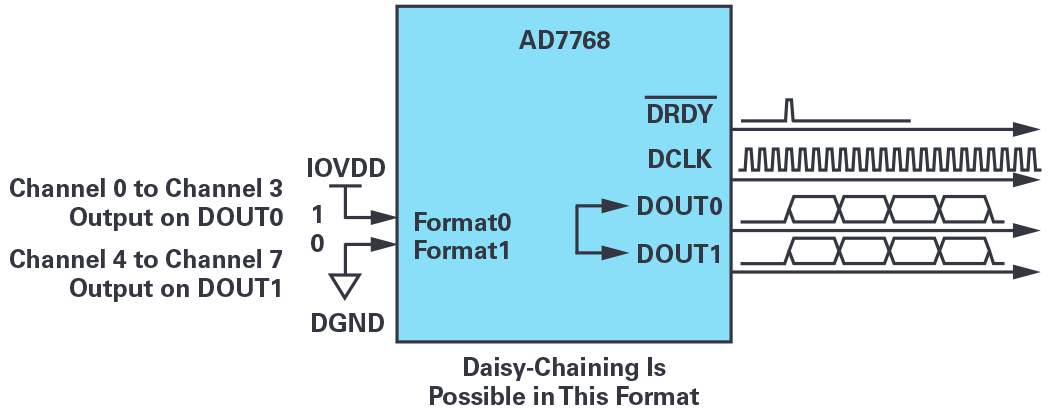

2002 目前許多精密模數(shù)轉(zhuǎn)換器 (ADC) 具有串行外設(shè)接口 (SPI) 或一些串行接口,用于與微控制器單元 (MCU)、DSP 或 FPGA 等控制器通信。控制器寫入或讀取ADC內(nèi)部寄存器并讀取轉(zhuǎn)換

2023-02-15 12:31:46 2759

2759

多片FPGA之間的互連,經(jīng)常提到多路復(fù)用的概念,也經(jīng)常提到TDM的概念,正確理解多路復(fù)用在多片FPGA原型驗(yàn)證系統(tǒng)中的機(jī)理,尤其是時(shí)序機(jī)制,對于我們正確看待和理解多片FPGA原型系統(tǒng)的性能有很好的促進(jìn)作用。下圖是一個(gè)使用多路復(fù)用器后接采樣FF的多路復(fù)用解決方案的示例。

2023-06-06 10:04:35 579

579

可重構(gòu)設(shè)計(jì)是指利用可重用的軟、硬件資源,根據(jù)不同的應(yīng)用需求,靈活地改變自身體系結(jié)構(gòu)的設(shè)計(jì)方法。FPGA器件可多次重復(fù)配置邏輯的特性使可重構(gòu)系統(tǒng)成為可能,使系統(tǒng)兼具靈活、便捷、硬件資源可復(fù)用等性能

2011-05-27 10:22:36

FPGA中SPI復(fù)用配置的編程方法SPI(Serial Peripheral InteRFace,串行外圍設(shè)備接口)是一種高速、全 雙工、同步的通信總線,在芯片的引腳上只占用4根線,不僅節(jié)約了芯片

2012-08-12 11:56:42

。正是出于這種簡單、易用的特性,現(xiàn)在越來越多的芯片集成了這種通信協(xié)議。FPGA中也有不少SPI復(fù)用配置的編程方法,但具體有哪些你們知道嗎?

2019-08-06 06:40:36

本帖最后由 eehome 于 2013-1-5 09:47 編輯

fpga實(shí)現(xiàn)spi接口FPGA實(shí)現(xiàn)SPI接口(包括主機(jī)和從機(jī)程序)

2012-08-11 18:07:40

為活動(dòng)(已配置)狀態(tài)。FPGA包括許多配置接口選項(xiàng),通常包括并行NOR總線和串行外設(shè)接口(SPI)總線。支持這些總線的存儲器在不同廠商的產(chǎn)品之間總是存在微小的不兼容性,增添了采購多款存儲器件的困難程度

2021-09-03 07:00:00

ATmega128通過SPI接口與FPGA通信哪位大神做過發(fā)數(shù)據(jù)FPGA收到就是收不到FPGA發(fā)送過來的數(shù)據(jù)。 FPGA可以準(zhǔn)確收到AVR傳過去的數(shù)據(jù)。一位都不錯(cuò)。可就是收不到,SPDR寄存器中什么也讀不到。求高人指點(diǎn)

2016-07-22 09:57:54

各位工程師,大家好。小弟使用的C6747,采用SPI0 FLASH的BOOT方式,由于系統(tǒng)中SPI設(shè)備較多,SPI1已經(jīng)接了很多從設(shè)備。因此希望SPI0接口在BOOT后可以繼續(xù)使用。我目前的想法

2020-05-22 15:02:37

列 GPIO的可復(fù)用的特殊端口有 RESET、外部晶振引腳、SWD、UART 編程接口等,用戶在不同的應(yīng)用當(dāng)中需要根據(jù)這些端口的特性及應(yīng)用特點(diǎn)選擇不同的復(fù)用方式。☆☆☆☆☆☆☆☆☆☆☆☆...

2021-12-06 06:34:22

開始之前,請閱讀 UG290,Gowin FPGA 產(chǎn)品編程配置手冊 SSPI 部分。SSPI(Slave SPI)配置模式,即 FPGA 作為從器件,由外部 Host 通過SPI 接口對 Gowin FPGA 產(chǎn)品進(jìn)行配置。

2022-09-30 06:07:09

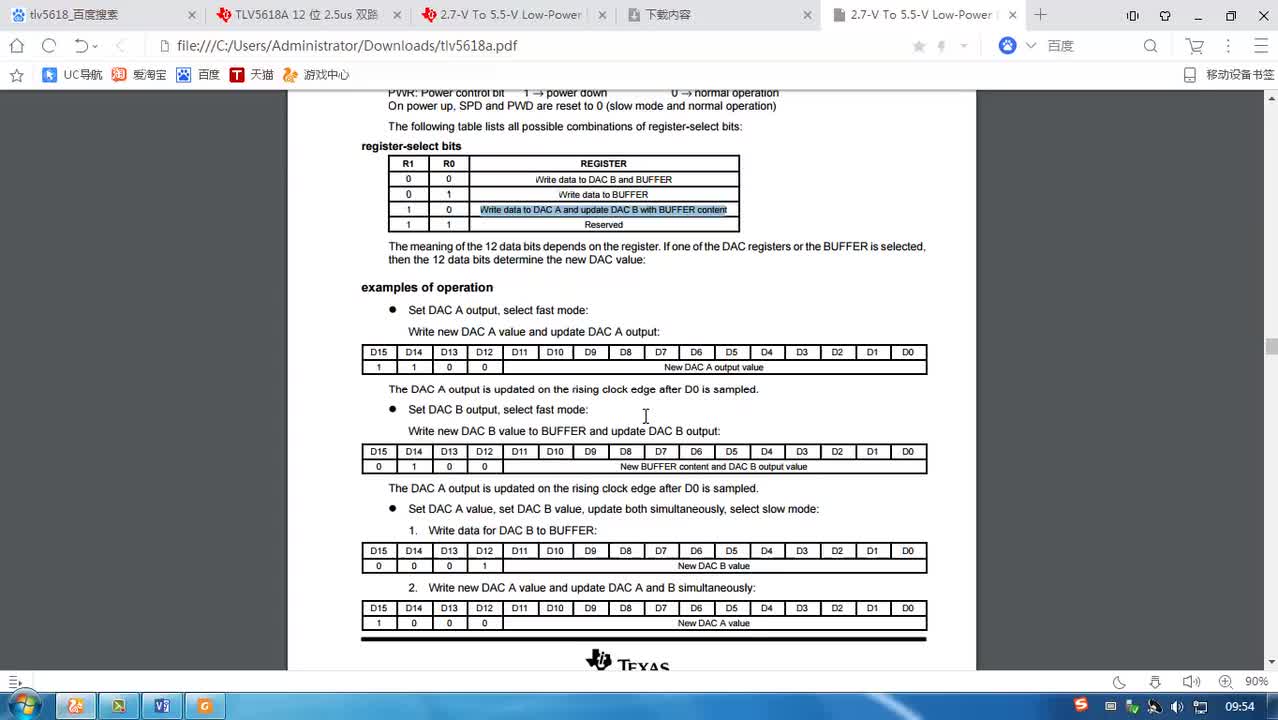

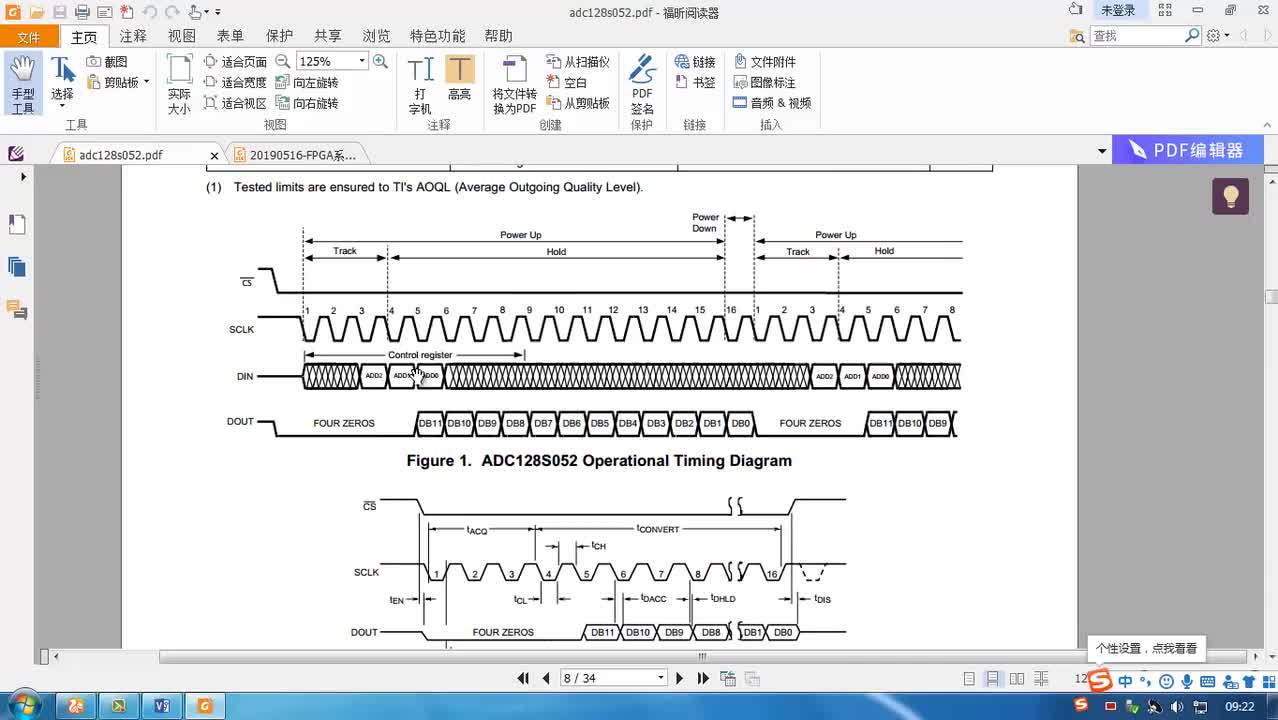

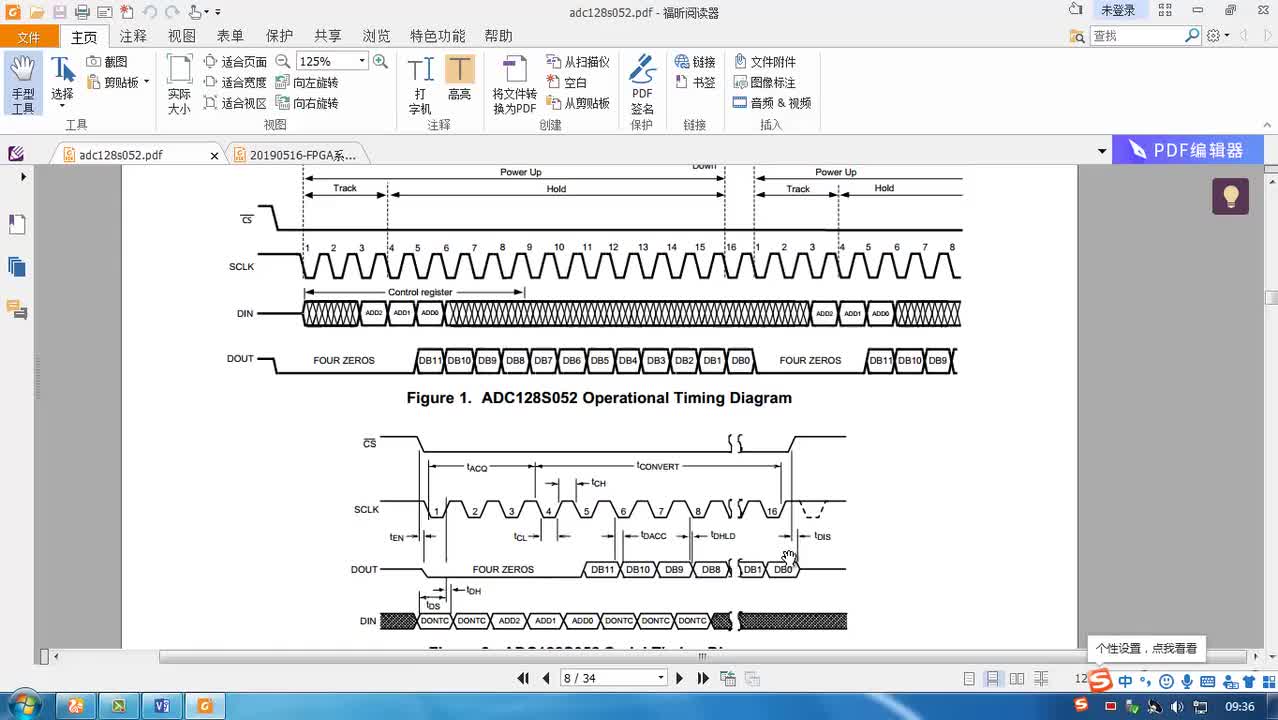

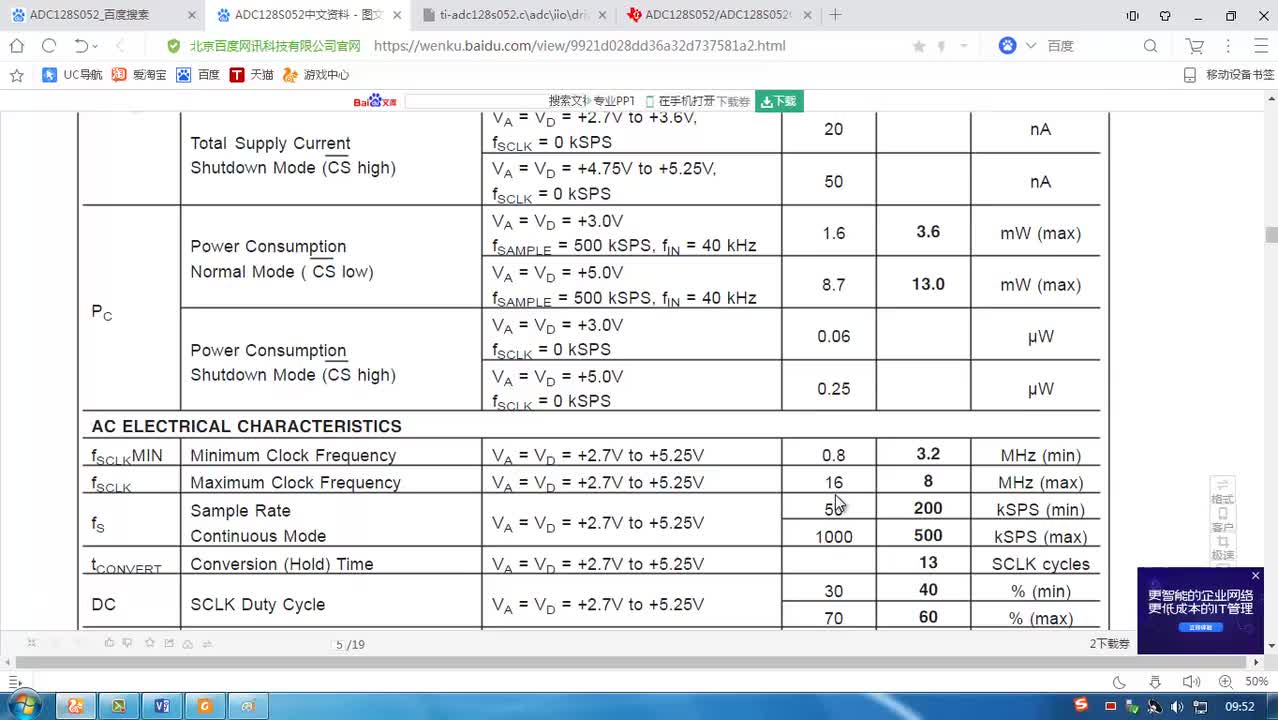

當(dāng)前許多精密模數(shù)轉(zhuǎn)換器(ADC)具有串行外設(shè)接口(SPI)或某種串行接口,用以與包括微控制器單元(MCU)、DSP和FPGA在內(nèi)的控制器進(jìn)行通信。控制器寫入或讀取ADC內(nèi)部寄存器并讀取轉(zhuǎn)換碼。SPI

2021-11-04 07:49:49

可用于FPGA和其它芯片之間來實(shí)現(xiàn)簡單而有效的溝通。SPI的項(xiàng)目第1部分:什么是SPI?第2部分:一個(gè)簡單的實(shí)現(xiàn)第3部分:應(yīng)用程序【FPGA設(shè)計(jì)實(shí)例】基于FPGA的SPI接口應(yīng)用 `

2012-03-26 15:47:42

的NOR總線和串行外圍設(shè)備接口(SPI)總線。支持這些總線的存儲器在不同制造商提供的產(chǎn)品之間始終存在很小的不兼容性,這使得存儲設(shè)備的多來源采購更加困難。 FPGA配置的歷史 FPGA首次面世時(shí)選擇的配置

2020-09-18 15:18:38

復(fù)用SPI掛載2個(gè)Device,一個(gè)是使用ST7567驅(qū)動(dòng)芯片的LCD,另一個(gè)是16Mbit的SPI FLASH。

問題現(xiàn)象不能同時(shí)工作,

使用了SPI1, 復(fù)用了MOSI和CLK,片選分別

2023-08-22 08:00:05

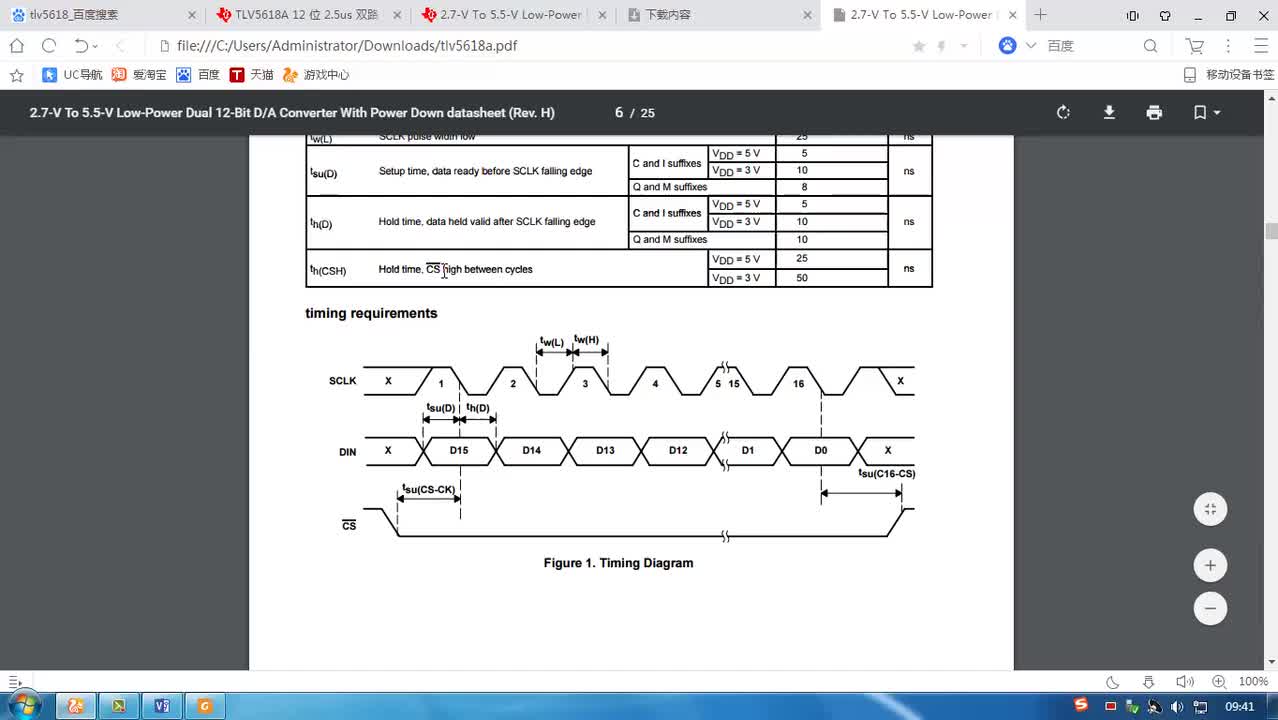

如SPI接口中,FPGA通過模擬產(chǎn)生時(shí)鐘和串行數(shù)據(jù)與一個(gè)外部芯片進(jìn)行通信,其建立和保持時(shí)間是有時(shí)序要求的,這個(gè)時(shí)序要求可以通過外部的手冊上獲得。那么在FPGA中模擬這個(gè)接口要如何保證這個(gè)時(shí)序要求呀

2023-04-23 11:35:02

/O的 FPGA,可滿足10Gb/s以上的通信系統(tǒng)的要求;而且用FPGA解決接口不兼容器件間的通信問題。因此本文 將提出一種新的基于FPGA 的SPI 接口設(shè)計(jì)方法。SPI(Serial

2019-05-28 05:00:05

的產(chǎn)物,具有設(shè)計(jì)周期短、可重復(fù)編程、靈活性強(qiáng)等特點(diǎn)。用FPGA 設(shè)計(jì)的SPI 總線具有可擴(kuò)展性強(qiáng)、便于修改等優(yōu)點(diǎn)。只要對設(shè)計(jì)做簡單的改動(dòng),即可對SPI 總線的數(shù)據(jù)位數(shù)、工作模式等進(jìn)行擴(kuò)展,充分發(fā)揮

2015-01-28 14:09:51

受到限制。因此,我們采用ALTERA公司的FPGA器件設(shè)計(jì)SPI總線的通信接口,該總線接口具有高速、配置靈活等優(yōu)點(diǎn),大大地縮短了系統(tǒng)的開發(fā)周期。

2019-08-09 08:14:34

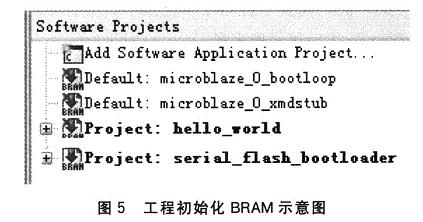

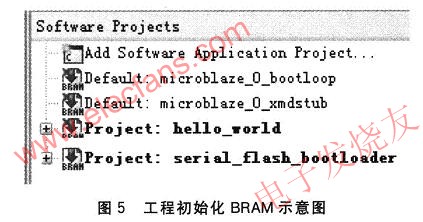

Flash對FPGA進(jìn)行加載。它適合作為FPGA硬件結(jié)構(gòu)的bit文件保存介質(zhì),如果應(yīng)用軟件工程編譯后的代碼較小,保存在同一片SPI FLash中(即復(fù)用SPI Flash)無疑是可行的最廉價(jià)方案。 由于本

2020-05-02 07:00:00

現(xiàn)在我用SPI接口連接一個(gè)存儲代碼的閃存,我能用這個(gè)接口與FPGA等其他芯片通信嗎?謝謝您!

2019-09-20 14:24:04

最近要測試兩個(gè)設(shè)備間的SPI通信,可手上只有一塊開發(fā)板,雖然將開發(fā)板上SPI1接口的MISO與MOSI短接之后可以實(shí)現(xiàn)自發(fā)自收,但是我還想多做一步:用一個(gè)芯片上的兩個(gè)SPI接口相互通信。測試

2022-02-17 08:05:13

嗨,大家好,我有一個(gè)ML507

FPGA和模擬信號(+/- 5V,100mA),數(shù)量約為40。我需要在電路和

FPGA之間設(shè)計(jì)一個(gè)帶有ADC的

接口以及多路

復(fù)用(對于多路

復(fù)用不夠緊張,因?yàn)槿绻斎牒陀邢?/div>

2020-06-15 06:59:40

本文介紹了一種FPGA和IPX2805之間的SPI4.2接口模塊設(shè)計(jì)的方法,對硬件設(shè)計(jì)進(jìn)行了說明,著重闡述了FPGA內(nèi)部SPI4.2接口模塊設(shè)計(jì)。

2021-05-06 09:22:44

你好, 我正在使用zynq zc702板。我必須使用SPI接口在ARM和FPGA之間進(jìn)行通信,請有人幫我怎么做?謝謝Deepak1991

2020-04-29 09:12:33

新手,求基于fpga的spi接口運(yùn)用實(shí)例,小弟感激不盡

2016-01-12 11:06:13

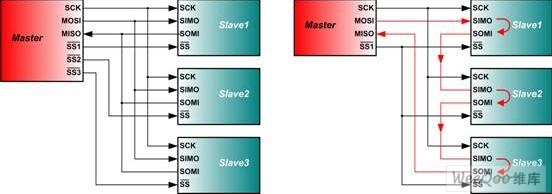

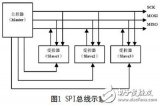

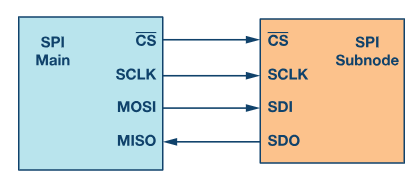

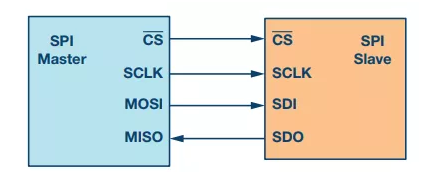

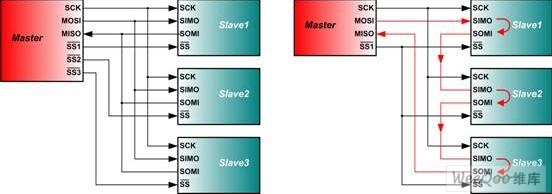

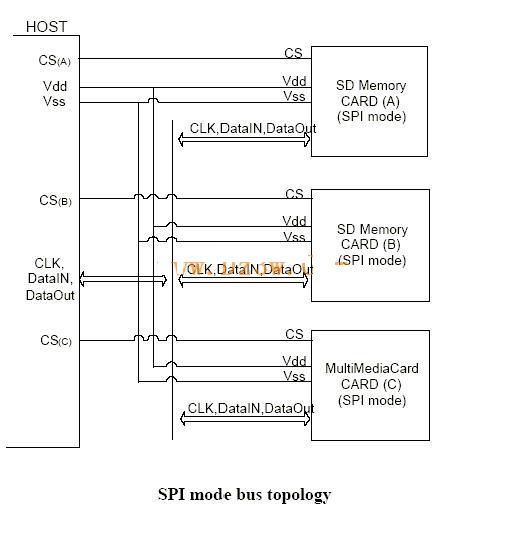

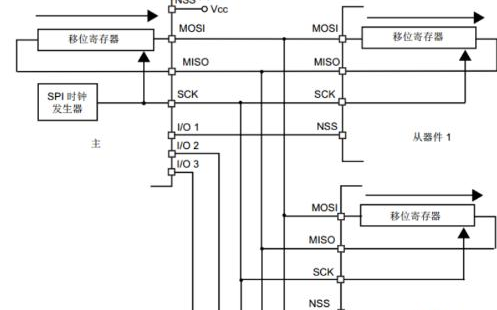

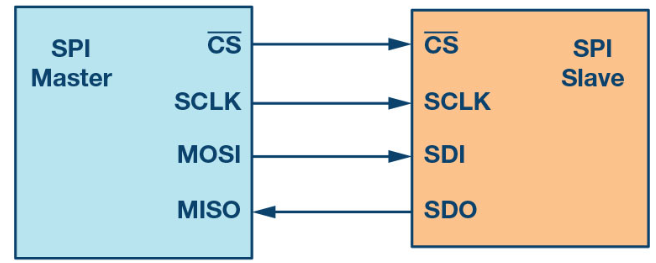

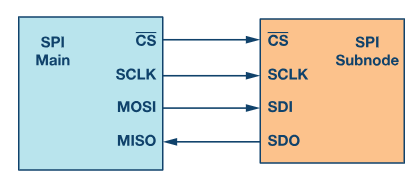

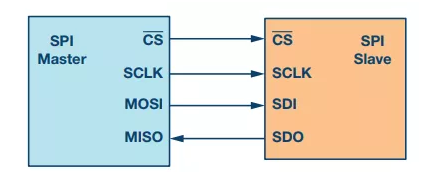

發(fā)送接收。三、設(shè)計(jì)原理本系統(tǒng)用硬件描述語言VHDL描述,可IP復(fù)用的通用結(jié)構(gòu)。 1、典型應(yīng)用SPI接口的典型應(yīng)用如圖1所示。微處理器與從設(shè)備通過發(fā)送指令的方式實(shí)現(xiàn)雙向數(shù)據(jù)傳輸。 2.1通信模塊這個(gè)模塊

2019-05-05 09:29:34

去偏移和包重組是在FPGA中實(shí)現(xiàn)SPI-4.2接口的核心難點(diǎn),在分析偏移和包重組原理的基礎(chǔ)上,給出基于FPGA的SPI-4.2接口的設(shè)計(jì)與實(shí)現(xiàn)方案,并對關(guān)鍵部分給出了硬件原理圖,在線測試結(jié)

2009-04-10 09:43:35 32

32 SPI接口讀寫串行EEPROM:93C46為采用3線串行同步總線SPI接口方式的EEPROM,其芯片引腳名稱和功能描述如圖1-1:

2009-09-19 11:39:27 89

89 基于FPGA的SPI自動(dòng)發(fā)送模塊的設(shè)計(jì):一、摘要:SPI 接口應(yīng)用十分廣泛,在很多情況下,人們會用軟件模擬的方法來產(chǎn)生SPI 時(shí)序或是采用帶SPI 功能模塊的MCU。但隨著可編程邏輯技

2009-10-04 08:44:40 25

25 本文介紹了一種FPGA和IPX2805之間的SPI4.2接口模塊設(shè)計(jì)的方法,對硬件設(shè)計(jì)進(jìn)行了說明,著重闡述了FPGA內(nèi)部SPI4.2接口模塊設(shè)計(jì)。該設(shè)計(jì)簡單、高效,解決了商用芯片不能滿足高速轉(zhuǎn)發(fā)的系

2010-07-28 16:56:32 33

33 MAX7456隨屏顯示(OSD)發(fā)生器具有SPI™兼容接口,本應(yīng)用筆記介紹了SPI接口的工作原理,文中還包含在微控制器內(nèi)逐位模擬SPI接口的控制器C程序。

2008-07-27 23:24:13 14438

14438

FPGA中SPI復(fù)用配置的編程方法

SPI(Serial Peripheral InteRFace,串行外圍設(shè)備接口)是一種高速、全雙工、同步的通信總線,在芯片的引腳上只占用4根線,不僅節(jié)約了芯片的引

2010-01-06 14:48:18 3062

3062

數(shù)字接口系列文章之SPI總線

串行外設(shè)接口 (SPI) 總線是一種運(yùn)行于全雙工模式下的同步串行數(shù)據(jù)鏈路。用于在單個(gè)主節(jié)點(diǎn)和一個(gè)或多個(gè)從節(jié)點(diǎn)之間交換數(shù)據(jù)。SPI 總線

2010-01-08 10:46:41 803

803

SPI(Serial Peripheral Interface,串行外圍設(shè)備接口)是一種高速、全雙工、同步的通信總線,在芯片的引腳上只占用4根線,不僅

2010-10-13 17:41:34 4734

4734

SPI接口總線介紹

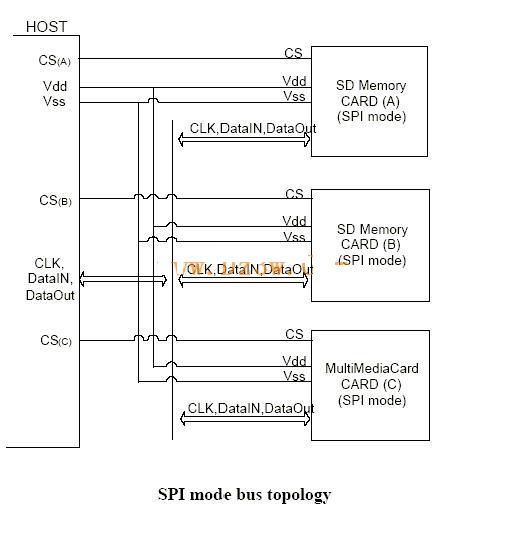

SPI 可以作為主、從器件工作,并可在同一總線上支持多個(gè)主、從器件。SPI 主要使用3 個(gè)信號。(1)主輸出、從

2010-11-24 08:41:32 4575

4575

SPI方式FPGA配置和SPI flash編程

2011-05-16 18:01:02 164

164 集成電路設(shè)計(jì)越來越向系統(tǒng)級的方向發(fā)展,解決模塊間的接口問題顯得尤為重要。SPI 串行總線是一種常用的標(biāo)準(zhǔn)接口,其使用簡單方便而且占用系統(tǒng)資源少,應(yīng)用相當(dāng)廣泛。本文將介紹

2011-06-10 16:32:53 52

52 SPI在芯片的管腳上只占用四根線,節(jié)約了芯片的管腳,同時(shí)為PCB的布局上節(jié)省空間,因此在基于FPGA的讀寫接口設(shè)計(jì)中,高速SPI是一種很好的選擇。

2011-07-04 09:45:05 6310

6310

SPI 串行總線是一種常用的標(biāo)準(zhǔn)接口,其使用簡單方便而且占用系統(tǒng)資源少,應(yīng)用相當(dāng)廣泛。本文將介紹一種新的通用的SPI 總線的FPGA 實(shí)現(xiàn)方法。

2011-09-09 11:58:27 67

67 使用的同步串行三線SPI接口,可以方便的連接采用SPI通信協(xié)議的外圍或另一片AVR單片機(jī),實(shí)現(xiàn)在短距離內(nèi)的高速同步通信.ATmega128的SPI為硬件接口和傳輸完成中斷申請,所以使用SPI傳輸數(shù)

2011-11-09 17:37:33 3660

3660 SPI 總線是一個(gè)同步串行接口的數(shù)據(jù)總線,具有全雙工、信號線少、協(xié)議簡單、傳輸速度快等特點(diǎn)。介紹了SPI 總線的結(jié)構(gòu)和工作原理,對4 種工作模式的異同進(jìn)行了比較,并著重分析了

2012-05-23 10:18:57 4112

4112

FPGA與SPI接口程序:使用xc3s400,時(shí)鐘50Mhz,串行DA 使用max544,max544使用的是SPI接口,所以要模擬SPI發(fā)送方式。其實(shí)最重要的就是精確的模擬出發(fā)送數(shù)據(jù)的時(shí)序圖。有用的就下吧。

2012-10-23 12:35:09 194

194 電子專業(yè)單片機(jī)開發(fā)中的學(xué)習(xí)教程資料——SPI接口

2016-08-08 15:17:40 20

20 SPI接口詳細(xì)說明

2016-12-23 02:11:24 8

8 SPI 接口應(yīng)用十分廣泛,在很多情況下,人們會用軟件模擬的方法來產(chǎn)生SPI 時(shí)序或是采用帶SPI 功能模塊的MCU。但隨著可編程邏輯技術(shù)的發(fā)展,人們往往需要自己設(shè)計(jì)簡單的SPI 發(fā)送模塊。本文介紹

2017-10-19 10:33:01 18

18 高速SPI和SCI接口

2017-10-20 10:29:04 10

10 SPI接口應(yīng)用十分廣泛,在很多情況下,人們會用軟件模擬的方法來產(chǎn)生SPI時(shí)序或是采用帶SPI功能模塊的MCU。但隨著可編程邏輯技術(shù)的發(fā)展,人們往往需要自己設(shè)計(jì)簡單的SPI發(fā)送模塊。本文介紹一種基于FPGA的將并行數(shù)據(jù)以SPI串行方式自動(dòng)發(fā)送出去的方法。

2017-11-24 15:32:02 1807

1807

問題有了好的解決方案。例如,現(xiàn)有的高性能接口IP及高速物理I/O的FPGA,可滿足10Gb/s以上數(shù)據(jù)通道的通信系統(tǒng)的要求;可以用FPGA實(shí)現(xiàn)接口不兼容器件間的通信問題。因此本文將提出一種新的基于FPGA 的SPI 接口設(shè)計(jì)方法。

2018-08-01 12:13:00 7218

7218

依據(jù)SPI同步串行接口的通信協(xié)議, 設(shè)計(jì)一個(gè)可配置的、高度靈活的SPI Master 模塊,以滿足正常、異常及強(qiáng)度測試要求。利用Verilog 語言實(shí)現(xiàn)SPI接口的設(shè)計(jì)原理和編程思想。

2018-11-05 17:42:38 10793

10793

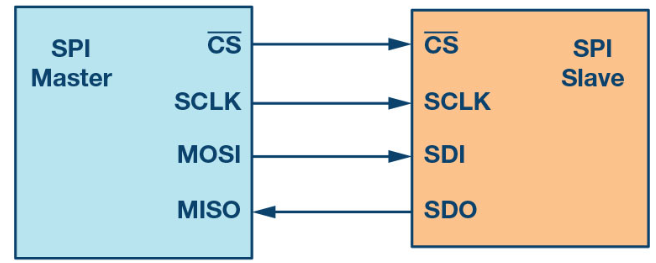

SPI 是一種同步、全雙工、主從式接口。來自主機(jī)或從機(jī)的數(shù)據(jù)在時(shí)鐘上升沿或下降沿同步。主機(jī)和從機(jī)可以同時(shí)傳輸數(shù)據(jù)。SPI 接口可以是3線式或4線式。

2018-11-13 16:45:44 19009

19009

)或某種串行接口,用以與包括微控制器單元(MCU)、DSP和FPGA在內(nèi)的控制器進(jìn)行通信。控制器寫入或讀取ADC內(nèi)部寄存器并讀取轉(zhuǎn)換碼。SPI的印刷電路板(PCB)布線簡單,并且有比并行接口更快的時(shí)鐘速率,因而越來越受歡迎。而且,使用標(biāo)準(zhǔn)SPI很容易將ADC連接到控制器。 一些新型ADC具有SP

2020-01-17 16:34:20 4668

4668 SPI,是Serial Peripheral interface(串行外設(shè)接口)縮寫。是Motorola首先在其MC68HCXX系列處理器上定義,用來做MCU與外設(shè)之間的通信接口。

2020-09-02 16:25:19 2164

2164

本文主要介紹STM32的SPI接口、cubeMX軟件配置SPI接口和分析SPI相關(guān)代碼。 STM32之SPI簡介: SPI協(xié)議【Serial Peripheral Interface】 串行外圍設(shè)備

2020-09-24 14:09:48 14561

14561

和 FPGA 在內(nèi)的控制器進(jìn)行通信。控制器寫入或讀取 ADC 內(nèi)部寄存器并讀取轉(zhuǎn)換碼。SPI 的印刷電路板(PCB)布線簡單,并且有比并行接口更快的時(shí)鐘速率,因而越來越受歡迎。而且,使用標(biāo)準(zhǔn) SPI 很容易將 ADC 連接到控制器。一些新型 ADC 具有 SPI,但有些 ADC 具有非標(biāo)準(zhǔn)的

2020-12-22 12:49:00 13

13 偏移和包重組是在FPGA中實(shí)現(xiàn)SPI一4.2接口的核心難點(diǎn),在分析偏移和包重組原理的基礎(chǔ)E,給出基于FPGA的SPI一4.2接口的設(shè)計(jì)與實(shí)現(xiàn)方案,并對關(guān)鍵部分給出r硬件原理圖,在線測試結(jié)果證明該方案可以實(shí)現(xiàn)SPI一4.2接口的功能。

2021-01-25 14:51:21 13

13 ADGS1612:SPI接口、1 Ω RON、±5 V、12 V、5 V、3.3 V、支持多路復(fù)用器配置、四通道SPST開關(guān)數(shù)據(jù)手冊(修訂版0)

2021-03-20 12:23:30 0

0 基于FPGA的SPI接口具體資料及電路圖

2021-03-22 09:47:25 10

10 UG-1209:ADGS5414SPI接口評估板,八路SPST開關(guān),13.5VRON,±20V/+36V,多路復(fù)用器可配置

2021-04-20 16:13:47 0

0 UG-1284:評估ADGS1408/ADGS1409SPI接口,4ΩRON,±15 V/+12 V/±5 V,1.8V邏輯控制,8:1/雙4:1復(fù)用器

2021-05-17 18:27:42 0

0 當(dāng)前許多精密模數(shù)轉(zhuǎn)換器(ADC)具有串行外設(shè)接口(SPI)或某種串行接口,用以與包括微控制器單元(MCU)、DSP和FPGA在內(nèi)的控制器進(jìn)行通信。控制器寫入或讀取ADC內(nèi)部寄存器并讀取轉(zhuǎn)...

2021-10-28 21:06:03 10

10 typora-copy-images-to: typora_picture基于FPGA與MCU通信的SPI協(xié)議設(shè)計(jì)1. SPI總線協(xié)議介紹及硬件設(shè)計(jì)1.1 SPI總線協(xié)議介紹及硬件設(shè)計(jì)SPI總線

2021-11-05 15:35:59 13

13 基于FPGA的SPI協(xié)議及設(shè)計(jì)實(shí)現(xiàn)博主微信:flm13724054952,不懂的有疑惑的也可以加微信咨詢,歡迎大家前來投稿,謝謝!引言介紹在電子通信領(lǐng)域里采用的通信協(xié)議有IIC,SPI,UART

2021-11-05 19:05:59 22

22 SPI接口電路的學(xué)習(xí)1、SPI接口電路原理SPI, Serial Perripheral Interface, 串行外圍設(shè)備接口, 是Motorola 公司推出的一種同步串行接口技術(shù)。 SPI 總線

2021-11-06 10:05:58 20

20 的時(shí)候,需要復(fù)用SPI引腳,因?yàn)樵撔酒挥幸粋€(gè)SPI接口。因此寫下一些調(diào)試心得。實(shí)際使用在使用時(shí),需要用一組## 標(biāo)題SPI口先驅(qū)動(dòng)AS3933,配置完成后,繼續(xù)用SPI口來驅(qū)動(dòng)另外一個(gè)芯片.上面兩個(gè)圖片表示了口線的復(fù)用以及SPI的復(fù)用規(guī)則,我們這里選擇的是CS0接DW1000以

2021-12-04 19:06:10 10

10 用的MCU是STM32F407,使用SPI1與SPI2相互通信,分別將PB3、PB4、PB5復(fù)用為SPI1,將PB13、PB14、PB15復(fù)用為SPI2,都不使用NSS管腳,兩個(gè)SPI接口之間的管腳連接如下...

2021-12-22 19:17:17 8

8 寫在前面SPI協(xié)議系列文章:FPGA實(shí)現(xiàn)的SPI協(xié)議(一)----SPI驅(qū)動(dòng) 在上篇文章,簡要介紹了SPI協(xié)議,編寫了SPI協(xié)議的FPGA驅(qū)動(dòng),但是在驗(yàn)證環(huán)節(jié),僅僅驗(yàn)證了發(fā)送時(shí)序,而沒有

2021-12-22 19:25:39 19

19 本文主要介紹STM32的SPI接口、cubeMX軟件配置SPI接口和分析SPI相關(guān)代碼。

2022-02-08 15:27:29 10

10 串行外設(shè)接口(SPI)是微控制器和外設(shè)IC之間使用最廣泛的接口之一,如傳感器、ADC、DAC、移位寄存器、SRAM等。SPI 是一個(gè)基于同步、全雙工主從的接口。來自主站或從站的數(shù)據(jù)在時(shí)鐘上升沿或下降沿同步。主站和從站都可以同時(shí)傳輸數(shù)據(jù)。SPI接口可以是3線或4線。

2022-10-24 14:52:54 10758

10758

數(shù)字接口(續(xù))— SPI 總線

2022-11-07 08:07:31 0

0 FPGA實(shí)現(xiàn)SPI協(xié)議

2023-03-20 10:35:02 0

0 FPGA中關(guān)于SPI的使用

2023-04-12 10:13:16 531

531 多片FPGA之間的互連,經(jīng)常提到多路復(fù)用的概念,也經(jīng)常提到TDM的概念

2023-06-06 10:07:37 221

221

串行外設(shè)接口(SPI)是微控制器和外圍IC(如傳感器、ADC、DAC、移位寄存器、SRAM等)之間使用較廣泛的接口之一。本文先簡要說明SPI接口,然后介紹ADI公司支持SPI的模擬開關(guān)與多路轉(zhuǎn)換器,以及它們?nèi)绾螏椭鷾p少系統(tǒng)電路板設(shè)計(jì)中的數(shù)字GPIO數(shù)量。

2023-06-17 09:13:17 4127

4127

的數(shù)據(jù)與主機(jī)產(chǎn)生的時(shí)鐘同步。同I2C接口相比,SPI器件支持更高的時(shí)鐘頻率。用戶應(yīng)查閱產(chǎn)品數(shù)據(jù)手冊以了解SPI接口的時(shí)鐘頻率規(guī)格。 SPI接口只能有一個(gè)主機(jī),但可以有一個(gè)或多個(gè)從機(jī)。圖1 顯示了主機(jī)和從機(jī)之間的SPI連接。 圖1. 含主機(jī)和從機(jī)的SPI配置 來自主機(jī)的片選信號用于選擇從機(jī)

2023-07-21 09:59:51 473

473

SPI 通用接口層 SPI 通用接口層把具體的 SPI 設(shè)備的協(xié)議驅(qū)動(dòng)和 SPI 控制器驅(qū)動(dòng)連接在一起。 負(fù)責(zé) SPI 系統(tǒng)與 Linux 設(shè)備模型相關(guān)的初始化工作。 為協(xié)議驅(qū)動(dòng)和控制器驅(qū)動(dòng)提供

2023-07-25 10:52:31 445

445 相信大家都玩過屏幕,在FPGA上使用最多的就是VGA/HDMI接口的顯示器了,這兩種顯示器的優(yōu)點(diǎn)就不用說了,缺點(diǎn)就是體積比較大,而且價(jià)格比較貴,對于追求便攜/價(jià)格低的我來說,SPI接口的屏幕才是我的首要選擇,而且一般是可以帶觸摸的哦。

2023-08-23 09:17:54 452

452

電子發(fā)燒友網(wǎng)站提供《將SPI閃存與7系列FPGA結(jié)合使用.pdf》資料免費(fèi)下載

2023-09-13 10:00:23 0

0 如何使用RS232轉(zhuǎn)SPI實(shí)現(xiàn)串口和SPI接口的轉(zhuǎn)換? RS232轉(zhuǎn)SPI是一種將串口和SPI接口進(jìn)行轉(zhuǎn)換的技術(shù),通常在需要將串口設(shè)備連接到SPI控制器的情況下使用。串口和SPI接口之間的轉(zhuǎn)換可以

2023-09-14 17:52:46 1154

1154 SPI和IIC接口一樣是非常常見的開發(fā)板接口,但與IIC相比,SPI設(shè)計(jì)了一種二進(jìn)制流的交互方式,擁有更快的傳輸速度,它可以在任何兩個(gè)嵌入式設(shè)備之間交換消息,ELF1開發(fā)板也是通過SPI接口連接

2023-12-06 15:49:57 425

425

當(dāng)前許多精密模數(shù)轉(zhuǎn)換器(ADC)具有串行外設(shè)接口(SPI)或某種串行接口,用以與包括微控制器單元(MCU)、DSP和FPGA在內(nèi)的控制器進(jìn)行通信。控制器寫入或讀取ADC內(nèi)部寄存器并讀取轉(zhuǎn)換碼。SPI

2024-01-09 08:23:17 190

190

電子發(fā)燒友App

電子發(fā)燒友App

評論