大家都在談論FinFET——可以說,這是MOSFET自1960年商用化以來晶體管最大的變革。幾乎每個人——除了仍然熱心于全耗盡絕緣體硅薄膜 (FDSOI)的人,都認為20 nm節點以后,FinFET將成為SoC的未來。但是對于要使用這些SoC的系統開發人員而言,其未來會怎樣呢?

回答這一問題最好的方法應該是說清楚FinFET對于模擬和數字電路設計人員以及SoC設計人員究竟意味著什么。從這些信息中,我們可以推斷出FinFET在系統級意味著什么。

FinFET有什么不同?

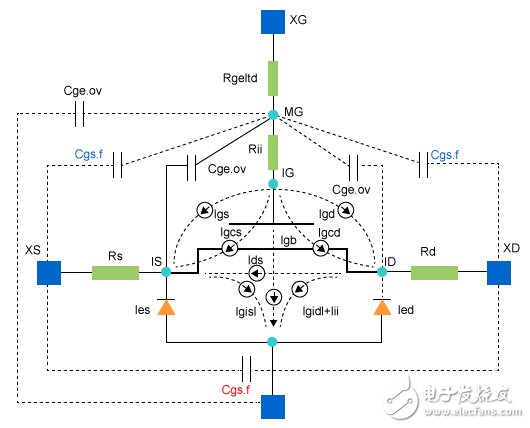

關于FinFET及其結構 (圖1) 理論的討論已經有很多了,這里我們不再重復這些討論。從電路設計人員的角度看,我們更關心FinFET究竟與平面MOSFET有什么不同。關于這一問題,今年的設計自動化大會(DAC)技術討論專題為模擬設計人員開辟了新思路。

圖1.FinFET經常出現在各種資料中

“采用FinFET進行模擬設計”而不是調侃的說“上帝一定瘋了”,這代表了四個專家的觀點:代工線代表TSMC的Eric Soenen,Globalfoundries的Richard Trihy、工具專家Synopsys的Navraj Nandra,以及設計經理Freescale的Scott Herrin。討論集中在新晶體管的電氣特性上。

在贊成一方,Herrin指出,FinFET能夠以很低的亞閾值泄漏電流實現高增益。

Nandra補充說,“FinFET固有增益很高,但是跨導(gm)實際上很低,和頻率(ft)一樣。更先進的幾何布局比平面器件更容易實現匹配,能夠很好的控制晶體管特性。結果是,您可以開發性能更好的電路。而且,還有其他的令人驚奇的地方。例如,輸出電流較小,因此,您開發的數據轉換器會更小。”

但是也有挑戰。Nandra說,gm和gd較低,而柵極泄漏較大,柵極電容要比同樣尺寸的平面器件大兩倍。正如Soenen所指出的,大家都知道的一點是,FinFET柵極寬度是量化的:圓晶上的每一個晶體管都有相同的標稱柵極寬度。因此,習慣于對每一晶體管采用w值的模擬設計人員只能并行采用一組同樣的FinFET——實際上,w作為電路參數可以是連續變量,直至一組正整數。

布板問題

通過采用多個最小寬度晶體管來替代寬度可調晶體管,量化會改變布板習慣。Nanda說,例如,Synopsys有一款工具將柵極寬度比例轉換為所需的翅片數。但是在另一討論組的研討中,Cadence硅片流程副總裁Anirudh Devgan提出了更嚴重的布板問題。

Devgan說:“采用更先進的幾何布局后,多模式會更加復雜。隨著復雜度的提高,很難預測設計規則錯誤。錯誤與環境相關。”

有些規則是熟悉的:例如,減小耦合的間隔規則,平板印刷的形狀規則等。雙模式增加了顏色規則,以保證最精細的模式能夠分成兩個獨立的掩膜。還有相對較新的布板相關效應,Devgan指出了其中的六個——包括非常接近和多間隔等,這對晶體管行為有很大的影響。為說明問題的嚴重性,Devgan指出,在20 nm已經有5,000條布板規則需要進行檢查。

對于模擬設計人員和數字單元庫開發人員,這么復雜的結果是,幾乎不可能開發DRC結構干凈的布板。由于提取和DRC帶來的布板問題,設計人員必須預測多次迭代。Devgan提醒說:“這需要幾個星期的時間。40%的設計時間都花在收斂上。”

建模挑戰

除了晶體管行為上的這些不同之外,電路設計人員在FinFET上還遇到了其他一些問題:仿真模型在結構上與平面MOSFET不同,會更復雜(圖2)。Trihy提醒說,“如果您看一下模型,雜散電容的數量增加了十倍。還不清楚桌面驅動的仿真器能否處理FinFET。”

圖2.FinFET仿真器模型會非常復雜

即使是如此復雜,也并不是所有模型在所有條件下都正確。因此,對于不熟悉平面晶體管的用戶,模型選擇會與電路相關,可能也會與布板相關。Herrin同意,“有不同點,您必須知道模型的局限性。”

Nandra說,Synopsys一直結合使用SPICE和TCAD工藝模型,以及BSIM-4公共多柵極模型,以實現FinFET電路的精確仿真。他說,即使是在亞閾值區,BSIM-4也的確實現了精確的行為模型。但是,用在電路仿真時,模型會非常復雜。Nandra承認,“您必須采用結構相關的方法來解決雜散問題。”

Trihy繼續這一主題。他問到,“器件模型會停在哪里,從哪里開始提取電路?采用FinFET電路,邊界是模糊的。您可以依靠設計規則來限制交互,但是,最后,最重要的可能不是模型的精度,而是提取的精度。”Devgan在他一次發言中,提醒說,在某些情況下,可能需要現場解決問題,對復雜的緊密封裝的3D結構進行精確的提取,FinFET電路會有這種結構。

新方法,新電路

晶體管行為、布板規則和建模方法出現了很大的變化,因此,適用于28 nm平面工藝的電路拓撲不太可能用在14 nm FinFET工藝上。量化會帶來一些挑戰。低電壓、受限的gm以及大柵極電容會導致其他變化,包括,限制扇出,處理壓縮動態范圍等。Soenen提醒說, “這不是電源技術,但我們計劃提供1.8 V FinFET。”Herrin解釋說,例如,在嵌入式應用中,電壓限制意味著完全不同的ESD電路,采用新方法來支持高電壓I/O。

Soenen和Nandra同意這些變化帶來的影響。Soenen預測說:“您會在模擬電路中看到很多數字輔助內容。會看到開關電容濾波器,更多的使用過采樣技術。”

Nandra補充說,“我們看到了FinFET之前還沒有的電路。”

芯片級

對于模擬電路和數字單元庫設計人員,小尺寸FinFET既有優點又有缺點。優點是更小的電路,更高的工作頻率,不用太擔心工藝變化,當然還有更低的亞閾值泄漏。缺點是,設計會更困難,需要更多的迭代才能達到收斂。一般而言,無法重用前幾代的設計。設計人員不得不建立新電路方法、拓撲和布板。新設計意味著更長的時間,更大的風險,速度、密度和功耗在晶體管級取得的進步可能因此而消失殆盡。

對于使用模塊和單元庫的芯片級設計人員,則完全不同。小尺寸FinFET僅在模塊和單元中比較復雜。芯片設計人員通常注意到了更小更快的模塊,這些模塊的靜態功耗會非常低。最后一點,與以前的產品相比,很多設計比較容易實現功耗管理。

但還是有問題。較低的工作電壓使得信號和電源完整性分析更加重要。對于綜合邏輯,較低的扇出使得時序收斂變得復雜。模塊級更困難的收斂意味著在最終集成階段要非常小心,不要打破任何東西。但這都是非常熟悉的問題,每一新工藝代都有這些問題。這當然不受歡迎。

總結

最后,對于將使用基于FinFET的SoC系統設計人員而言,這有什么含義?通過我們在這里的分析,并考慮到Intel 20 nm三柵極SoC在業界的應用經驗,得出了相同的結論。

設計鏈上每一個連續步驟——從晶體管到單元或者電路,從電路到功能模塊,從模塊到芯片,從芯片到系統,趨勢是發揮FinFET的優勢,克服挑戰。芯片設計人員獲得了更快、泄漏更低的庫,不需要知道單元設計人員是怎樣開發它們的。

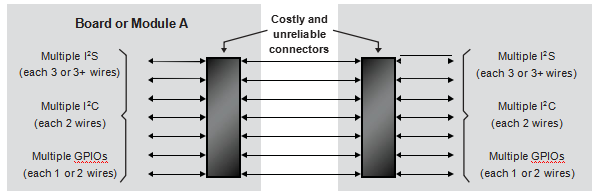

相似的,系統設計人員會看到組件密度更大的芯片——取決于結構,金屬或者聚乙烯間隔、接觸間隔或者柵極長度等工藝減小了面積,這提高了性能,有效的降低了泄漏電流。可能還有一些二階效應。例如,顯著降低的內核電壓會對電壓穩壓器提出新要求,要求降低噪聲,有很好的瞬變響應。某些SoC可能不支持傳統的高電壓I/O。

總之,對于系統開發人員,FinFET革命卻如所言:密度、速度和功耗都有巨大變化。還有更有趣的一點。對電路設計人員——特別是模擬設計人員提出要求,放棄熟悉的電路,FinFET在電路級帶動了關鍵的各類創新。新電路將帶動某些SoC在新的開放應用領域大放異彩。

電子發燒友App

電子發燒友App

評論