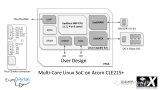

賽靈思為 Zynq?-7000 All Programmable SoC打造端對端Smarter Vision開發(fā)環(huán)境,大幅提升機(jī)器視覺應(yīng)用的設(shè)計(jì)生產(chǎn)力。

2013-11-27 09:34:39 810

810 本文主要介紹了面光源的結(jié)構(gòu)有哪些材料及其在設(shè)計(jì)生產(chǎn)過程中需注意的問題。

2016-03-15 15:09:16 2491

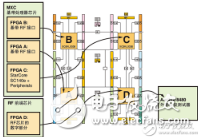

2491 內(nèi)核適用于美高森美 IGLOO2 FPGA、 SmartFusion2系統(tǒng)級芯片(SoC) FPGA或RTG4 FPGA,具備運(yùn)行于Linux平臺并基于Eclipse的SoftConsole集成開發(fā)環(huán)境(IDE)和Libero SoC設(shè)計(jì)套件,提供全面的設(shè)計(jì)支持。

2018-07-31 09:01:00 2959

2959 Actel公司軟件使用的是Libero,我正在調(diào)試一個(gè)程序,有誰知道怎么使用調(diào)試工具,就是和Quartus II 里面的Signaltap 軟件一樣的東西

2017-07-04 14:19:30

`本人即將大二,屆時(shí)將有數(shù)字電路這一課程,于是買了一塊FPGA開發(fā)板進(jìn)行實(shí)踐操作來鞏固知識。我買的開發(fā)板是周立功公司EasyFPGA030開發(fā)板,其核心是Actel公司的A3P030,需要用

2015-08-17 19:47:31

發(fā)現(xiàn)Altera官網(wǎng)上一個(gè)不錯(cuò)的視頻,講SoC FPGA嵌入式軟件的,都是干貨分享啊!系列視頻一共有5個(gè)視頻,視頻上傳了幾遍都上傳不了,大家還是去他們網(wǎng)站看吧:http://www.alteraforum.com.cn/showtopic-6634.aspx

2019-09-25 09:01:49

Altera公司意欲通過更先進(jìn)的制程工藝和更緊密的產(chǎn)業(yè)合作,正逐步強(qiáng)化FPGA協(xié)同處理器,大幅提升SoC FPGA的整體性能,為搶攻嵌入式系統(tǒng)市場版圖創(chuàng)造更大的差異化優(yōu)勢。隨著SoC FPGA在

2019-08-26 07:15:50

狀態(tài)中,我把這種處理方式稱為:基于代碼流監(jiān)控的讀心術(shù)。在soc fpga這個(gè)軟件和硬件都是可編程的領(lǐng)域里,一切皆有可能

2015-01-06 17:24:03

可以像軟件一樣通過編程來修改。FPGA有別于DSP、ARM、MCU的地方主要在于它的并行處理能力,它的強(qiáng)大并行性使復(fù)雜的運(yùn)算得到極大的速度比提升。 SOC: 系統(tǒng)芯片是一個(gè)將計(jì)算機(jī)或其他電子系

2017-04-13 08:55:14

STM32學(xué)習(xí)筆記①ARM、MCU、DSP、FPGA、SoC各是什么?區(qū)別是什么?(轉(zhuǎn))ARM、MCU、DSP、FPGA、SoC的比較CMSIS標(biāo)準(zhǔn)ARM、MCU、DSP、FPGA、SoC各

2021-12-09 07:08:05

`描述此參考設(shè)計(jì)提供為 Altera Cyclone V SoC FPGA 供電時(shí)所需的所有電源軌。此設(shè)計(jì)使用 LMZ3 系列模塊產(chǎn)生用于為 FPGA 供電的電源軌。`

2015-05-11 16:49:30

描述PMP9353 參考設(shè)計(jì)是 Altera Cyclone V SoC 器件的完整電源解決方案。此設(shè)計(jì)使用多個(gè) LMZ3 系列模塊、兩個(gè) LDO 和一個(gè) DDR 終端穩(wěn)壓器提供為 SoC 芯片供電

2015-05-11 16:45:44

%, 使用戶得以更快、更有預(yù)見性地創(chuàng)建產(chǎn)品。同時(shí),新型信號集成流引入了更高層次的自動化水平,使得快速設(shè)計(jì)所需要的預(yù)布線拓?fù)洹⒓s束開發(fā)和發(fā)展的性能導(dǎo)向數(shù)字電路模擬具有了更好的可用性和生產(chǎn)率。在新版本的發(fā)布會

2012-12-18 10:18:07

級設(shè)計(jì)領(lǐng)域的設(shè)計(jì)團(tuán)隊(duì)提供新技術(shù)和增強(qiáng)以提升易用性、生產(chǎn)率和協(xié)作能力,從而為PCB設(shè)計(jì)工程師樹立了全新典范。 “隨著供電電壓下降和電流需要增加,在設(shè)計(jì)PCB系統(tǒng)上的功率提交網(wǎng)絡(luò)

2008-06-19 09:36:24

Cyclone V SoC FPGA學(xué)習(xí)之路第二章:硬件篇(內(nèi)部資源)前言上一章了解了《cycloneV device datasheet》,其中數(shù)據(jù)手冊里重點(diǎn)介紹了電源要求,時(shí)序參數(shù)性能等。下面

2021-07-23 07:06:59

賽靈思公司(Xilinx)最新推出的ISE 12軟件設(shè)計(jì)套件,實(shí)現(xiàn)了具有更高設(shè)計(jì)生產(chǎn)力的功耗和成本的突破性優(yōu)化。ISE 設(shè)計(jì)套件首次利用“智能”時(shí)鐘門控技術(shù),將動態(tài)功耗降低多達(dá) 30%。

2019-08-20 08:33:19

) 和PolarFire ?片上系統(tǒng) (SoC) FPGA 產(chǎn)品組合。因此,基于 RISC-V 的設(shè)計(jì)具有更低的功耗、更高的靈活性、更快的上市時(shí)間,并提供 Linux 支持,而無需其他解決方案所需的權(quán)衡

2021-09-07 17:59:56

軟件生態(tài)系統(tǒng)的發(fā)展,對需要低功耗中端 SoC FPGA 的應(yīng)用來說是個(gè)好消息。”Microchip 面向 PolarFire SoC 和 Mi-V 生態(tài)系統(tǒng)的 Icicle 工具包能與以下服務(wù)集成

2020-09-25 11:39:42

Qt配置Altera SoC FPGA Kit 編譯器: GCC(Altera SoC) /home/terasic

2018-07-03 08:41:02

ArduZynq 和 TE0726-03M ZynqBerry SBC 中的 Zynq Z-7010 SoC 的 FPGA 容量存在顯著差異。雖然所有 Zynq-7000 SoC 都采用雙核 Arm

2018-08-31 14:43:05

,期待下一個(gè)十年我們能有新型高速的器件問世。4、如果我們關(guān)注一下一些專用芯片的功能框圖,比如LSI的sata raid的芯片,里面就是powerpc + 必要的硬件邏輯,這個(gè)模式在soc fpga中不就是

2015-01-06 17:32:00

原諒我記憶力不好。。。花了好久弄明白的東西才十個(gè)小時(shí)不到就忘記了,所以趁現(xiàn)在記得趕緊記錄下來。本文內(nèi)容:重建de1-soc中HPS-FPGA工程。 PS:原工程在http

2018-07-03 08:10:25

套件提供的system.xmp。 ISE檢測到.xmp文件與ISE v11.4項(xiàng)目相對應(yīng),并詢問我是否要將其轉(zhuǎn)換為v12.1。我說是的。現(xiàn)在,每次我想生成網(wǎng)表時(shí),platgen都會停止并顯示錯(cuò)誤:錯(cuò)誤

2019-08-19 10:05:14

本文由FPGA愛好者小梅哥編寫,未經(jīng)作者許可,本文僅允許網(wǎng)絡(luò)論壇復(fù)制轉(zhuǎn)載,且轉(zhuǎn)載時(shí)請標(biāo)明原作者。1、添加SoC硬件相關(guān)頭文件添加路徑D:\intelFPGA\17.1\embedded\ip

2020-02-16 18:38:28

下一個(gè)十年我們能有新型高速的器件問世。4、如果我們關(guān)注一下一些專用芯片的功能框圖,比如LSI的sata raid的芯片,里面就是powerpc + 必要的硬件邏輯,這個(gè)模式在soc fpga中不就是

2015-01-06 17:29:41

,期待下一個(gè)十年我們能有新型高速的器件問世。4、如果我們關(guān)注一下一些專用芯片的功能框圖,比如LSI的sata raid的芯片,里面就是powerpc + 必要的硬件邏輯,這個(gè)模式在soc fpga中不就是

2015-01-06 17:33:09

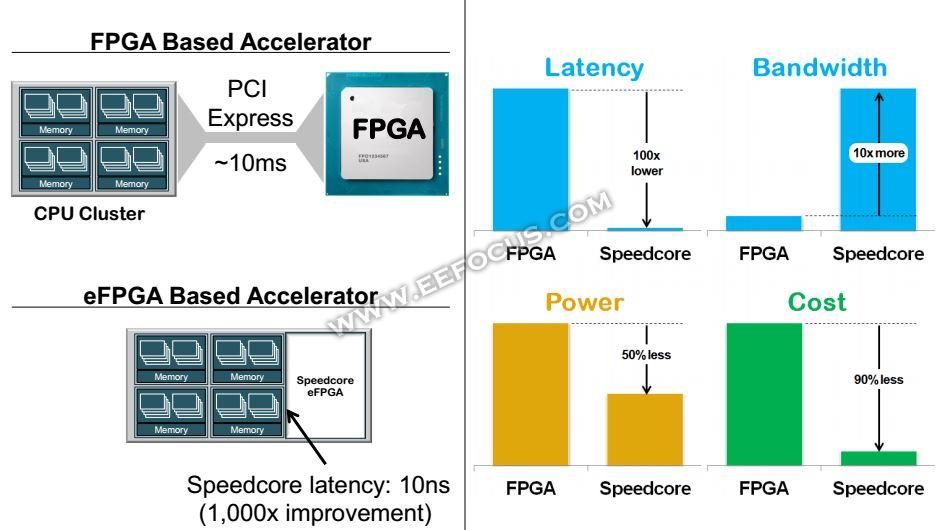

盡管FPGA已經(jīng)日益廣泛應(yīng)用于各種系統(tǒng),但大部分供應(yīng)商僅采用兩種頗為狹窄但截然不同的FPGA結(jié)構(gòu)。市場區(qū)別很清楚,一邊是集成多個(gè)應(yīng)用處理器內(nèi)核的高端SoC FPGA,另一邊是主要包含邏輯單元的低端

2019-10-15 06:04:47

能夠降低驗(yàn)證成本并能更早實(shí)現(xiàn)驗(yàn)證sign-off的方法都是眾人的注目焦點(diǎn)。 ***工業(yè)技術(shù)研究院 (工研院, ITRI) 在今年的設(shè)計(jì)自動化大會(2011 DAC)提出的案例研究,提出一種能夠顯著提升客

2011-07-24 09:47:50

大家好!我在電路板上的第一條消息......我的問題:當(dāng)使用Impact 11.4和Platform cable USB II對我的xc3s250e進(jìn)行編程時(shí),它有時(shí)會在編程后變得非常熱。沒有燃燒

2019-01-11 11:07:25

我用的是libero9.1,集成的仿真軟件只有modelsim,現(xiàn)在我想用modelsim仿真,有以下幾點(diǎn)問題。1.從libero中進(jìn)入modelsim需要自己建立工程嗎?我試過在libero中把

2014-03-20 14:32:19

的生產(chǎn)率。通過J-Link調(diào)試和Flash編程,可以使用完整的工具生態(tài)系統(tǒng)。”任何合格的工程師都可以在一兩天內(nèi)為J-Link和RISC-V編寫閃存加載器。SEGGER還提供根據(jù)需要為特定設(shè)備編寫閃存裝載

2021-03-09 19:35:13

如何利用SoC電表計(jì)量芯片提升電表設(shè)計(jì)?

2021-05-14 06:45:58

影響FPGA設(shè)計(jì)周期生產(chǎn)力的最大因素是什么?如何提高FPGA設(shè)計(jì)生產(chǎn)力?

2021-05-06 09:26:04

所有,我目前在我的Windows機(jī)器上安裝了Xilinx 11.4工具鏈(ISE,XPS,SDK等)。但是我想在我的機(jī)器上安裝Xilinx 12.4。我需要啟動和運(yùn)行,因?yàn)槲矣泻芏嗍褂肐SE

2018-11-26 14:47:42

基于FPGA的新型數(shù)字微鏡芯片測試系統(tǒng)一、概述2014年,國務(wù)院印發(fā)《國家集成電路產(chǎn)業(yè)發(fā)展推進(jìn)綱要》,將集成電路發(fā)展上升為國家戰(zhàn)略。在集成電路產(chǎn)業(yè)蓬勃發(fā)展的同時(shí),集成電路測試行業(yè)成為了不可缺少的一環(huán)

2021-08-06 09:32:20

打開Libero Soc11.8,一出現(xiàn)界面就又不行了,打開別的軟件就沒問題,不知道什么原因。電腦比較久了,是i3的,萬能的發(fā)燒友能否告訴我是什么原因,是軟件兼容問題還是電腦硬件問題。軟件用了沒多長時(shí)間,一個(gè)禮拜多,剛開始還好好的。

2017-07-08 14:15:38

求介紹平板電腦電路板設(shè)計(jì)生產(chǎn)企業(yè)。。求介紹平板電腦電路板設(shè)計(jì)生產(chǎn)企業(yè)。。謝謝各位大大。。。。

2014-01-03 18:18:34

寫在前面;很久很久之前買了ZLG的EasyFPGA板子,是Actel的ProASIC A3P060的芯片。問題起因;本人為愚鈍的菜鳥,而且英文一竅不通。又不想用Libero IDE版本,于是就

2016-01-18 14:57:07

寬度偏差每減小1mm,成材率可以提高0.1%左右,因此尺寸精密測量與控制技術(shù)可顯著提高經(jīng)濟(jì)效益和產(chǎn)品競爭力。測寬儀應(yīng)用于鋼板的在線生產(chǎn)線上,為其提供高質(zhì)量的在線寬度測量,并可將測量數(shù)據(jù)傳輸

2018-08-30 09:07:07

是奧地利微電子和西門子的合作成果,這項(xiàng)合作開始于2005年,旨在根據(jù)腫瘤學(xué)家和其他醫(yī)療專業(yè)人員的需求,生產(chǎn)新一代光探測器模塊,并從根本上提升性能。 醫(yī)療專業(yè)人員對新型CT設(shè)備有兩項(xiàng)關(guān)鍵要求: ? 更高分辨率

2012-12-20 14:24:45

獵頭職位:FPGA軟件工程師【上海】崗位描述:1. 根據(jù)系統(tǒng)需求,參與FPGA器件選型、方案設(shè)計(jì),負(fù)責(zé)邏輯設(shè)計(jì)、仿真和調(diào)試;2. 編寫FPGA設(shè)計(jì)文檔、測試文檔與使用文檔等;3. 協(xié)助硬件工程師完成

2017-02-17 11:06:31

FPGA Editor如何提升設(shè)計(jì)效率?如何利用CTRL / Shift快捷鍵進(jìn)行放大縮小?如果利用F11鍵放大選定的項(xiàng)目?

2021-04-08 06:40:00

。這是雙方工程團(tuán)隊(duì)為進(jìn)一步提升良率、增強(qiáng)可靠性并縮短生產(chǎn)周期而努力合作的成果。Virtex-6系列通過生產(chǎn)驗(yàn)證,意味著聯(lián)華電【關(guān)鍵詞】:生產(chǎn)驗(yàn)證,高性能,電子,可靠性,生產(chǎn)周期,系列,制造工藝,生產(chǎn)

2010-04-24 09:06:05

PCB板子已經(jīng)發(fā)給廠家了,改不回來了,真是怪自己還沒優(yōu)化好程序,就急急忙忙的把板子發(fā)出去了。 復(fù)位信號必須接到Libero soc支持的芯片的全局引腳,我接到了個(gè)普通IO,在開發(fā)環(huán)境中分配引腳

2018-01-07 22:31:39

ASIC與SoC器件的成本不斷上升,迫使半導(dǎo)體廠商不斷擴(kuò)大每種器件的市場應(yīng)用范圍,以提高投資回報(bào)率。軟件使用的趨勢還在不斷加強(qiáng),這作為一種有效的機(jī)制,擴(kuò)大了單個(gè)器件的市場使用范圍,因?yàn)?b class="flag-6" style="color: red">軟件內(nèi)容能帶

2019-07-11 08:25:57

常年使用一種 EDA 工具顯然可以提高效率,同時(shí)也會讓您習(xí)慣于自己所用的 PCB 設(shè)計(jì)工具,接受該工具的所有優(yōu)缺點(diǎn)。不過,隨著當(dāng)今技術(shù)的快速發(fā)展,我們需要考慮做出改變,繼而引入最新的技術(shù)方法。本文經(jīng) PCB 設(shè)計(jì)雜志授權(quán)翻印,其中討論了阻礙 PCB 設(shè)計(jì)流程的生產(chǎn)率問題。

2019-10-14 06:27:31

器門陣列(FPGA)和片上系統(tǒng)軟件(SoC)的工業(yè)生產(chǎn)系統(tǒng)軟件必須好幾個(gè)電源軌,另外遭遇小規(guī)格和成本低的挑戰(zhàn)。集成柔性功率器件能夠?yàn)檫@類運(yùn)用明顯控制成本,減少解決方案規(guī)格。 集成柔性功率器件在同一封裝

2020-07-01 09:09:21

美元的低功耗 RISC-V 開發(fā)板讓人眼前一亮。Microchip Icicle 工具包內(nèi)置 PolarFire SoC,將加速 RISC-V 軟件生態(tài)系統(tǒng)的發(fā)展,對需要低功耗中端 SoC FPGA

2021-03-09 19:48:43

基于FPGA 的SOC 系統(tǒng)中的串口設(shè)計(jì)

作者:葛銳 歐鋼摘要:本文在XILINX FPGA 中采用嵌入式處理器Picoblaze 進(jìn)行SOC 設(shè)計(jì),以較少的

2010-02-08 09:48:37 21

21 詳細(xì)介紹了在Actel公司Libero集成開發(fā)環(huán)境下,利用各種集成的工具和EDA軟件進(jìn)行FPGA設(shè)計(jì)的過程和方法。通過具體實(shí)例,介紹了通過混合使用VHDL硬件編程語言、SmartDesign、IP核等多種設(shè)

2010-07-26 15:19:28 36

36 優(yōu)化上料組合、提高生產(chǎn)率

隨著SIPLACE SiCluster Professional優(yōu)化軟件的面世,西門子電子裝配系統(tǒng)有限公司(

2009-11-24 17:12:56 529

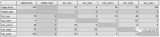

529 TI推出多核SoC顯著簡化通信基礎(chǔ)局端設(shè)備的設(shè)計(jì)

日前,德州儀器 (TI) 宣布推出一款基于 TI 多核數(shù)字信號處理器 (DSP) 的新型片上系統(tǒng) (SoC) 架構(gòu),該架構(gòu)在業(yè)界性能最高

2010-02-23 16:46:14 589

589 PROTEL 99設(shè)計(jì)生產(chǎn)18個(gè)基本步驟

一、電路板設(shè)計(jì)的先期工作 1、利用原理圖設(shè)計(jì)工具繪制原理圖,并且生成對應(yīng)的網(wǎng)絡(luò)表。當(dāng)然,有些特

2010-04-26 12:05:44 1765

1765 第1章 License設(shè)置 本文介紹一下Libero 軟件的快速入門。 Libero 軟件是Actel FPGA 的開發(fā)環(huán)境,它支持Actel 公司所有的FPGA 芯片。在安裝完Libero 軟件后,要設(shè)

2010-06-07 08:23:53 10461

10461 臺灣工業(yè)技術(shù)研究院提出一種能夠顯著提升客制化FPGA原型板驗(yàn)證效率的創(chuàng)新方法,自動化現(xiàn)有的 電路仿真 (in-circuit emulation)偵錯(cuò)功能,并提供更高的FPGA能見度。這個(gè)以FPGA為基礎(chǔ)的SoC驗(yàn)

2011-09-09 11:35:24 871

871

Altera公司(Nasdaq: ALTR)今天宣布可以提供FPGA業(yè)界的第一個(gè)虛擬目標(biāo)平臺,支持面向Altera最新發(fā)布的SoC FPGA器件立即開始器件專用嵌入式軟件的開發(fā)。在Synopsys有限公司成熟的虛擬原型開發(fā)解

2011-10-13 09:15:28 678

678 美高森美公司發(fā)布Libero? SoC v10.0 (第十版Libero? SoC)。這一新版Libero集成式設(shè)計(jì)環(huán)境(IDE)可為系統(tǒng)單芯片(SoC)設(shè)計(jì)人員提供多項(xiàng)新功能,包括提升易用性、增加嵌入式設(shè)計(jì)流程的集成度,以

2011-12-20 09:02:58 919

919 本文是關(guān)于Altera公司SoC FPGA 的用戶手冊(英文版) 。文中主要介紹了什么是SoC FPGA、SoC FPGA相關(guān)知識介紹、為什么要使用SoC FPGA以及SoC FPGA都應(yīng)用到哪些方面。

2012-09-05 14:03:08 153

153 全球電子設(shè)計(jì)創(chuàng)新領(lǐng)先企業(yè)Cadence設(shè)計(jì)系統(tǒng)公司(NASDAQ: CDNS)今天發(fā)布了新版 Incisive? 功能驗(yàn)證平臺,再一次為整體驗(yàn)證性能和生產(chǎn)率設(shè)定新標(biāo)準(zhǔn)。

2014-01-16 17:36:13 1047

1047 開創(chuàng)性FPGA軟件供應(yīng)商Plunify? Pte. Ltd.今日發(fā)布其支持Altera 的FPGA和SoC的InTimeTM設(shè)計(jì)優(yōu)化軟件。

2014-11-21 10:54:49 1552

1552 2014年,12月16號,北京——Altera公司(Nasdaq: ALTR)今天發(fā)布其Quartus? II軟件v14.1,擴(kuò)展支持Arria? 10 FPGA和SoC——FPGA業(yè)界唯一具有硬核浮點(diǎn)DSP模塊的器件,也是業(yè)界唯一集成了ARM處理器的20 nm SoC FPGA。

2014-12-16 13:48:53 1396

1396 致力于在功耗、安全、可靠和性能方面提供差異化半導(dǎo)體技術(shù)方案的領(lǐng)先供應(yīng)商美高森美公司(Microsemi Corporation,紐約納斯達(dá)克交易所代號:MSCC)宣布推出最新11.7版本Libero系統(tǒng)級芯片(SoC),這是用于美高森美現(xiàn)場可編程邏輯器件(FPGA)產(chǎn)品的全面FPGA設(shè)計(jì)工具套件。

2016-03-30 10:12:09 1242

1242 提高FPGA設(shè)計(jì)生產(chǎn)力的工具、技巧和方法,9影響FPGA設(shè)計(jì)周期生產(chǎn)力的最大因素是什么?

2017-02-11 12:22:06 587

587

致力于在功耗、安全、可靠性和性能方面提供差異化半導(dǎo)體技術(shù)方案的領(lǐng)先供應(yīng)商美高森美公司發(fā)布Libero系統(tǒng)級芯片(SoC)軟件的 v11.8最新版本。這是一款綜合性可編程邏輯器件(FPGA)設(shè)計(jì)工具,具有混合語言仿真等重要性能改進(jìn),還有同級最佳調(diào)試功能,以及一個(gè)全新網(wǎng)表視圖。

2017-04-27 11:50:09 1560

1560 門陣列(FPGA)做為安謀國際核心測試芯片,進(jìn)而建構(gòu)SoC原型制作平臺。 驗(yàn)證SoC設(shè)計(jì) FPGA原型最穩(wěn)當(dāng) FPGA原型制作是在FPGA上實(shí)作SoC或特定應(yīng)用集成電路(ASIC)設(shè)計(jì)的方法,并進(jìn)行硬件驗(yàn)證和早期軟件開發(fā)。

2018-05-11 09:07:00 2405

2405

當(dāng)前SoC是從算法研究人員到硬件設(shè)計(jì)人員,乃至軟件工程師和芯片布局團(tuán)隊(duì)等眾多專家的工作結(jié)晶,在項(xiàng)目不斷發(fā)展的同時(shí),各類專家也都有自己的需求。SoC 項(xiàng)目的成功很大程度上取決于上述各類專家所使用的硬件驗(yàn)證、軟硬件聯(lián)合驗(yàn)證以及軟件驗(yàn)證的方法,基于FPGA原型設(shè)計(jì)可為每一類專家?guī)砀鞣N不同的優(yōu)勢。

2017-11-24 17:04:01 2445

2445

全球領(lǐng)先的功率、安全性、可靠性和性能差異化之半導(dǎo)體解決方案供應(yīng)商美高森美公司(Microsemi Corporation)宣布提供新型超安SmartFusion2? SoC FPGA和 IGLOO2

2018-04-28 15:50:00 880

880 美高森美公司(Microsemi Corporation)宣布推出最新11.7版本Libero系統(tǒng)級芯片(SoC),這是用于美高森美現(xiàn)場可編程邏輯器件(FPGA)產(chǎn)品的全面FPGA設(shè)計(jì)工具套件

2018-08-08 14:28:00 1388

1388 美高森美公司(Microsemi) 宣布發(fā)布用于其最新現(xiàn)場可編程門陣列(FPGA)產(chǎn)品開發(fā)的綜合設(shè)計(jì)軟件工具的最新版本Libero SoC Version 11.6。除了新增針對用于航空航天市場

2018-08-19 09:04:00 2088

2088 關(guān)鍵詞: System Builder , SmartFusion FPGA 帶有System Builder設(shè)計(jì)工具的Libero SoC軟件可以加快SmartFusion2的開發(fā)和縮短客戶的上市

2018-09-25 09:07:01 513

513 隨著人工智能技術(shù)應(yīng)用到標(biāo)準(zhǔn)化、重復(fù)性的機(jī)械自動化過程,銀行和保險(xiǎn)等行業(yè)的后勤工作崗位不僅在數(shù)量上逐漸減少,而且在形式上也在發(fā)生改變。“半人馬智能”(即人機(jī)合作智能)在軟件編程等核心工作領(lǐng)域逐漸興起。它將人工智能與人類能力相結(jié)合,形成一種共生關(guān)系,推動生產(chǎn)率的顯著提升。

2019-01-17 09:24:53 2256

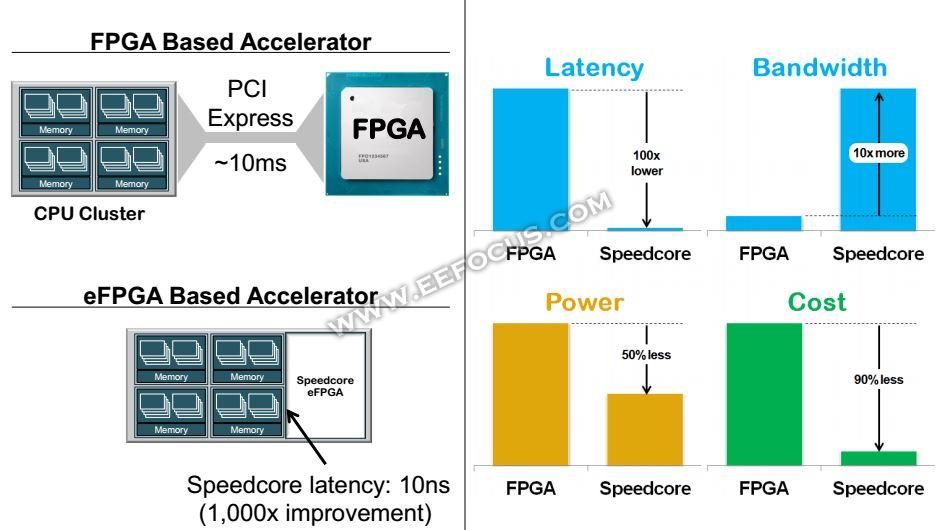

2256 很低,這也是為何獨(dú)孤的PowerPC和FPGA要結(jié)合ARM 弄SoC的原因之一。可以不夸張地說,FPGA SoC是對ARM架構(gòu)的MPU一場赤裸裸的打劫! eFPGA即嵌入式FPGA(embedded

2019-01-17 17:18:08 5564

5564

本文將深入介紹Libero IDE中集成的大部分軟件的使用流程,包括SmartDesign、ViewDraw、ModelSim、 Synplify、 Designer 和FlashPro的使用。

2019-04-23 08:00:00 55

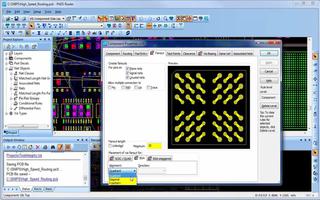

55 參加本研討會可了解 PADS VX 版如何提高全流程的設(shè)計(jì)生產(chǎn)率。

2019-05-20 06:10:00 1964

1964

PADS 包括可為射頻和微波設(shè)計(jì)提供消除手工操作、提高生產(chǎn)率的高級功能。

2019-05-15 06:16:00 2540

2540

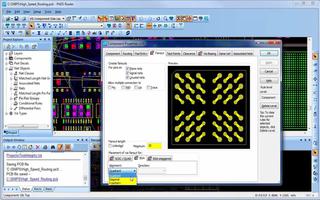

PADS 為高速網(wǎng)絡(luò)布線提供了一個(gè)可擴(kuò)展的環(huán)境,在該環(huán)境中可進(jìn)行交互和自動兩種模式。高速網(wǎng)絡(luò)的規(guī)則,例如匹配長度、差分對等,非常容易設(shè)置。在布線過程中,您將得到針對關(guān)鍵和敏感網(wǎng)絡(luò)的實(shí)時(shí)布線長度反饋。PADS 高速布線可成為提高您 PCB 設(shè)計(jì)生產(chǎn)率的“利器”。

2019-05-14 06:02:00 3230

3230

小梅哥最新款FPGA_SOC

2019-05-28 06:09:34 3982

3982 小梅哥最新款FPGA_SOC

2019-09-02 06:02:00 2139

2139

小梅哥最新款FPGA_SOC

2019-08-30 06:10:00 3548

3548

小梅哥最新款FPGA_SOC

2019-08-30 06:08:00 1733

1733

詳解ASIC芯片設(shè)計(jì)生產(chǎn)流程的PPT

2019-07-16 15:37:14 10081

10081 ? Prime設(shè)計(jì)軟件。 Altera的新軟件環(huán)境建立在公司經(jīng)過驗(yàn)證的用戶友好型Quartus II軟件之上,并采用了以生產(chǎn)力為中心的新型Spectra-Q?引擎。新的Quartus Prime設(shè)計(jì)軟件經(jīng)過

2019-08-09 11:04:26 2798

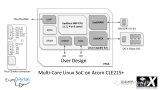

2798 英特爾的SoC開發(fā)套件提供了開發(fā)定制ARM快速和簡單的方法*處理器的SoC設(shè)計(jì)。設(shè)計(jì)生產(chǎn)率是Arria 10 SoC架構(gòu)的驅(qū)動理念之一。Arria 10 SoC提供與上一代SoC的完全軟件兼容性

2020-05-20 14:05:56 1244

1244 FPGA —— Virtex UltraScale+ VU19P。其擁有 350 億個(gè)晶體管,具備有史以來單顆芯片最高邏輯密度和最大I/O 數(shù)量,可以支持未來最先進(jìn) ASIC 和 SoC 技術(shù)的仿真與原型設(shè)計(jì)。與此同時(shí),還廣泛支持測試測量、計(jì)算以及網(wǎng)絡(luò)等相關(guān)應(yīng)用。 ? 高端 FPGA 新標(biāo)

2021-06-16 11:29:28 1552

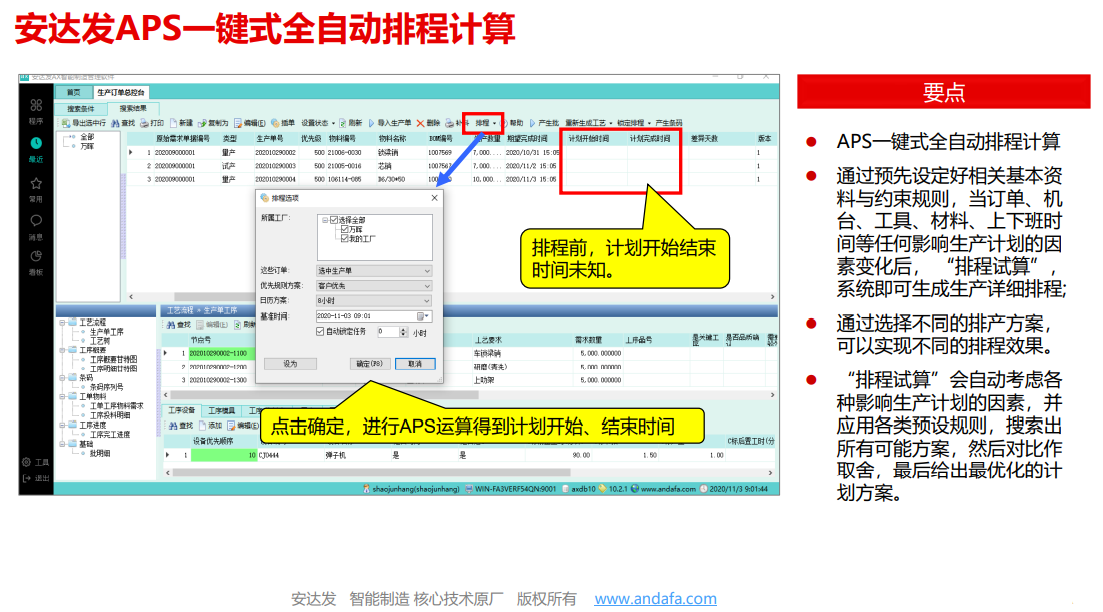

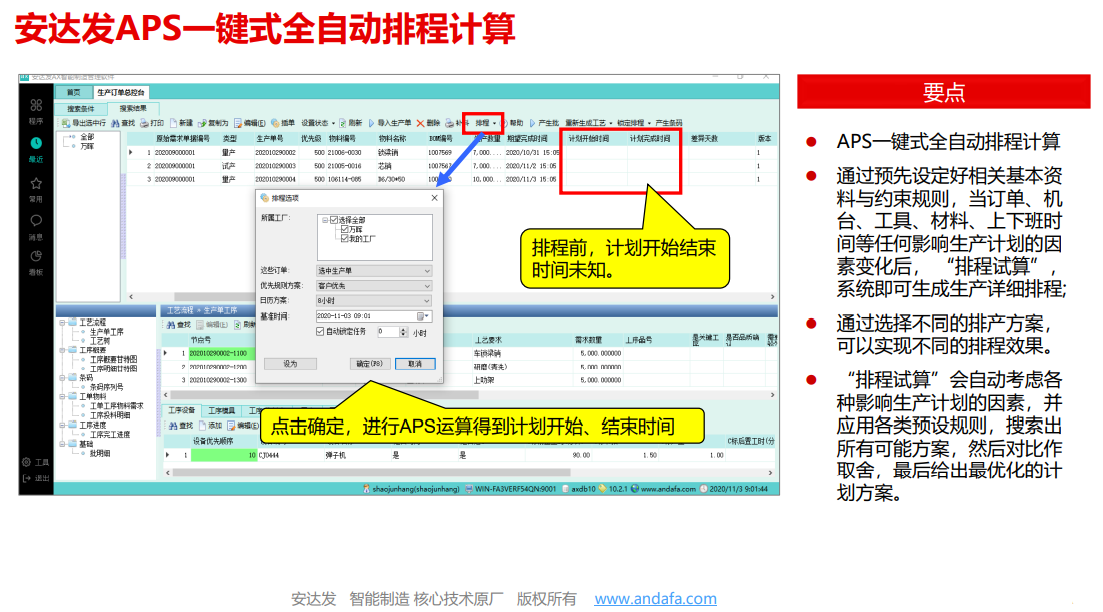

1552 APS排程軟件可以提升企業(yè)生產(chǎn)柔性,增強(qiáng)企業(yè)應(yīng)對市場變化的適應(yīng)性,安達(dá)發(fā)APS排程軟件制定合理優(yōu)化的詳細(xì)生產(chǎn)計(jì)劃,并且還可以將實(shí)績與計(jì)劃結(jié)合,接收MES制造執(zhí)行系統(tǒng)或者其他工序完工反饋信息,從而

2023-02-13 17:28:36 461

461

開始SoC FPGA的學(xué)習(xí)路程還是蠻難的,不僅要熟悉整個(gè)的設(shè)計(jì)流程,而且還要掌握FPGA以及軟件方面的知識,尤其大概看了一下后面的整體設(shè)計(jì)部分,操作起來還是較為繁瑣的,以至于讓人暈頭轉(zhuǎn)向。盡管如此

2023-03-30 10:13:35 6239

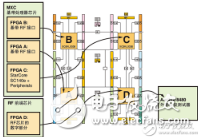

6239 對SoC芯片要進(jìn)行FPGA原型驗(yàn)證,假如設(shè)計(jì)較大,要將SoC中不同功能模塊或者邏輯模塊分別分配到特定的FPGA,那么對SoC的分割策略尤為重要

2023-04-27 15:17:06 627

627

LiteX 框架為創(chuàng)建 FPGA 內(nèi)核/SoC、探索各種數(shù)字設(shè)計(jì)架構(gòu)和創(chuàng)建完整的基于 FPGA 的系統(tǒng)提供了方便高效的基礎(chǔ)架構(gòu)。

2023-06-28 09:08:05 425

425

電子發(fā)燒友App

電子發(fā)燒友App

評論