和?x16 配置中均可提供高達?2133Mbps 的數據傳輸速率,并可與1.5V DDR3實現100%兼容。目前,華邦的?DRAM 產品布局包括1Gb-4Gb DDR3、128Mb-2Gb DDR

2022-04-20 16:04:03 2554

2554

最近我在調試自制6657板子的DDR3初始化,發現一個很奇怪的現象,百思不得其解,我分別用GEL和KEYSTONE DDR3 INIT 在6657EVM開發板上做DDR3初始化,是沒有問題的,我用

2019-01-08 10:19:00

的命令重排和調度使得數據在最大吞吐量時也能有效的傳輸。通過打開和關閉DDR3 SDRAM的行來實現最大效率的使用數據,地址和命令總線。命令的重排順序在命令FIFO中。DDR3內存控制器檢查在命令FIFO中

2018-01-18 22:04:33

請教各位大蝦:

怎樣實現6678和DDR3間的EDMA操作,哪位高手有相關的代碼可以共享哈

還有就是當從DDR3中將數據一維搬至DSP中,處理完后再將DSP中的數據二維放至DDR3中時需要配置哪些寄存器,具體怎樣配置 謝謝!!~

2018-06-21 16:49:06

嗨,我是FPGA領域的新手。現在我正在使用Genesys2。我必須控制DDR3內存。我在Digilent網站上找到了一些使用micrlaze處理器的DDR3示例。但是,在我的情況下,我不必

2019-05-05 15:29:38

為了實現更強大的系統操作,DDR3 SDRAM驅動器設計通過降低電容得到了增強,動態片上端接(ODT)和新的校準方案。電容減少來自于使用新的合并驅動器。使用新驅動程序,組成輸出驅動程序的電路共享用于ODT。DDR2上使用單獨的結構作為輸出驅動器和終端阻抗。

2019-05-23 08:20:56

? ?在調試335x的DDR3時,用的是CCS,非操作系統調試。

? ?按TI給的AM335x——StarterKit.gel,這個文件導入到CCS,debug的時候,DDR3可以驅動,讀寫正常。按

2018-06-21 10:59:20

最近在做DDR3的仿真測試,寫一個自定義的總線轉換成avalon總線,和DDR3的控制器(EMIF)互聯,傳輸數據,但是出現了有readdatavalid信號,而readdata一直是不定態的狀況

2016-05-25 20:20:21

1概述 當今計算機系統DDR3存儲器技術已得到廣泛應用,數據傳輸率一再被提升,現已高達1866Mbps.在這種高速總線條件下,要保證數據傳輸質量的可靠性和滿足并行總線的時序要求,對設計實現提出

2014-12-15 14:17:46

轉載DDR3內存詳解,存儲器結構+時序+初始化過程2017-06-17 16:10:33a_chinese_man閱讀數 23423更多分類專欄:硬件開發基礎轉自:首先,我們先了解一下內存的大體結構工作流程,這樣會比較容量理解這些參數在其...

2021-07-27 07:10:34

通過DDR3內存名MT41J128M16-16Meg*16*8Banks通過命名怎樣算出內存的大小?

2017-06-15 21:19:11

DDR3(double-data-rate three synchronous dynamic random accessmemory)是應用在計算機及電子產品領域的一種高帶寬并行數據總線。DDR3 在 DDR2

2019-05-22 08:36:26

DDR3基礎詳解最近在IMX6平臺下做DDR3的測試接口開發,以前在學習嵌入式時,用的是官方源碼,沒有做過多的研究。此時需要仔細研究DDR3的引腳與時序,此篇是我在學習DDR3做的歸納與總結,其中有

2021-07-28 09:02:52

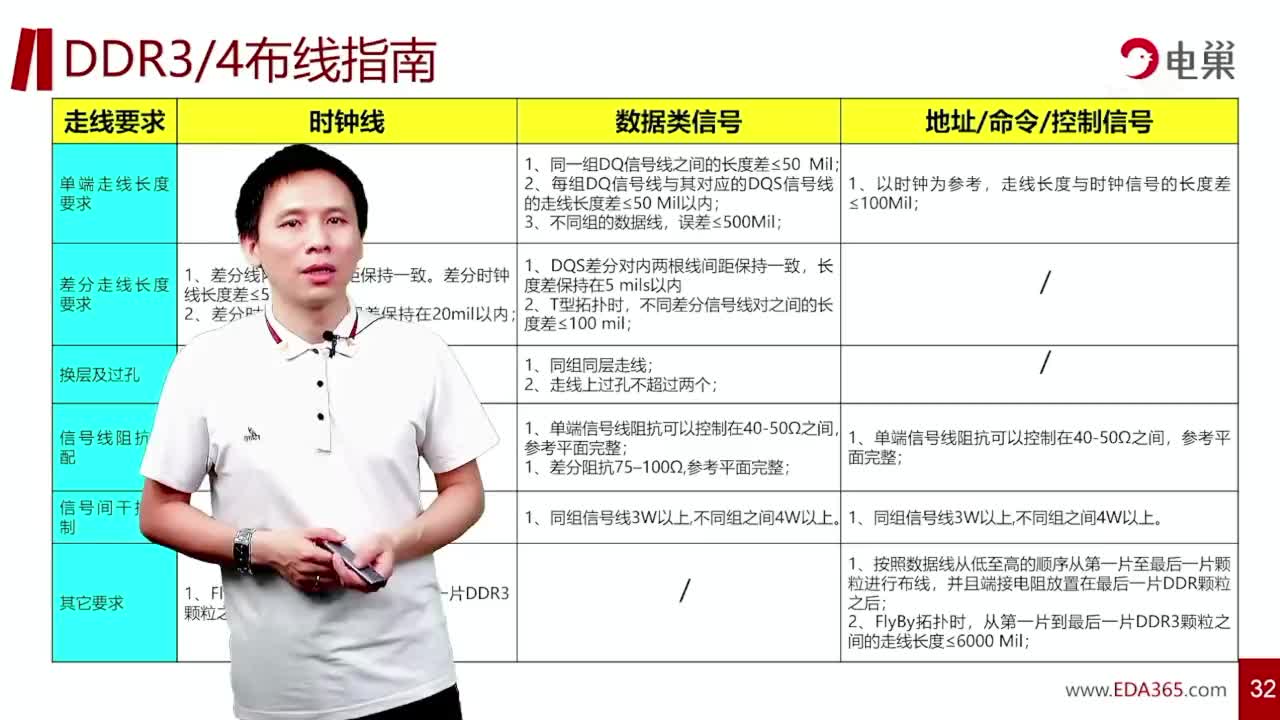

共享交流一下,DDR3布線技巧

2016-01-08 08:17:53

CPU的DDR3總線只連了一片DDR3,也沒有復用總線將DDR3的CS直接拉到地的話,DDR3初始化不成功所以說DDR3的CS信號是通過沿采樣的嗎,電平采樣不行?無法理解啊還是有其他方面原因

2016-11-25 09:41:36

本帖最后由 一只耳朵怪 于 2018-6-21 15:24 編輯

各位好!關于DDR3,之前有小結過如果進行DDR3的SW leveling和進行EMIF4寄存器的配置。但是調試時,如果進行DDR3的問題定位,現小結一下,附上相關文檔。如有相關問題,可在樓下跟帖討論。謝謝!

2018-06-21 04:01:01

專家,你好,想節省代碼設計的周期,請問是否可以提供6670的DDR3的驅動例子?謝謝

2018-06-21 13:34:52

DDR4,DDR3,DDR2,DDR1及SDRAM有什么不同之處?

2021-03-12 06:22:08

你好,ISE版本為13.3,modelsim版本為10.1c 64bit.MIG工具為ddr3生成mcb。modelsim的transcript窗口中的消息如下

2019-07-08 08:44:42

先生/女士 我已經編寫了用于矩陣轉置的vhdl代碼但是我得到結果的問題意味著當我插入輸入,時鐘的值時,它沒有顯示任何東西。為什么它發生我無法理解...這里我我附上我的代碼結果......matrix.docx 11 KB

2020-03-11 09:33:36

矩陣的行列和轉置間的關系和特性是什么?方陣的特征值和特征向量是什么?

2021-06-21 07:44:55

? ? ? BeagleBone的參考設計中,DDR3設計是DDR3 Device without VTT Termination。而其他的AM335X的參考設計都是有VTT Termination

2018-06-21 03:05:42

因為工作的需要,最近做了下DDR3 IP核的讀寫仿真,仿真過程中DDR寫數據正常,但在對DDR讀取數據時出現以下的情況:1.MEM_DQ、MEM_DQS、MEM_DQSN始終為高阻態

2019-12-26 23:11:56

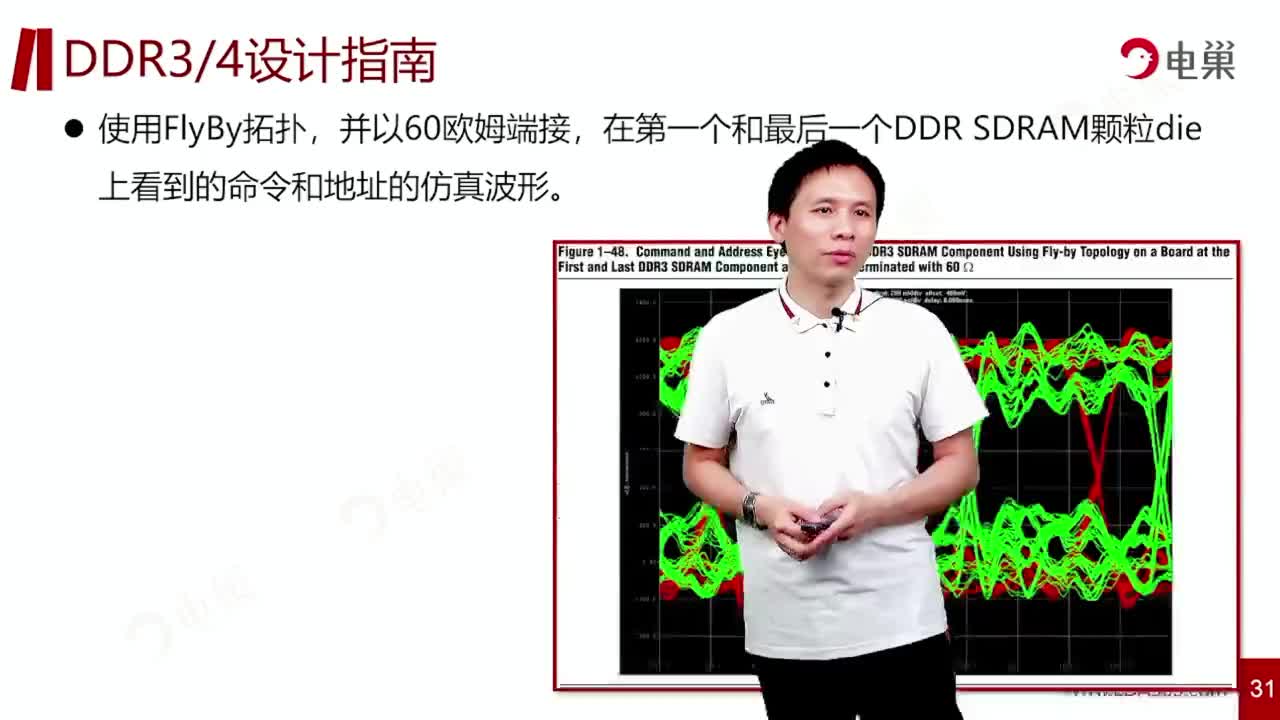

://pan.baidu.com/s/1s402 密碼: 9362 播放密碼:QQ521122524以上為其中一節課程完整版視頻內容:4顆DDR3拓撲講解4顆DDR3布局方法DDR3電氣規則設置等長設置DDR3信號分組等長原理DDR3等長設置DDR3電源處理DDR3布線繞線`

2014-12-17 21:16:37

視頻內容:4顆DDR3拓撲講解4顆DDR3布局方法DDR3電氣規則設置等長設置DDR3信號分組等長原理DDR3等長設置DDR3電源處理DDR3布線繞線

2015-07-30 21:34:09

DDR3 SDRAM內存的總線速率達到600 Mbps to 1.6 Gbps (300 to 800 MHz),1.5V的低功耗工作電壓,采用90nm制程達到2Gbits的高密度。這個架構毫無疑問

2019-04-22 07:00:08

本次發布 Gowin DDR3參考設計。Gowin DDR3 參考設計可在高云官網下載,參考設計可用于仿真,實例化加插用戶設計后的總綜合,總布局布線。

2022-10-08 08:00:34

Achieving High Performance DDR3 Data Rates in Virtex-7 and Kintex-7 FPGAs。Xilinx官方DDR3資料。

2016-05-27 16:39:58

DDR3的IP核配置完畢后,產生了好多文件,請問如何調用這些文件實現DDR3的讀寫呢?看了一些文章,說是要等到local_init_done為高電平后,才能進行讀寫操作。請問DDR3的控制命令如

2016-01-14 18:15:19

借助于.NET類,labview實現了PDF轉WORD的功能,這個功能還挺有用的。歡迎下載使用

2021-11-19 15:25:55

他vc707上運行我們的測試SW,那將是很棒的。這肯定有助于追查問題。該應用程序擴展了hello world示例,緩沖區放置在DDR3中。 heloworld.c和lscript.ld是附加的。提前致謝lscript.ld 5 KBhelloworld.c 3 KB

2019-09-09 10:20:26

看完保證你會做DDR3的仿真

2015-09-18 14:33:11

StringSrc變量和StringDst變量放在DDR2中固定位置。1)在cmd中給變量安排地址2)給變量賦初值以及分配地址空間3、為了實現矩陣的轉置,用AB類傳輸,關鍵在與對PaRam參數的設置,其他的按鍵觸發

2015-10-16 09:45:34

DDR3的頻率就是外頻的8倍 133=1066DDR2和DDR3的區別內存相對于DDR2內存,其實只是規格上的提高,并沒有真正的全面換代的新架構。DDR3接觸針腳數目同。DDR2皆為240pin。但是

2014-12-30 14:35:58

1.5V。所以我必須使用bank 15而不是bank 14來實現DDR3內存接口。這意味著現在我要使用12,13和12號銀行。 15用于DDR3內存接口。可以使用這3個銀行進行DDR3內存接口嗎?使用不相鄰的銀行是一個問題嗎?請幫幫我。問候,Iroshana。

2020-04-17 07:54:29

第22章 DSP矩陣運算-放縮,乘法和轉置矩陣本期教程主要講解矩陣運算中的放縮,乘法和轉置。目錄第22章 DSP矩陣運算-放縮,乘法和轉置矩陣22.1 初學者重要提示22.2 DSP基礎運算指令

2021-08-11 08:41:19

,也無法安裝DDR3的內存。ICMAX DDR型號總的來說,DDR4和DDR3相比,在各個方面都有著明顯的提升,出色的功耗和更加強勁穩定的性能給多任務處理和運行大型游戲提供了堅實的硬件基礎,在PC領域大多

2019-07-25 14:08:13

并不會注意一些數字上的差異,如DDR3和DDr2,或許大多數人都會追求時髦選擇DDR3,但是你真的了解DDR2與DDR3的區別嗎?作為消費者,其實我們可主宰自己的命運,用知識的武器捍衛自己的選擇。下面

2011-12-13 11:29:47

自己畫的6657的板,發現DDR3初始化有問題,初始化參數是按照芯片手冊來設置的,寫數據進去會出錯。初步懷疑是DDR3布線問題,請問TI的大神們,6657對DDR3的布線有什么具體的要求嗎?或者是

2018-06-21 05:42:03

了設計的一大挑戰。FPGA可通過在單個FPGA中實現多個視頻處理器來提供強大的處理能力。那么現在的挑戰就變成了要使數據盡快且高效地從FPGA進出。DDR3存儲器系統在大多數情況下可以為這些基于FPGA的系統

2019-05-27 05:00:02

進行了DDR3 SDRAM控制器的編寫,分析并提出了提高帶寬利用率的方法。最終將其進行類FIFO接口的封裝,屏蔽掉了DDR3 IP核復雜的用戶接口,為DDR3數據流緩存的實現提供便利。系統測試表明,該

2018-08-02 09:34:58

作者:張鳳麒,張延彬,王忠勇;2018年電子技術應用第7期摘要: 為了解決期貨行情數據加速處理中多個通道同時訪問DDR3時出現的數據讀寫沖突問題,實現了一種基于FPGA的DDR3六通道讀寫防沖突

2018-08-02 09:32:45

作者:吳連慧,周建江,夏偉杰摘要:為了解決視頻圖形顯示系統中多個端口訪問DDR3的數據存儲沖突,設計并實現了基于FPGA的DDR3存儲管理系統。DDR3存儲器控制模塊使用MIG生成DDR3控制器

2018-08-02 11:23:24

Xilinx Virtex-6系列FPGA中使用MIG3.7 IP核實現高速率DDR3芯片控制的設計思想和設計方案。針對高速實時數字信號處理中大容量采樣數據通過DDR3存儲和讀取的應用背景,設計和實現了

2018-08-30 09:59:01

大量收購現代DDR3長期回收現代ddr3,高價收購現代DDR3.大量求購現代DDR3.深圳帝歐專業電子回收,帝歐趙生***QQ1816233102/879821252郵箱dealic@163.com

2021-10-13 19:12:25

大量收購現代DDR3長期回收現代ddr3,高價收購現代DDR3.大量求購現代DDR3.深圳帝歐專業電子回收,帝歐趙生***QQ1816233102/879821252郵箱dealic@163.com

2021-10-13 19:18:05

如何借助于 MicroPython,實現你的 IoT 構想?

2021-04-02 07:15:08

均衡的定義和重要性是什么如何實現FPGA和DDR3 SDRAM DIMM條的接口設計?

2021-05-07 06:21:53

DDR3存儲器控制器面臨的挑戰有哪些?如何用一個特定的FPGA系列LatticeECP3實現DDR3存儲器控制器。

2021-04-30 07:26:55

現在因為項目需要,要用DDR3來實現一個4入4出的vedio frame buffer。因為片子使用的是lattice的,參考設計什么的非常少。需要自己調用DDR3控制器來實現這個vedio

2015-08-27 14:47:57

大家好,我在DDR3規格中發現JEDEC79-3E定義VOH(DC)是DC輸出高測量級別(用于IV曲線線性)。但是沒有關于如何測量高輸出直流輸出的指南,特別是當信號在高電壓時有環時,請參見附圖。誰能

2019-04-17 13:59:13

的工作時鐘頻率。然而,設計至DDR3的接口也變得更具挑戰性。在FPGA中實現高速、高效率的DDR3控制器是一項艱巨的任務。直到最近,只有少數高端(昂貴)的FPGA有支持與高速的DDR3存儲器可靠接口的塊

2019-08-09 07:42:01

自建Spartan6 DDR3仿真平臺

2019-08-01 06:08:47

怎樣對DDR3芯片進行讀寫控制呢?如何對DDR3芯片進行調試?

2021-08-12 06:26:33

在DDR3 Datesheet 中經常提到 AC175,AC150,DC100,DC90指的是什么意思???

2012-07-30 20:59:49

本帖最后由 sugarr 于 2012-3-7 10:14 編輯

求助,實現一下矩陣的轉置函數function r=rafun(y,M,N)y=reshape(y,M,N);f=@(x

2012-03-07 10:10:04

第22章 DSP矩陣運算-放縮,乘法和轉置矩陣本期教程主要講解矩陣運算中的放縮,乘法和轉置。目錄第22章 DSP矩陣運算-放縮,乘法和轉置矩陣22.1 初學者重要提示22.2 DSP基礎運算指令

2021-08-11 06:05:03

本帖最后由 一只耳朵怪 于 2018-6-20 11:34 編輯

各位專家好!剛剛學習DSP,還沒有入門。實驗室購買了TMS320C6678開發板。請問:1、為什么DSP需要外接DDR3?2

2018-06-20 00:40:57

背景:由于使用的是自己做的6678的板子,因此DDR3布線與EVM略有出入,DDR3無法運行在1333速率,只能運行在1066速率。現在想要在板子上實現Nor flash boot,因此嘗試

2018-08-06 07:33:54

我需要在V7中實現與DDR3 SDRAM相同的功能和接口。這意味著命令/地址,讀取數據和寫入數據流的方向與MIG的方向不同。這可以實現嗎?

2020-07-14 16:18:04

Quamtum-SI DDR3仿真解析

Automated DDR3 Analysis

2010-04-29 09:00:11 4257

4257

總結了DDR和DDR2,DDR3三者的區別,對于初學者有很大的幫助

2015-11-10 17:05:37 36

36 DDR3是目前DDR的主流產品,DDR3的讀寫分離作為DDR最基本也是最常用的部分,本文主要闡述DDR3讀寫分離的方法。最開始的DDR, 芯片采用的是TSOP封裝,管腳露在芯片兩側的,測試起來相當方便;但是,DDRII和III就不一樣了,

2017-11-06 13:44:10 8454

8454

雖然新一代電腦/智能手機用上了DDR4內存,但以往的產品大多還是用的DDR3內存,因此DDR3依舊是主流,DDR4今后將逐漸取代DDR3,成為新的主流,下面我們再來看看DDR4和DDR3內存都有哪些區別。相比上一代DDR3,新一代DDR4內存主要有以下幾項核心改變:

2017-11-08 15:42:23 30896

30896 為了解決視頻圖形顯示系統中多個端口訪問DDR3的數據存儲沖突,設計并實現了基于FPGA的DDR3存儲管理系統。DDR3存儲器控制模塊使用MIG生成DDR3控制器,只需通過用戶接口信號就能完成DDR3

2017-11-18 18:51:25 6412

6412

我們通過Configuration,Package,Speed...等DDR3的命名可知道DDR3的容量,封裝,速度等級等信息。

2019-03-03 11:04:15 1909

1909

本文檔的主要內容詳細介紹的是DDR和DDR2與DDR3的設計資料總結包括了:一、DDR的布線分析與設計,二、DDR電路的信號完整性,三、DDR Layout Guide,四、DDR設計建議,六、DDR design checklist,七、DDR信號完整性

2020-05-29 08:00:00 0

0 從成本的角度來看,DDR3也許的確要比DDR4低一些,所以從這個角度可以講通。

2020-09-08 16:28:23 4062

4062 DDR4相比DDR3的相關變更點相比DDR3,DDR4存在諸多變更點,其中與硬件設計直接相關的變更點主要有:? 增加Vpp電源;? VREFDQ刪除;? CMD、ADD、CTRL命令的端接變更為

2021-11-06 20:36:00 28

28 ??這篇文章我們講一下Virtex7上DDR3的測試例程,Vivado也提供了一個DDR的example,但卻是純Verilog代碼,比較復雜,這里我們把DDR3的MIG的IP Core掛在Microblaze下,用很簡單的程序就可以進行DDR3的測試。

2022-08-16 10:28:58 1241

1241 一、DDR3簡介 ? ? ? ? DDR3全稱double-data-rate 3 synchronous dynamic RAM,即第三代雙倍速率同步動態隨機存儲器。所謂同步,是指DDR3數據

2022-12-21 18:30:05 1915

1915 本文介紹一個FPGA開源項目:DDR3讀寫。該工程基于MIG控制器IP核對FPGA DDR3實現讀寫操作。

2023-09-01 16:23:19 745

745

DDR3是2007年推出的,預計2022年DDR3的市場份額將降至8%或以下。但原理都是一樣的,DDR3的讀寫分離作為DDR最基本也是最常用的部分,本文主要闡述DDR3讀寫分離的方法。

2023-10-18 16:03:56 518

518

DDR4和DDR3內存都有哪些區別? 隨著計算機的日益發展,內存也越來越重要。DDR3和DDR4是兩種用于計算機內存的標準。隨著DDR4內存的逐漸普及,更多的人開始對兩者有了更多的關注。 DDR3

2023-10-30 09:22:00 3905

3905

正在加载...

2554

2554 2554

2554

電子發燒友App

電子發燒友App

評論