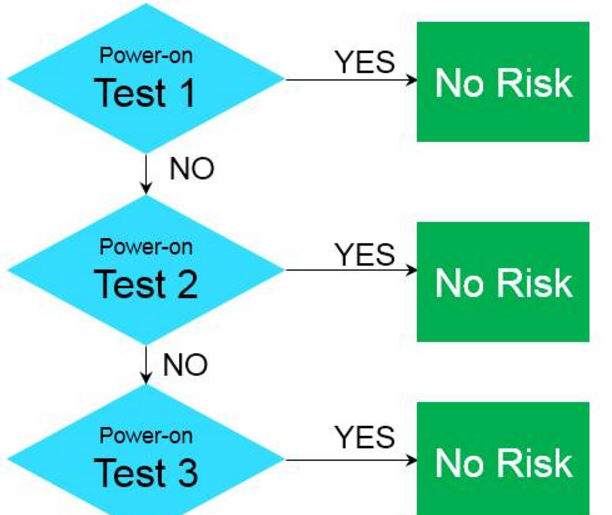

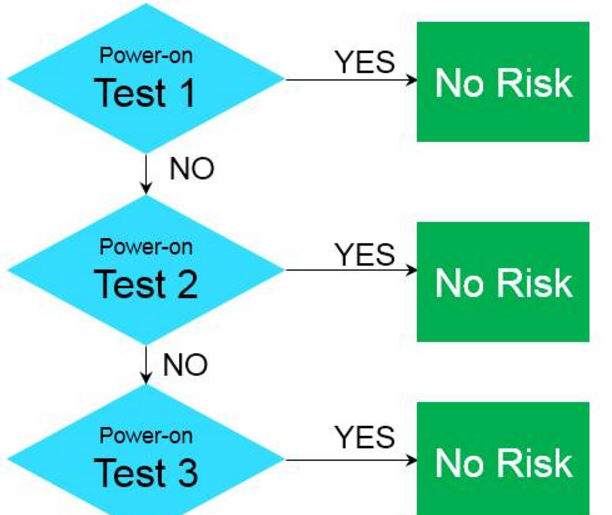

Zynq-7000 AP SoC 設計應該針對給 PS eFUSE 完整性造成的潛在影響進行評估。請參見以下部分,了解評估潛在影響的方法

2017-10-11 14:24:55 10662

10662

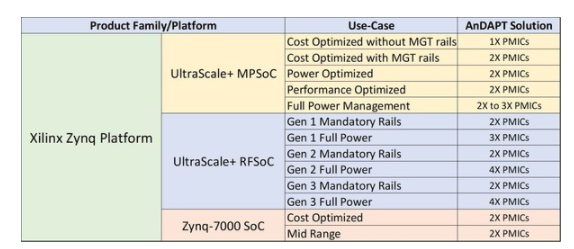

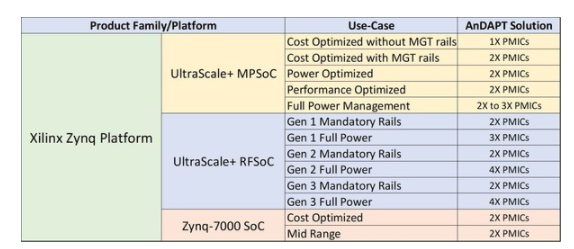

AnDAPT支持為Xilinx Zynq所有的UltraScale+和Zynq-7000 FPGA/SoC供電,包括采用集成、靈活和高效AmP電源管理IC的應用定義用例。

2021-05-18 09:48:08 991

991

請教一下,我在HLS里面要將以下程序生成IP核,C Synthesis已經(jīng)做好了,但是在export RTL的時候一直在運行

int sum_single(int A int B

2023-09-28 06:03:53

大家好,我們是一群學生在Zynq 7000 AP SoC上做項目。我們已經(jīng)提供了一個基本代碼,OV7670攝像頭可以捕獲實時視頻并將其發(fā)送到電路板。電路板直接在VGA屏幕上顯示視頻。內存緩沖區(qū)已用

2020-04-10 09:51:09

) 的英國學者所著,為您詳細介紹 Xilinx? Zynq?-7000 All Programmable SoC。本書包含了 Zynq-7000 SoC 開發(fā)的方方面面,從硬件到軟件,從理論到實現(xiàn)

2014-09-04 11:37:18

我正在尋找Zynq-7000 AP SoC CLG400 XC7Z010的有效模量,CTE和Tg。使用您的包裝進行SIP的熱機械建模需要此數(shù)據(jù)。我還想知道最大允許結溫是多少。

2020-07-30 08:16:38

真隨機數(shù)發(fā)生器在安全解決方案中起著重要作用。真正的隨機數(shù)發(fā)生器通常由平臺支持,例如Exynos 5,OMAP 3,4 SoC系列和飛思卡爾i.MX53。我已經(jīng)閱讀了zynq-7000的TRM,但沒有找到隨機數(shù)生成器。 zynq真的不支持RNG嗎?

2020-07-17 14:27:09

ArduZynq 和 TE0726-03M ZynqBerry SBC 中的 Zynq Z-7010 SoC 的 FPGA 容量存在顯著差異。雖然所有 Zynq-7000 SoC 都采用雙核 Arm

2018-08-31 14:43:05

嗨,大家好,我有一個問題,在VIVADO HLS 2017.1中運行C \ RTL協(xié)同仿真。我已成功運行2014和2016版本的代碼。任何人都可以告訴我為什么報告NA僅用于間隔

2020-05-22 15:59:30

Zynq-7000 AP SoC ZC706 XC7Z045 Zynq?-7000 FPGA + MCU/MPU SoC 評估板

2024-03-14 20:42:29

在尋求獲得來自處理系統(tǒng)內的賽靈思Zynq?-7000全可編程SoC的最大利益,操作系統(tǒng)將讓你更不是一個簡單的裸機解決方案。任何開發(fā)ZYNQ SoC設計有大量的操作系統(tǒng)可供選擇,并根據(jù)最終應用程序,你

2019-10-23 07:44:24

Vivado HLS視頻庫加速Zynq-7000 All Programmable SoC OpenCV應用加入賽靈思免費在線研討會,了解如何在Zynq?-7000 All Programmable

2013-12-30 16:09:34

ZYNQ-7000 ALL PROGRAMMABLE SOC P

2023-03-30 11:54:50

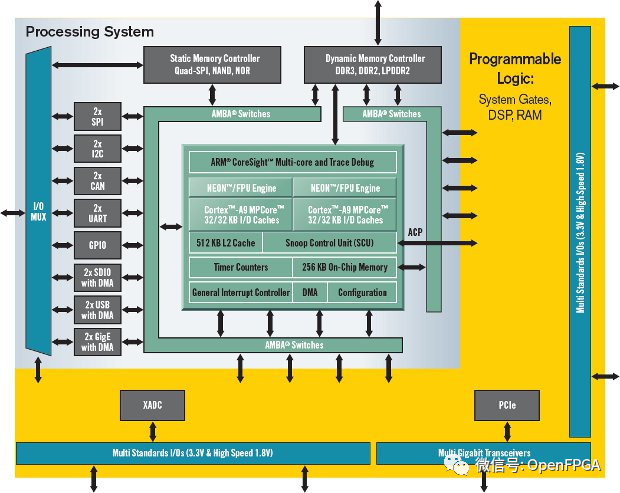

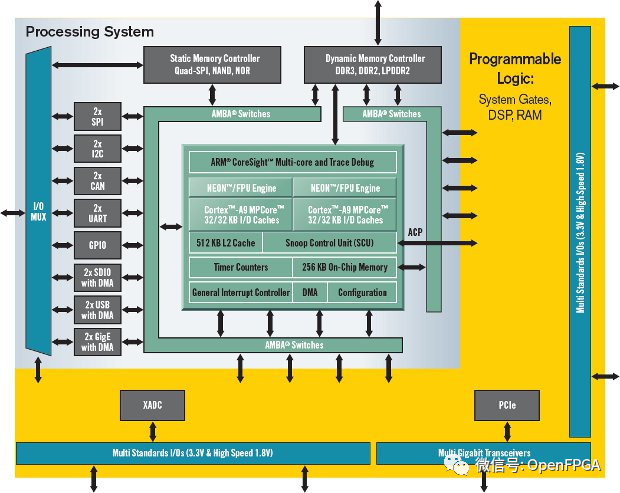

CPUCPU為Xilinx Zynq-7000SOC,兼容XC7Z035/XC7Z045/XC7Z100,平臺升級能力強,以下為Xilinx Zynq-7000特性參數(shù):TLZ7xH-EasyEVM

2022-01-03 07:50:21

你好,我如何啟用自定義IP的中斷。我使用vivado HLS生成了IP。中斷線連接到ZYNQ的中斷端口。以下是設備樹{amba_pl:amba_pl {#address-cells

2020-05-01 16:46:48

就是加速開發(fā)的周期。加速策略可以從兩個方面考慮:(一)設計的重用和(二)抽象層次的提升。Xilinx Vivado開發(fā)套件中的IP集成功能可以實現(xiàn)設計的重用,而Vivado HLS工具則能夠實現(xiàn)對高層次

2020-10-10 16:48:25

Vivado HLS中可以使用三種語言進行設計開發(fā),分別是 C、C++ 和 SystemC。其中C語言是一種非常通用的面向過程的編程語言,我們在《正點原子ZYNQ嵌入式開發(fā)指南》中均是使用C語言進行

2020-10-10 16:44:42

對設計出來的IP核進行驗證。7.3HLS設計我們在電腦中的“F:\ZYNQ\High_Level_Synthesis”目錄下新建一個名為ov5640_sobel的文件夾,作為本次實驗的工程目錄。然后打開

2020-10-13 17:05:04

的IP核。在本章我們通過按鍵控制LED實驗,來學習如何使用Vivado HLS工具生成一個帶有輸入和輸出接口的IP核,并學習Vivado HLS工具仿真平臺的使用,以及在Vivado中對綜合結果進行驗證

2020-10-10 16:54:25

對設計出來的IP核進行驗證。5.3HLS設計我們在電腦中的“F:\ZYNQ\High_Level_Synthesis”目錄下新建一個名為lcd_rgb_colorbar的文件夾,作為本次實驗的工程目錄。然后

2020-10-13 16:56:47

、HLS IP庫6、HLS線性代數(shù)庫其中第一個“任意精度數(shù)據(jù)類型庫”在《正點原子HLS開發(fā)指南》的第一章《LED閃爍實驗》中就已經(jīng)用到過。本章將帶大家學習如何使用HLS視頻庫中的函數(shù)來作圖像處理。需要

2020-10-13 16:58:56

的IP核,并在Vivado中對設計出來的IP核進行驗證。11.3HLS設計我們在電腦中的“F:\ZYNQ\High_Level_Synthesis”目錄下新建一個名為otsu_threshold的文件夾

2020-10-14 16:04:34

RTL。 在導出RTL結束之后,我們到工程目錄所指向的文件夾中可以看到以ZIP壓縮文件形式存在的IP核,如下圖所示:圖 13.3.18 文件夾中的IP核HLS設計結束之后,我們將在Vivado中對導出

2020-10-16 16:22:38

的IP核,該IP核能夠實現(xiàn)基于霍夫變換的直線檢測。12.3HLS設計我們在電腦中的“F:\ZYNQ\High_Level_Synthesis”目錄下新建一個名為hough_transform_line

2020-10-14 16:06:47

,直方圖均衡化使得原始圖像的直方圖趨向于在整個灰度級中均勻分布,反映在圖像上面就是圖像的對比度得到了很大的提升。10.2實驗任務本節(jié)的實驗任務是使用Vivado HLS實現(xiàn)一個圖像處理的IP核,該IP

2020-10-14 16:02:01

ap_none接口的IP核。在本章我們將通過呼吸燈實驗,來學習如何使用Vivado HLS工具生成一個帶有AXI4-Lite總線接口的IP核,并學習Vivado HLS工具C/RTL協(xié)同仿真平臺的使用,以及在

2020-10-10 17:01:29

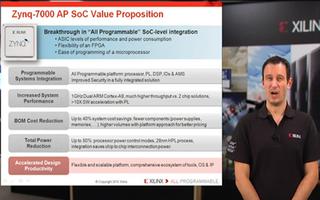

我想知道為什么人們使用Zynq-SoC而不是其他類型的FPGA?使用這個芯片有什么區(qū)別和好處?在普通微處理器上我更喜歡Zynq Soc的限制在哪里?親切的問候,德勒H.

2020-04-01 09:24:02

,我們一直在使用Vivado給我們提供的IP或者使用硬件描述語言制作 IP 。今天我們將講解如何使用HLS-高級綜合語言來創(chuàng)建屬于我們自己的IP。我們將使用的工具稱為Vitis HLS,此后稱為 HLS

2022-09-09 16:45:27

` ZYNQ系列是Xilinx推出的高端嵌入式SoC,其在片上集成了ARM處理器和FPGA。ZYNQ與傳統(tǒng)的嵌入式CPU相比,具有強大的并行處理能力。開發(fā)人員利用FPGA強大的并行處理能力,不僅

2021-01-15 17:09:15

Alexa)和揚聲器接口以啟用音頻通道。要完成此項目,我們將使用Vivado,SDK和Vivado HLS。我們使用的開放板是基于采用Zynq 7010 SoC芯片的Snickerdoodle開發(fā)板

2019-07-31 05:30:00

的IP與Zynq Processing System連接起來。現(xiàn)在,為了將數(shù)據(jù)發(fā)送到corfe并收回,Vivado hls將輸入端口合成為ap_memory(這意味著為輸入端口pBaseMatrix

2019-02-28 13:47:30

模擬過程完成沒有0錯誤,但在合成期間顯示錯誤。我無法找到錯誤。我在合成期間在HLS工具中收到這樣的錯誤“在E中包含的文件:/thaus / fact_L / facoriall

2020-05-21 13:58:09

FPGA的HLS案例開發(fā)|基于Kintex-7、Zynq-7045_7100開發(fā)板前 言本文主要介紹HLS案例的使用說明,適用開發(fā)環(huán)境:Windows 7/10 64bit、Xilinx

2021-02-19 18:36:48

你好,我使用Vivado HLS生成了一個IP。從HLS測量的執(zhí)行和測量的執(zhí)行時間實際上顯著不同。由HLS計算的執(zhí)行非常小(0.14 ms),但是當我使用AXI計時器在真實場景中測量它時,顯示3.20 ms。為什么會有這么多差異? HLS沒有告訴實際執(zhí)行時間?等待回復。問候

2020-05-05 08:01:29

Vivado HLS 2017.4 、Xilinx SDK 2017.4。

測試板卡是基于創(chuàng)龍科技Xilinx Zynq-7000系列XC7Z010/XC7Z020高性能低功耗處理器設計的異構多核SoC

2023-08-24 14:44:10

Vivado HLS 2017.4 、Xilinx SDK 2017.4。測試板卡是基于創(chuàng)龍科技Xilinx Zynq-7000系列XC7Z010/XC7Z020高性能低功耗處理器設計的異構多核SoC工業(yè)

2023-01-01 23:51:35

是基于創(chuàng)龍科技Xilinx Zynq-7000系列XC7Z010/XC7Z020高性能低功耗處理器設計的異構多核SoC工業(yè)級核心板。HLS 案例位于產品資料“4-軟件資料\Demo

2023-08-24 14:40:42

龍科技Xilinx Zynq-7000系列XC7Z010/XC7Z020高性能低功耗處理器設計的異構多核SoC工業(yè)級核心板。HLS 案例位于產品資料“4-軟件資料\Demo\FPGA-HLS

2023-01-01 23:52:54

使用 solution2 生成 IP 核。進行綜合時,需將頂層函數(shù)修改為 HLS_accel() 。修改頂層函數(shù)后請點擊

,在彈出的界面中點擊“All Solutions”進行綜合。圖 53 圖 54綜合完成后

2023-08-24 14:52:17

目 錄4 matrix_demo 案例 274.1 HLS 工程說明 274.2 編譯與仿真 304.3 綜合 314.4 IP 核測試 364.4.1 PL 端 IP 核測試 Vivado 工程

2023-01-01 23:50:04

產品上市時間。

HLS 基本開發(fā)流程如下:(1) HLS 工程新建/工程導入(2) 編譯與仿真(3) 綜合(4) IP 核封裝(5) IP 核測試測試板卡是基于創(chuàng)龍科技Xilinx Zynq

2023-08-24 14:54:01

產品上市時間。HLS 基本開發(fā)流程如下:(1) HLS 工程新建/工程導入(2) 編譯與仿真(3) 綜合(4) IP 核封裝(5) IP 核測試測試板卡是基于創(chuàng)龍科技Xilinx Zynq-7000系列

2023-01-01 23:46:20

、USB、Micro SD、CAN、UART等接口,支持LCD顯示拓展及Qt圖形界面開發(fā),方便快速進行產品方案評估與技術預研。HLS基本開發(fā)流程如下:HLS工程新建/工程導入編譯與仿真綜合IP核封裝IP核

2021-11-11 09:38:32

的經(jīng)驗幾乎為0,因此我想就如何解決這個問題提出建議。這就是我的想法:1 - 首先,用Vivado HLS轉換VHDL中的C代碼(我現(xiàn)在有一些經(jīng)驗)2 - 在Vivado HLS中生成IP核(如果我

2020-03-24 08:37:03

你好我正在嘗試在vivado HLS中創(chuàng)建一個IP,然后在vivado中使用它每次我運行Export RTL我收到了這個警告警告:[Common 17-204]您的XILINX環(huán)境變量未定義。您將

2020-04-03 08:48:23

我照著xapp1167文檔,用HLS實現(xiàn)fast_corners的opencv算法,并生成IP。然后想把這個算法塞到第三季的CH05_AXI_DMA_OV5640_HDMI上,這個demo里

2017-01-16 09:22:25

`玩轉Zynq連載1——Zynq的linux啟動過程更多資料共享 鏈接:https://share.weiyun.com/5s6bA0s1概述 簡單的,以ug585中的一張圖來看,從大的方面說

2019-04-16 06:56:32

`玩轉Zynq連載21——Vivado中IP核的移植更多資料共享騰訊微云鏈接:https://share.weiyun.com/5s6bA0s百度網(wǎng)盤鏈接:https://pan.baidu.com

2019-09-04 10:06:45

靈活性也就越小。在Xilinx的FPGA器件中,IP核設計是非常重要并且必不可少的一部分,應該說,前述的軟IP、固IP和硬IP,在我們Zstar板載的Zynq上都能夠找到蹤影。而對于Vivado來說

2019-09-06 08:13:18

`玩轉Zynq連載24——用戶自定義IP核的移植更多資料共享騰訊微云鏈接:https://share.weiyun.com/5s6bA0s百度網(wǎng)盤鏈接:https://pan.baidu.com/s

2019-09-15 09:55:57

`玩轉Zynq連載25——[ex04] 基于Zynq PL的自定義IP核集成更多資料共享騰訊微云鏈接:https://share.weiyun.com/5s6bA0s百度網(wǎng)盤鏈接:https

2019-09-20 11:35:29

。 3 ZYNQ硬件配置在IP Integrator(IP集成器)下點擊CreateBlock Design(創(chuàng)建新的設計模塊)。如圖所示,在彈出的Create BlockDesign窗口

2019-09-30 12:57:32

的基于Zynq SoC的視覺系統(tǒng)。加速算法C到IP集成ZYNQ SOC:嵌入式視覺的最明智的選擇 在開發(fā)機器視覺應用過程中,設計團隊必須選擇高度靈活的器件,這一點至關重要。設計團隊所需的計算平臺應提供強大

2014-04-21 15:49:33

。HLS工程說明時鐘HLS工程配置的時鐘為100MHz,案例將該時鐘用于計算0.5s間隔時間進行LED2亮滅狀態(tài)控制,生成的IP核亦需接入該時鐘。如需修改時鐘頻率,請打開HLS工程后點擊,在彈出的界面中

2021-11-11 15:54:48

描述TIDA-00389 設計是一種經(jīng)過優(yōu)化的電源解決方案,適用于 Xilinx? Zynq? 7010 FPGA/SoC(屬于 Zynq? 7000 產品系列)。它面向 ADAS 應用,在這

2018-11-19 15:00:01

介紹如何設計HLS IP,并且在IP Integrator中使用它來作一個設計——這里生成兩個HLS blocks的IP,并且在一個FFT(Xilinx IP)的設計中使用他們,最終使用RTL

2017-02-07 17:59:29 4179

4179

高層次綜合設計最常見的的使用就是為CPU創(chuàng)建一個加速器,將在CPU中執(zhí)行的代碼移動到FPGA可編程邏輯去提高性能。本文展示了如何在Zynq AP SoC設計中使用HLS IP。 在Zynq器件

2017-02-07 18:08:11 3207

3207

閑話Zynq UltraScale+ MPSoC 作者: Hello,Panda 時隔三年,Xilinx推出了其全新的異構SoC,大名叫Zynq UltraScale+。相比它的前輩

2017-02-08 08:24:11 588

588

最新和最具創(chuàng)新性的汽車、醫(yī)療和安全視覺產品的核心,以及應用于先進的電機控制系統(tǒng),使工廠生產過程更加的安全,更加的環(huán)保,更加的高效。Zynq SoC也已經(jīng)擁有了與下一代有線和無線通信基礎設施以及新興的豐富的物聯(lián)網(wǎng)應用融合連接的接口。公司通過利用Zynq SoC和硬件/軟件的復用部署實現(xiàn)一種平臺戰(zhàn)略,它們能夠

2017-02-08 15:45:00 257

257

Xilinx? 的客戶們分享了各種 ?Zynq SoC? 的成功應用。這些成功案例詳細描述了挑戰(zhàn)、解決方案和所取得的成果。如欲了解其他 ?Xilinx? 客戶如何利用 ?Zynq SoC

2017-02-09 03:35:13 217

217 ? 創(chuàng)建 ?Linux? 系統(tǒng)的整個過程,而且還將將介紹在 ?IPI? 中為 Zynq SoC? 創(chuàng)建硬件系統(tǒng)的過程。隨后使用 ?Avnet? 的 ?SoC Mini-ITX? 電路板,不僅可將現(xiàn)成

2017-02-09 08:03:40 807

807 Missing Link Electronics? 基于德國弗朗霍夫海因里希赫茲研究所 ?(HHI)? 的加速技術提供 2015.02a? 修訂版 ?Zynq SoC? 評估參考設計。支持

2017-02-09 08:17:06 212

212 到目前為止我們摸索使用過的Zynq All Programmable SoC PS(處理器系統(tǒng))部分的所有設備都是只利用了一個ARM Cortex-A9處理器內核(內核0),然而在Zynq SoC

2017-02-11 10:06:11 2262

2262

太過緩慢,可利用Vivado?設計套件高層次綜合(HLS)工具將代碼轉換為Verilog或VHDL格式,以便在Zynq SoC可編程邏輯中運行。這樣可以將一些功能代碼的運行速度提高700倍,同時釋放處理器以更快地執(zhí)行其他任務,從而提升整體系統(tǒng)性能。

2017-11-18 13:24:05 1599

1599

將Vivado HLS與OpenCV庫配合使用,既能實現(xiàn)快速原型設計,又能加快基于Zynq All Programmable SoC的Smarter Vision系統(tǒng)的開發(fā)進度。

2018-07-18 09:49:00 3602

3602

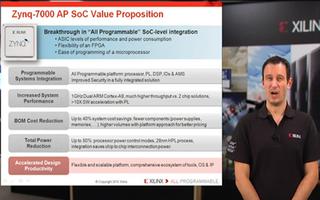

Zynq-7000 AP SoC作為業(yè)界第一款SoC產品,完美集成了雙核ARM Cortex-A9處理器與賽靈思28 nm FPGA。本視頻向您展示了Zynq-7000的強大性能,以及豐富的外設支持及開發(fā)工具支持情況,讓您能更快地尋找到Zynq-7000的相關信息和支持資源。

2018-06-05 01:45:00 4172

4172

Xilinx公司1G Hz的Zynq 7045 AP SoC能給我們帶來什么?

2018-06-04 13:47:00 5090

5090

Xilinx公司介紹:Zynq-7000 AP SoC 在多種應用領域中的演示。

2018-06-04 13:47:00 4466

4466 除了要最終客戶推出屢獲殊榮的Zynq-7000 AP SoC器件幫助他們在競爭中整整領先一代之外,我們今天還推出了豐富的穩(wěn)健可靠的基礎架構,使Zynq-7000 SoC用戶能夠生產力更高

2018-06-04 13:47:00 3212

3212

)。這里還要強調軟件要求避免緩存一致性問題。 在Zynq CPU和HLS加速模塊之間Streaming Data Step 1: 產生HLS IP 這里會產生兩個

2018-10-02 07:25:11 394

394 OPENCV(Open Source Computer Vision)被廣泛的使用在計算機視覺開發(fā)上。使用Vivado HLS視頻庫在zynq-7000全可編程soc上加速OPENCV 應用的開發(fā),將大大提升我們的計算機視覺開發(fā)。

2018-11-10 10:47:49 1323

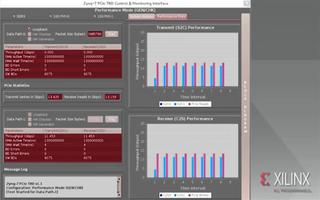

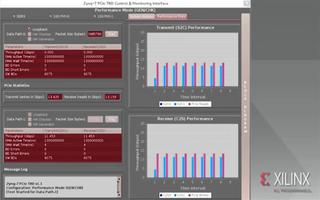

1323 觀看Zynq-7000 AP SoC ZC706評估套件,這是一款基于收發(fā)器的套件,包含所有必需的硬件,工具和IP,可快速完成對基于收發(fā)器的嵌入式系統(tǒng)的評估和開發(fā)。

董事會給出了

2018-11-20 06:03:00 5402

5402 Xilinx為Zynq-7000 SoC提供了一個穩(wěn)健而廣泛的支持基礎,讓用戶基于Zynq的開發(fā)設計更加高效,同時也幫助客戶更快地把設計推向市場.Zynq-7000 SoC的用戶對Vivado

2018-11-30 06:08:00 2321

2321 了解適用于Zynq-7000 All Programmable SoC的Windows Embedded Compact 7板級支持包(BSP)。

2018-11-30 06:06:00 3214

3214 ADI公司在Embedded World 2015上展示了采用Zynq SDR套件的DDS HLS IP

2018-11-30 06:44:00 3026

3026 DAVE嵌入式系統(tǒng)在嵌入式世界2015中展示了Matrix多重HLS IP和DAVE Bora套件

2018-11-30 06:43:00 2010

2010 iVeia使用嵌入式世界2015中的iVeia視覺套件演示了Canny邊緣檢測HLS IP

2018-11-30 06:41:00 2648

2648 安富利展示了一個集成的工業(yè)物聯(lián)網(wǎng)(IoT)系統(tǒng),集成了Xilinx Zynq-7000 All Programmable SoC上的機器視覺,電機控制和近場通信(NFC)。

2018-11-26 07:00:00 2840

2840 了解如何使用BootGen為Zynq-7000 All Programmable SoC構建完整的映像。

引導映像通常包括第一級引導加載程序,至少一個軟件應用程序和PL的比特流。

2018-11-23 06:58:00 5211

5211 通過Zynq-7000 AP SoC了解電源管理技術,并了解Zynq Power Demonstration的這些技術。

2018-11-22 06:54:00 3500

3500 ,Zynq-7000 AP SoC可以在許多應用中廣泛使用。Zedboard強大的板載外圍設備和擴展功能組合使其成為新手和經(jīng)驗豐富的設計師的理想平臺。

2019-02-13 17:16:33 37

37 現(xiàn)在讓我們看一下平臺電子產品巨頭公司采取哪些措施來提高其盈利能力;Zynq SoC為何遠優(yōu)于ASIC、單獨的ASSP甚至是ASSP+FPGA雙芯片平臺實現(xiàn)方案;以及您如何順利利用Zynq SoC迅速提高自己公司的盈利能力。

2019-07-24 16:25:29 1984

1984 zynq-7000 SoC產品選型指南

2020-12-09 16:15:01 12

12 Zynq-7000 SoC數(shù)據(jù)手冊下載

2021-05-21 15:22:41 28

28 這篇博文特別關注 Zynq SoC 的多用途 IO (MIO, Multipurpose IO) 模塊。

2022-03-30 11:43:29 1452

1452 在 AXI 基礎第 6 講 - Vitis HLS 中的 AXI4-Lite 簡介中,使用 C 語言在 HLS 中創(chuàng)建包含 AXI4-Lite 接口的 IP。在本篇博文中,我們將學習如何導出 IP

2022-08-02 09:43:05 579

579

這里向大家介紹使用HLS封裝的縮放IP來實現(xiàn)視頻圖像縮放功能。將HLS封裝的縮放IP加入到OV5640圖像傳輸系統(tǒng),驗證圖像放大和縮小功能。

2022-10-11 14:21:50 1517

1517 Xilinx平臺的Vivado HLS 和 Vitis HLS 使用的 export_ip 命令會無法導出 IP

2023-07-07 14:14:57 338

338

該項目演示如何在 Zynq SoC 上開始使用 FreeRTOS。

2023-10-18 09:44:15 473

473

正在加载...

電子發(fā)燒友App

電子發(fā)燒友App

評論