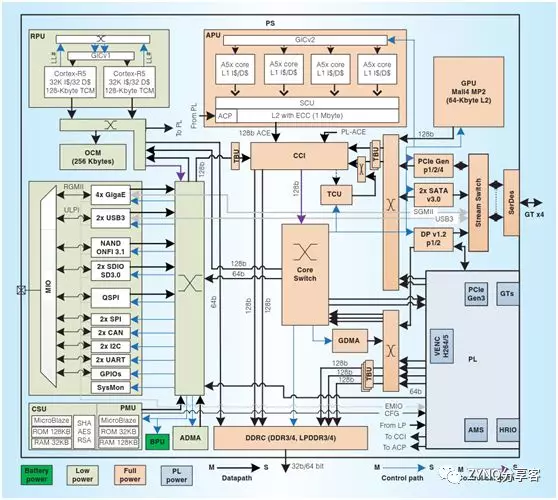

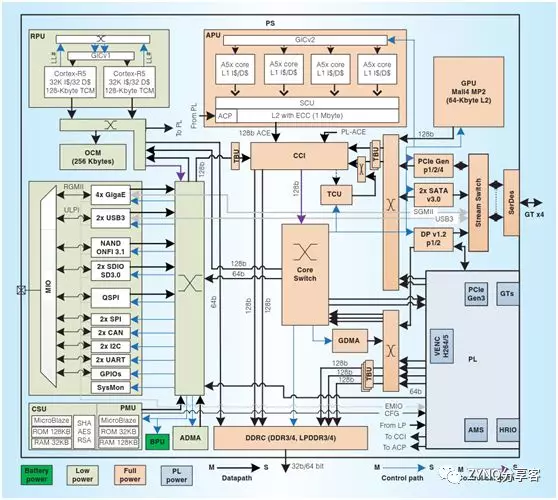

UltraScale+MPSoC系列器件共有四個大的系列,分別是CG系列、EG系列和EV系列,其中EG系列和EV系列提供汽車級和軍品級器件。 相較與上一代ZYNQ-7000產品,器件性能優越性主要體現在

2020-12-17 10:53:42 19692

19692

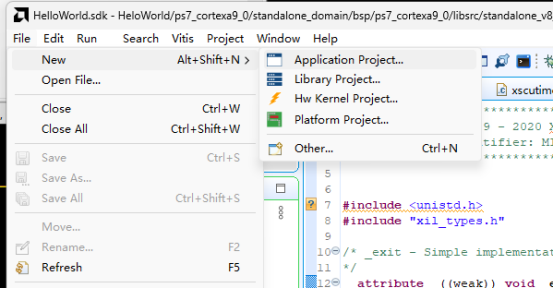

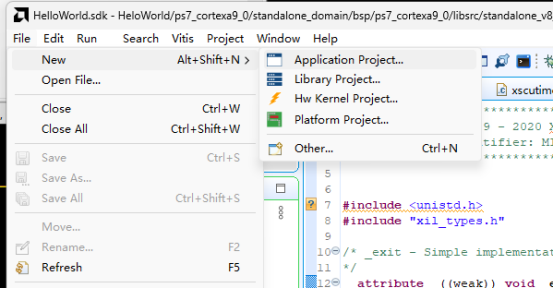

前言: 前面我們都是使用JTAG方式下載比特流文件,然后下載elf文件,最后點擊Run as或者Debug as來運行程序。JTAG方式是通過tcl腳本來初始化PS,然后用JTAG收發信息,優點

2020-12-26 10:08:50 8035

8035

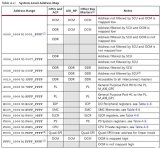

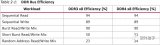

MPSoC有六個PL側高性能(HP)AXI主接口連接到PS側的FPD(PL-FPD AXI Masters),可以訪問PS側的所有從設備。這些高帶寬的接口主要用于訪問DDR內存。有四個HP AXI

2022-07-22 09:25:24 2501

2501 《基于“礦板”低成本學習Zynq系列》之六-DDR測試

2023-07-19 19:19:44 1744

1744

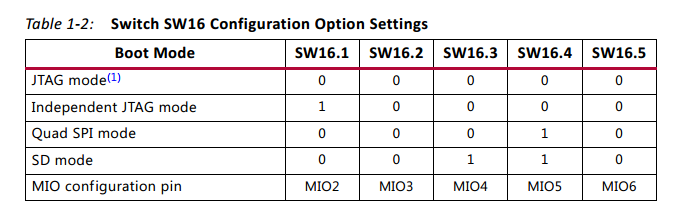

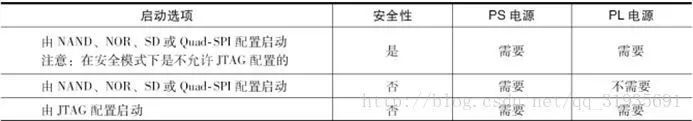

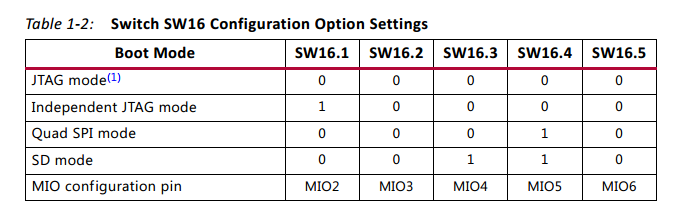

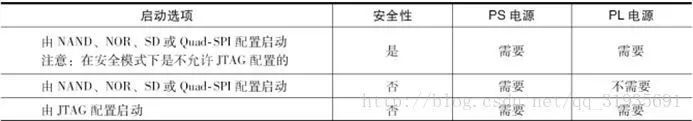

Zynq-7000AP SOC器件有效利用了片上CPU來幫忙配置,在沒有外部JTAG的情況下,處理系統(PS)與可編程邏輯(PL)都必須依靠PS來完成芯片的初始化配置。 ZYNQ的兩種啟動模式:從BootROM主動啟動,從JTAG被動啟動。

2023-08-02 09:33:09 736

736

在 AMD SoC 器件(AMD Zynq 7000 SoC,AMD Zynq UltraScale+ MPSoC,AMD Versal Adaptive SoC),常見的啟動方式是通過加載外部

2023-12-22 10:27:25 506

506

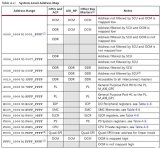

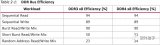

DDR SDRAM訪問特性DDR控制器效率對比

2021-02-04 07:14:23

通過 JTAG 手動初始化 DDR 控制器后,我試圖訪問 DDR 內存區域,但它總是失敗據我了解,必須使用信任區地址空間控制器映射區域,因此我嘗試執行 lsdk2012 中的 u-boot 所做

2023-03-29 07:58:56

JTAG口如何配置?怎么使用?

2021-10-29 07:22:26

我設計的是FPGA的板子,用JTAG燒寫。直接燒FPGA是沒有問題的,但是燒ROM就會出錯,IDCODE=ff檢驗不通過。網上有人說是JTAG的電平不夠。求問是不是布線的時候JTAG口距離FPGA一定要近一些,線短一些才行?

2013-07-26 15:29:20

、JTAGJTAG的基本原理是在器件內部定義一個TAP(測試訪問口),通過專用的JTAG測試工具對內部節點進行測試。除了TAP之外,混合IC還包含移位寄存器和狀態機,該狀態機被稱為TAP控制器,以執行邊界掃描功能。JTAG測試允許多個器件通過JTAG接口串聯在一起,形成一個JTAG鏈,能實現對各個器件分別測試

2022-02-17 08:00:13

ZYNQ-7000的USB轉JTAG驅動無法使用 使用操作系統是win7 64位 有人遇到過這個問題嗎?

2013-07-10 22:06:48

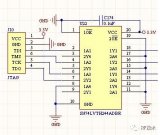

51一樣應用,那么你可以參考一下。參考文章EBAZ4205 ZYNQ 7Z010 裸機程序NAND固化 JTAG調試方法如果本文有地方寫的不清楚可以跳轉過去看下。本文主要是硬件改動,軟件燒錄與測試方法與參考文章并無區別。可以先看完本文的硬件改動后再看參考文章,改動的地方主要是原理圖中標紅色框的這兩個電阻(

2022-01-06 07:52:41

ZYNQ 分為 PS 和 PL 兩部分,那么器件的引腳(Pin)資源同樣也分成了兩部分。ZYNQ PS 中的外設可以通過 MIO(Multiuse I/O,多用輸入/輸出)模塊連接到 PS 端的引腳

2022-02-08 07:27:16

你好!我在ZYNQ 7015里(或者7035)調用XDMA PCIE IP 從上位機HOST PC通過PCIE接口給ZYNQ的PS DDR發送數據(XDMA PCIE IP接到了PS的AXI HP

2019-11-21 10:35:01

1、Zynq MPSoC支持的DDR介紹自己做自己的嵌入式產品一般要選擇合適的DDR,而這里開發板給的是4GB的UIMM的DDR4,也就是電腦上用的,所以用不了,只能自己掛載Component,這里

2022-04-19 17:56:03

其實是剛接觸 Zynq 軟硬件設計時需要了解的最基本開發流程,也是PL和PS設計結合的完美體現。 但是,上述開發的過程都有一個基本的前提,就是 Zynq 開發板是通過 JTAG 直接與電腦相連,然后

2021-01-08 16:33:01

本文主要與大家分享了Zynq在非JTAG模式下的啟動配置流程,旨在讓大家對Zynq的三階段啟動模式有一個具體的認識,希望大家多多交流。

2021-03-17 07:36:30

jtag接口或者SWD接口的單片機如何通過網口燒寫程序?

2023-11-08 06:55:00

、USB口、UART-RS422、千兆網、JTAG調試等接口。二、基礎接口和性能核心板:使用 Zynq-7100SoC 對嵌入式應用進行快速原型設計以實現優化;PS端包含Dual ARM

2020-03-24 09:39:49

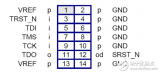

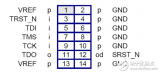

SRST PINTOCONNECT DIGILENT USB-JTAG2請給它一個清晰度6.我們設計的設計僅限14針JTAG。因此,計劃通過以太網將PS應用程序編程并存儲在QSPI中,因此通過JTAG

2020-03-12 14:39:42

大家好,有一個AXI VDMA IP,它可以很好地使用HP端口從zynq zc706上的PS DDR獲取1920x1080 @ 60Hz視頻。我們可以使用相同的IP在zynq zc706上使用HP

2019-04-09 06:10:12

現象: 在排除了下載線的問題后,還是不能訪問FPGA的JTAG口,那么很有可能你的FPGA芯片的JTAG口已經損壞。此時請用萬用表檢查TCK,TMS,TDO和Tdi是否和GND短路,如果任何一個信號對地短路則表示JTAG信號管腳已經損壞。

2019-05-31 07:01:06

NUC970系列可以通過USB的ISP方式燒錄到Nandflash/SPIFlash/eMMC/DDR/SRAM等。

2023-06-15 11:07:00

親愛的支持,我正在嘗試設計一個基于zynq7000設備的定制板。目前的情況是VIVADO 2016.4無法通過DLC9LPMC檢測到JTAG端口上存活的任何設備。我在這個論壇和其他搜索引擎中檢查了

2020-06-10 13:47:27

ZXB-27DR-8T8R 數模混合信號處理卡,采用Xilinx ZYNQ UltraScale+RFSoCZU27DR,

可以訪問大型FPGA 門密度,8 路ADC / DAC 端口,可擴展I

2023-08-25 15:11:55

描述PMP10601 參考設計提供為 Xilinx? Zynq? 7000 系列 (XC7Z015) FPGA供電時所需的所有電源軌。此設計使用多個 LMZ3 系列模塊、多個 LDO 和一個 DDR

2018-07-13 03:11:34

描述該參考設計采用多種 TPS54325 和其他 TI 電源器件,是適用于 Xilinx Zynq FPGA 的全套電源解決方案。輸入電壓達到 12V 后,該參考解決方案可提供 Zynq FPGA

2018-09-11 09:14:38

Xilinx-ZYNQ7000系列-學習筆記(3):系統復位與啟動一、復位ZYNQ-7000 SoC系統中的復位可以由硬件、看門狗定時器、JTAG控制器或軟件產生,可用于驅動系統中每個模塊的復位信號

2022-01-25 06:49:13

Xilinx-ZYNQ7000系列-學習筆記(3):系統復位與啟動一、復位ZYNQ-7000 SoC系統中的復位可以由硬件、看門狗定時器、JTAG控制器或軟件產生,可用于驅動系統中每個模塊的復位信號

2022-01-25 07:05:36

DDR 終端穩壓器。它還具有一個用于加電和斷電排序的 LM3880。此設計采用 12V 輸入電壓。特性提供 Xilinx? Zynq? 7000 系列 (XC7Z015) 所需的所有電源軌設計已經過優化,支持 12V 輸入板載加電和斷電排序支持 DDR3 存儲器件模塊設計,使用方便`

2015-05-08 16:17:26

DDR 終端穩壓器提供為 FPGA 供電時所需的所有電源軌。它還具有一個用于加電和斷電排序的 LM3880。此設計采用 12V 輸入電壓。特性提供 Xilinx? Zynq? 7000 系列

2015-05-08 16:08:58

DDR 終端穩壓器。它還具有一個用于加電和斷電排序的LM3880。此設計采用 12V 輸入電壓。特性 提供 Xilinx? Zynq? 7000 系列 (XC7Z015) 所需的所有電源軌設計已經過優化,支持 12V 輸入板載加電和斷電排序支持 DDR3 存儲器件模塊設計,使用方便

2022-09-23 07:43:32

DDR 終端穩壓器提供為 FPGA供電時所需的所有電源軌。它還具有一個用于加電和斷電排序的 LM3880。此設計采用 12V 輸入電壓。特性提供 Xilinx? Zynq? 7000 系列

2022-09-28 06:24:34

`網上看到了各種版本,有說JTAG口要用3.3V,有說要用2.5V的。手頭有個USB_BLASTER的下載器。不知道具體要用多少伏的。還有一個問題,看官方手冊,說JTAG口的6腳不接。但是我手頭有個開發板,JTAG的6腳與4腳接在一起了。`

2017-10-18 11:29:10

,排除這類問題。如果還是不能訪問FPGA的JTAG口,那么很有可能你的FPGA芯片的JTAG口已經損壞。此時請用萬用表檢查TCK,TMS,TDO和Tdi是否和GND短路,如果任何一個信號對地短路則表示

2023-05-19 19:47:36

的內部資源包括 DDR 控制器,QSPI 控制器,OCM,IIC,SPI 等。

本教程提供一個最小的參考設計,使上位機可以通過 PCIE 端口,通過 S_AXI_GP0 端口訪問 ZYNQ 內部

2023-11-30 18:49:15

,排除這類問題。如果還是不能訪問FPGA的JTAG口,那么很有可能你的FPGA芯片的JTAG口已經損壞。此時請用萬用表檢查TCK,TMS,TDO和Tdi是否和GND短路,如果任何一個信號對地短路則表示

2024-01-19 21:19:29

視頻太大了,無法上傳,直接分享百度網盤了介紹一下內容【黑金ZYNQ7000系列原創視頻教程】20.Linux下的GPIO操作【黑金ZYNQ7000系列原創視頻教程】19.Linux下的hello

2016-11-14 21:04:04

描述該參考設計是一種可擴展的電源設計,旨在為基于 FPGA 的 Artix-7、Spartan-7 和 Zynq-7000 系列器件供電。此設計接收來自標準直流電源的電力,并通過明確的 Samtec

2019-01-03 13:47:48

你好我有Zynq 7z020板,我想訪問它的GPIO,但我找不到Zynq處理器文檔,所以我知道如何訪問Zynq GPIO?問候

2019-09-11 10:48:04

AVR單片機使用JTAG口作為普通I/O口的方法有哪幾種?JTAG口的配置方式是什么?如何去使用JTAG口?使用JTAG口需要注意什么事項?

2021-07-07 06:22:05

應該是“Xilinx模擬混合信號模塊”,是FPGA中的一個硬核。在7系列FPGA中,XADC提供了DRP和JTAG接口,用于訪問XADC的狀態和控制寄存器。Zynq中添加了第三個接口,稱作PS-XA...

2021-12-27 06:18:43

如附圖中所示,我需要ARM進行圓頂計算并將結果存儲到其DDR中,我希望這些數據可以通過AXI_GP或AXI_HP(在這種情況下,使用S_AXI_GP)通過微網格訪問。由于ARM

2019-10-31 07:49:52

小妹正在做一個軟件,想通過編程把數據傳到PC的并口在從其與jtag接口相連通過從JTAG口TDI串入數據和指令,再從TDO串出掃描結果,在主機上進行比對以實現測試,目前我主要用VC來編程。請問一下我

2008-08-15 16:21:01

如何調試Zynq UltraScale+ MPSoC VCU DDR控制器 Zynq UltraScale+ MPSoC VCU DDR 控制器是一款專用 DDR 控制器,只支持在 Zynq

2021-01-07 16:02:09

如何調試 Zynq UltraScale+ MPSoC VCU DDR 控制器?

2021-01-22 06:29:21

你好,我希望能夠從PL端寫入ZYNQ的DDR內存。異步數據寫入FIFO然后在某些時候(當FIFO中有足夠的數據時)使用DMA將其傳輸到Zynq的DDR.Any幫助表示贊賞。問候,弗雷德以上來自于谷歌

2019-04-09 13:25:12

)。Zynq 7030內置雙核ARM Cortex-A9 和可編程邏輯(等效于K7系列FPGA)的SOC解決方案。AD936x是ADI公司推出的零中頻的集成IC解決方案,支持雙發雙收。 本開發系統開源

2019-07-23 10:56:41

我有一個包含單個Spartan3-DSP XC3SD3400A的新電路板。我無法通過JTAG或串行SPI閃存對器件進行編程。我可以通過iMPACT對閃存芯片進行編程,但是當我對電路板進行電源循環

2019-05-22 14:21:39

HP總線。PL作為AXI HP主機,可以通過這4條總線實現對內存(DDR3)的讀寫訪問,這4條總線加總的極限帶寬,通常能夠超過DDR3的最大有效帶寬,因此,對于處理器與PL之間的數據交互,Zynq

2019-11-26 09:47:20

所需的所有電源軌(包括 DDR3 存儲器)。特性提供 Zynq FPGA 所需的所有電源軌可在 5V 至 12V 的寬輸入電壓范圍內運行極高密度的 PCB 設計可節省電路板面積支持 DDR3 存儲器件

2015-04-14 09:46:41

想diy一個小玩意,考慮到成本問題,只使用4層板用的主要芯片就兩個1.Xilinx ZYNQ XC7Z010-1CLG225 (15 * 15 0.8mm BGA)2.16bit DDR3 1片請問4層板能實現嗎?

2017-01-08 22:50:42

我一直在研究 BL2 上的 DDR 驅動程序,并注意到 *** 設置了對內存區域的訪問,在研究 CW 腳本時也是如此。是否需要初始化 *** 才能訪問 DDR 內存?我知道它不需要 MMU,但它與 TZ 一樣嗎?

2023-03-27 07:13:46

的Linux的xdevcfg設備來編程PL部件。有趣的解決方案是通過在同一芯片的PS部分運行的XVC遠程調試基于Zynq的設計。假設我將XAPP1251中描述的AXI-JTAG控制器添加到我的設計中,是否

2020-07-30 13:51:19

什么是JTAG 到底什么是JTAG呢? JTAG(Joint Test Action Group)聯合測試行動小組)是一種國際標準測試協議(IEEE 1149.1兼容),主要用于芯片內部測試。現在多數的高級器件都支持JTAG

2007-06-05 12:10:48 98

98 JTAG技術是一種嵌入式調試技術,芯片內部封裝了專門的測試電路TAP(測試訪問口),通過專用的JTAG測試工具對內部節點進行測試和控制,目前大多數ARM器件支持JTAG

2008-08-24 13:10:39 8144

8144

STM32 調試器不能通過 JTAG 連接器件

2015-12-07 17:52:55 0

0 本文介紹zynq上三種方式啟動文件的生成和注意事項,包括只用片上RAM(OCM)和使用DDR3兩種情況。 JTAG方式 JTAG方式是調試中最常用的方式,在SDK中 在“Project

2017-11-10 14:49:02 12374

12374

今天,賽靈思 Zynq-7000 SoC 和 Zynq UltraScale+ MPSoC 迎來一個新的產品系列及三款最新器件! 新的產品系列被稱為Zynq Z-7000S系列,三款新器件分別為

2017-02-08 04:25:13 517

517

部分IO資源概述 在新的Zynq UltraScale+系列器件中,PS端的IO得到了增強: a) MIO由Zynq-7000的54個增加到78個; b)除GTR信號外,所有其他的PS外設均可通過

2017-02-08 08:29:11 491

491

時鐘正常,就可以通過JTAG接口訪問CPU的內部寄存器和掛在CPU總線上的設備,如FLASH,RAM,SOC(比如4510B,44Box,AT91M系列)內置模塊的寄存器,象UART,Timers

2017-10-13 19:28:04 3

3 時鐘正常,就可以通過JTAG接口訪問CPU的內部寄存器和掛在CPU總線上的設備,如FLASH,RAM,SOC(比如4510B,44Box,AT91M系列)內置模塊的寄存器,象UART,Timers,GPIO等等的寄存器。

2017-11-15 13:06:30 2561

2561 ZYNQ 7系列所有可編程器件均可以在安全模式下通過靜態存儲器配置或者在非安全模式下通過JTAG或者靜態存儲器配置。 (1)JTAG模式主要用于開發和調試 (2)NAND、并行NOR、串行NOR

2017-11-17 10:25:52 22027

22027

以2個Cortex A9的ARM核為核心,還包括片上存儲器、片外存儲器接口(DDR)和一系列的外設接口。Zynq-7000系列將ARM CPU和外設集成在一個芯片內,使得Zynq-7000系列皆具處理器和FPGA雙重特性,特別適用于軟硬件協同設計。

2017-11-18 05:11:01 18880

18880

歡迎大家發言指出。 Zynq器件主要包括三種類型的存儲控制接口: ① DDR控制器,主要特性如下: ·支持DDR3、DDR2、LPDDR2; ·支持位寬為16比特或32比特,位寬為16比特時支持ECC。

2017-11-22 08:23:54 6195

6195

的測試電路TAP(TestAccessPort,測試訪問口),通過專用的JTAG測試工具對內部節點進行測試。

2018-01-11 09:45:50 28818

28818

ZYNQ-7000如何生成從Flash和SD卡啟動的鏡像文件 將PL與PS部分一起使用,并且通過JTAG下載到板子運行。對于ZYNQ,有多種啟動方式

2018-12-01 08:38:18 7278

7278

在ps的控制下,可以實現安全或非安全的配置所有ps和pl。通過zynq提供的JTAG接口,用戶可以在外部主機的控制下對zynq進行配置,zynq不支持最開始就配置pl的過程。

2019-05-15 11:41:31 7190

7190

JTAG-HS3是Digilent高性價比的高速Xilinx FPGA編程解決方案系列產品中的最新一款。在JTAG-HS1產品成功的基礎上,JTAG-HS3通過增加一個開漏緩沖器到引腳14來實現

2019-11-13 17:12:33 5009

5009

該參考設計具有多個 TPS54325 和其他功率器件,適用于 Xilinx Zynq FPGA。該參考設計可通過 12V 輸入提供 Zynq FPGA(包括 DDR3 存儲器)所需的電源軌。

2020-12-21 08:00:00 33

33 該參考設計具有多個 TPS54325 和其他功率器件,適用于 Xilinx Zynq FPGA。該參考設計可通過 12V 輸入提供 Zynq FPGA(包括 DDR3 存儲器)所需的電源軌。

2020-12-21 08:00:00 11

11 該參考設計具有多個 TPS54325 和其他功率器件,適用于 Xilinx Zynq FPGA。該參考設計可通過 12V 輸入提供 Zynq FPGA(包括 DDR3 存儲器)所需的電源軌。

2020-12-21 08:00:00 10

10 該參考設計具有多個 TPS54325 和其他功率器件,適用于 Xilinx Zynq FPGA。該參考設計可通過 12V 輸入提供 Zynq FPGA(包括 DDR3 存儲器)所需的電源軌。

2020-12-21 08:00:00 8

8 該參考設計具有多個 TPS54325 和其他功率器件,適用于 Xilinx Zynq FPGA。該參考設計可通過 12V 輸入提供 Zynq FPGA(包括 DDR3 存儲器)所需的電源軌。

2020-12-23 16:47:38 43

43 Zynq UltraScale+ MPSoC VCU DDR 控制器是一款專用 DDR 控制器,只支持在 Zynq UltraScale+ MPSoC EV 部件上與 Zynq

2022-02-08 15:51:58 1421

1421 Xilinx 用兩個 96 位獨特器件標識符(稱為器件 DNA)為每個 Zynq UltraScale+ 器件編程。一個 DNA 值位于可編程邏輯 (PL) 中,另一個 DNA 值位于處理系統 (PS) 中。這兩個 DNA 值是不同的,但每個 DNA 都有以下屬性及讀取訪問方法。

2022-02-08 14:19:49 1149

1149

嘉合勁威(阿斯加特/光威品牌母公司)今天宣布,旗下的“神可”(Sinker)系列DDR4內存產品已經通過統信軟件的認證。

2021-01-28 11:02:10 1663

1663 Zynq UltraScale+ MPSoC VCU DDR 控制器是一款專用 DDR 控制器,只支持在 Zynq UltraScale+ MPSoC EV 部件上與 Zynq

2021-02-23 06:00:10 15

15 。如圖2.1所示,在相對較高層次對比了三種器件。Zynq MPSoC的PS部分比Zynq的PS部分面積更大,也更復雜。本章,將介紹這三種器件的特點。 2.1 技術時間線 進一步介紹之前,需要指出這三種

2021-04-02 17:20:14 13783

13783

本篇主要針對Zynq UltraScale + MPSoC的DDR接口,從硬件設計的角度進行詳細介紹,最后展示一下小編之前自己設計的基于ZU+的外掛8顆DDR4的設計。 目前比較常用的DDR

2021-09-16 10:17:02 4789

4789

上,也可以通過 EMIO 連接到 PL 端的引腳。Zynq-7000 系列芯片一般有 54 個 MIO,個別芯片如 7z007s 只有 32 個。GPIO 是英文“general purpose I/O”的縮寫,即通用的輸入/輸出。是 ZYNQ PS 中的一個外設,用于觀測和控制器件引腳的狀態。圖 1

2021-12-04 18:51:06 16

16 一、JTAGJTAG的基本原理是在器件內部定義一個TAP(測試訪問口),通過專用的JTAG測試工具對內部節點進行測試。除了TAP之外,混合IC還包含移位寄存器和狀態機,該狀態機被稱為TAP控制器,以執行邊界掃描功能。JTAG測試允許多個器件通過JTAG接口串聯在一起,形成一個JTAG鏈,能實現對各個器件分別測試

2021-12-22 19:05:58 17

17 應該是“Xilinx模擬混合信號模塊”,是FPGA中的一個硬核。在7系列FPGA中,XADC提供了DRP和JTAG接口,用于訪問XADC的狀態和控制寄存器。Zynq中添加了第三個接口,稱作PS-XA...

2022-01-05 14:26:11 10

10 Zynq MPSoC是Zynq-7000 SoC(之后簡稱Zynq)的進化版本。Zynq是賽靈思發布的集成PL(FPGA)和PS設計的最早的一代產品。如圖2.1所示,在相對較高層次對比了三種器件。Zynq MPSoC的PS部分比Zynq的PS部分面積更大,也更復雜。本章,將介紹這三種器件的特點.

2022-08-15 09:16:38 1629

1629 在無 JTAG 的模式下,Zynq 是通過片上CPU完成對芯片的配置,也就是PS和PL的配置是通過 PS 處理器 ARM 核來實現的。需要注意的是,與傳統的 Xilinx 7 系列 FPGA 芯片不同,Zynq 是不支持從 PL 端進行直接啟動配置的,一定要通過 PS 部分來完成。

2022-10-19 09:11:55 986

986 在線仿真、調試,它在芯片內部封裝了專門的測試電路 TAP ( Test Access Port ,測試訪問口),通過專用的JTAG測試工具對芯片進行測試。現在多數的高級器件都支持JTAG協議,如以以ARM

2023-06-14 09:15:46 7242

7242

電子發燒友網站提供《IEEE 1149.1 JTAG測試訪問端口復位要求應用說明.pdf》資料免費下載

2023-07-26 15:45:42 0

0

電子發燒友App

電子發燒友App

評論