本文首先會對這個問題進行一般性地分析,在此基礎上我們將以德州儀器公司 10G SERDES 器件 TLK10002 為例,提出一個新的解決方案,即采用雙時鐘模式提供 SERDES系統時鐘,并且探討

2013-09-26 14:34:31 3258

3258

不夠的情況下有可能會造成 FIFO 的溢出。本文首先會對這個問題進行一般性地分析,在此基礎上我們將以德州儀器公司 10G SERDES 器件 TLK10002 為例,提出一個新的解決方案,即采用雙時鐘模式提供 SERDES系統時鐘。

2013-09-29 10:05:45 2100

2100

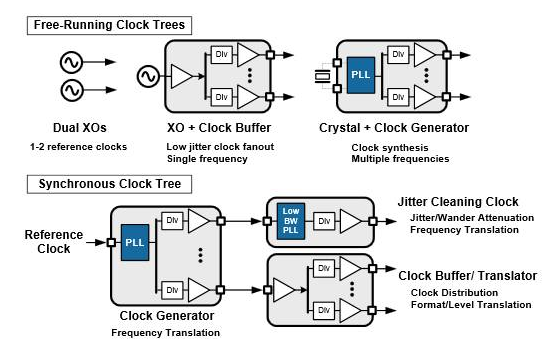

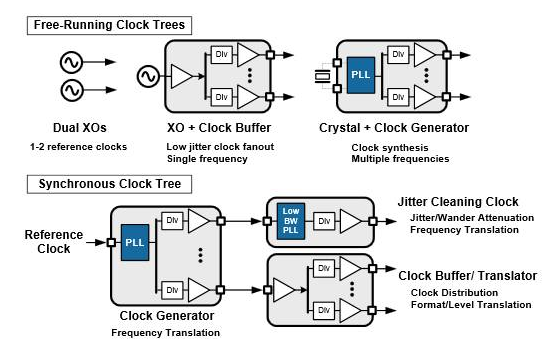

在高性能應用中,例如通信、無線基礎設施、服務器、廣播視頻以及測試和測量裝置,當系統集成更多功能并需要提高性能水平時,硬件設計就變得日益復雜,為系統提供參考時序的板級時鐘樹也走向這種趨勢。在進行時鐘

2017-10-31 09:45:13 5550

5550

GMII、SGMII和SerDes的區別和聯系? GMII和SGMII區別,上一篇已經介紹了,這一篇重點介紹SGMII和SerDes區別。 GMII和SGMII SGMII接口 SGMII

2020-10-09 11:31:29 29959

29959

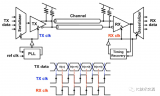

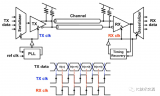

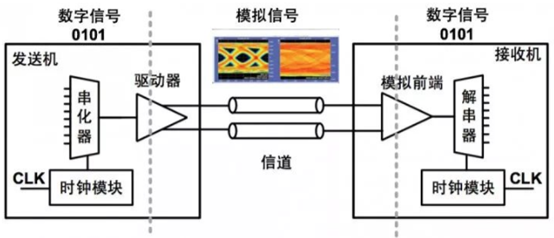

SerDes是串化(Serializer)和解串(Deserializer)的簡稱,下圖給出了PHY的簡圖。發送端發送并行數據,時鐘由ref_clk經過PLL鎖相環振出的時鐘提供,經過差分對信號傳輸至接收端,通過CDR恢復時鐘并解串數據。

2023-08-16 17:19:23 2740

2740

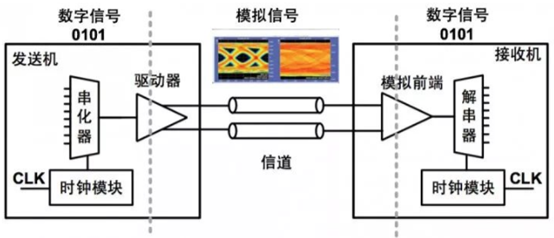

SerDes是SERializer(串行器)/DESerializer(解串器)的簡稱,是一種主流的時分多路復用(TDM)、點對點(P2P)的串行通信技術。

2023-11-14 09:32:39 2479

2479

SERDES是英文SERializer(串行器)/DESerializer(解串器)的簡稱。

2024-01-04 09:04:02 495

495

親愛的Xilinx論壇,我正在實現基于SERDES協議的序列化傳輸。我需要在Kintex7上接收8個差分對,這些差分對承載由另一個Kintex7串行化的64位字,主時鐘為100MHz。將托管FPGA

2020-03-17 09:53:11

/10b的SerDes接口,包括SERDES收發單元,通過完全數字化的方法實現SERDES的CDR(Clock Data Recovery,時鐘數據恢復),完成100~200Mhz的板間SERDES單通道

2019-05-29 17:52:03

用戶在產品選型和方案設計之初,對于硬件接口資源分配不熟悉,不遵守芯片規范使用導致項目出現問題,造成了嚴重損失。本期我們就此系列平臺的SerDes資源分配做一篇文章。LS系列產品的資源不可為不豐富,其中最讓人頭暈的當屬于SerDes協議。百度百科這樣解釋,SERDES是英文SERializer(串行器)/DE

2021-12-20 06:01:37

到Serial RIO,…等等,都是在借助SerDes來提高性能。SerDes是非常復雜的數模混合設計,用戶手冊的內容只是描述了森林里面的一棵小樹,并不能夠解釋SerDes是怎么工作的。SerDes怎么...

2021-07-28 07:02:12

SerDes的發送端TX的均衡原理是什么?怎樣利用高速接口SerDes去實現芯片間信號的有線傳輸?

2021-06-17 07:15:16

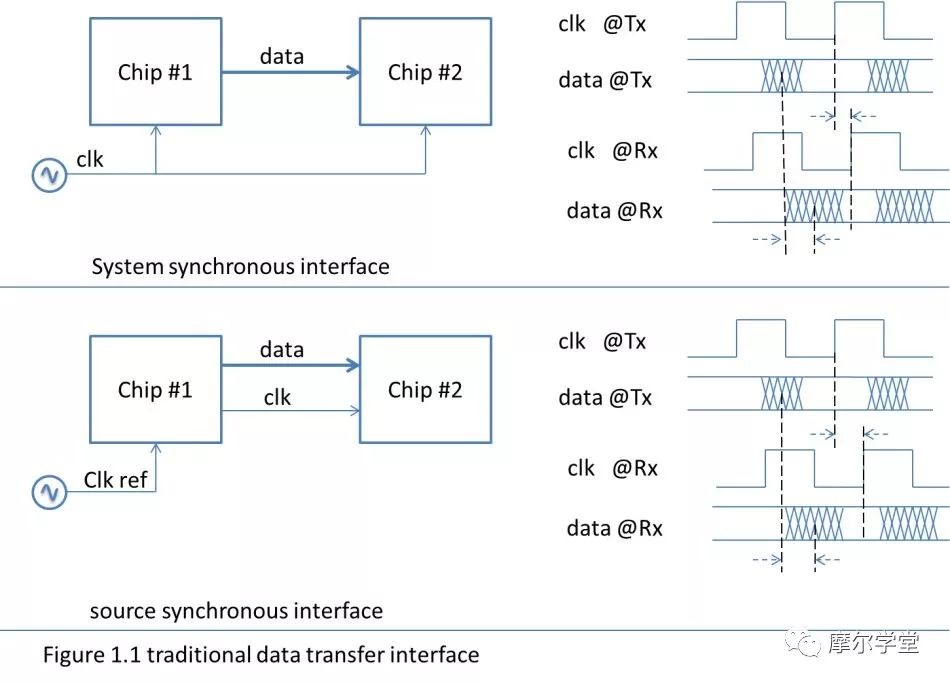

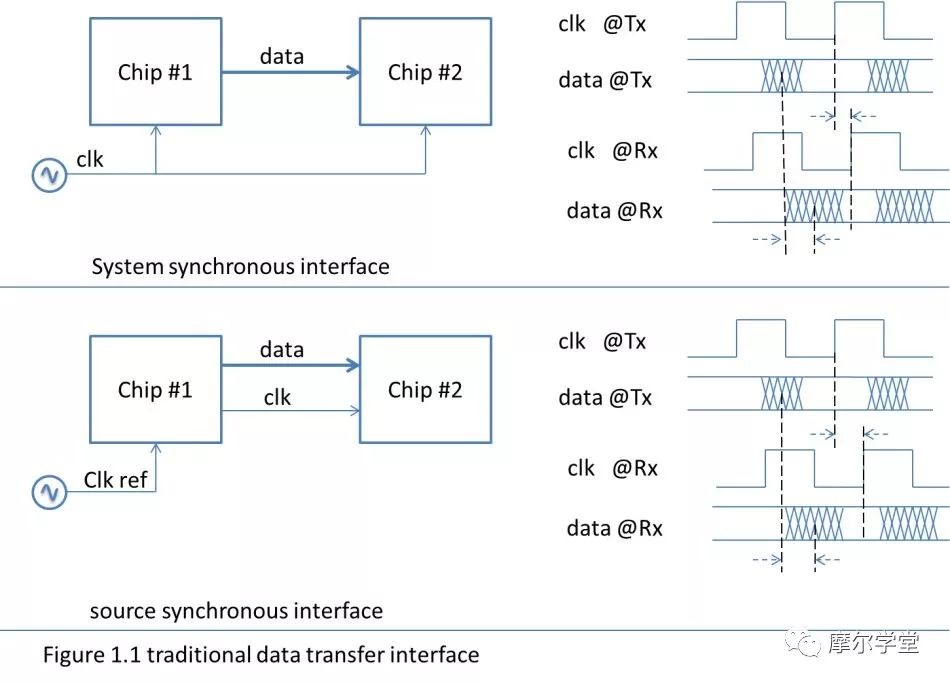

一、SERDES的作用1.1并行總線接口在SerDes流行之前,芯片之間的互聯通過系統同步或者源同步的并行接口傳輸數據,圖1.1演示了系統和源同步并行接口。隨著接口頻率的提高,在系統同步接口方式中

2021-07-26 07:33:44

一、SERDES的作用1.1并行總線接口在SerDes流行之前,芯片之間的互聯通過系統同步或者源同步的并行接口傳輸數據,圖1.1演示了系統和源同步并行接口。隨著接口頻率的提高,在系統同步接口方式中,有幾個因素限制了有效數據窗口寬度的繼續增加。a)、時鐘...

2021-07-28 08:35:42

我想用serdes ip模擬圖書館的位置在哪里?

2020-05-20 15:05:17

對高速信號進行高分辨率的數字化處理需審慎選擇時鐘,才不至于使其影響模數轉換器(ADC)的性能。那么時鐘抖動會對高速ADC的性能有什么影響呢?

2021-04-08 06:00:04

在本文中,我們將討論抖動傳遞及其性能,以及相位噪聲測量技術的局限性。 時鐘抖動和邊沿速率 圖1顯示了由一個通用公式表述的三種波形。該公式包括相位噪聲項“φ(t)”和幅度噪聲項“λ(t)。對評估的三個

2022-11-23 07:59:49

時鐘相噪對ADC性能的影響是什么?鎖相環的基本原理和相噪優化方式

2021-04-07 06:25:40

如題,9176DAC的PLL鎖上了,證明時鐘應該沒問題,但是為什么DLL和serdes PLL鎖不上呢?配置順序,我是按照手冊的START-UP SEQUENCE進行配置的。

2023-12-01 06:54:09

串行接口常用于芯片至芯片和電路板至電路板之間的數據傳輸。隨著系統帶寬不斷增加至多吉比特范圍,并行接口已經被高速串行鏈接,或SERDES (串化器/ 解串器)所取代。起初, SERDES 是獨立

2019-10-23 07:16:35

SerDes在93000平臺上量產測試。本文將介紹Nautilus UDI方案是如何實現高速SerDes測試的,包括UDI結構,輸入時鐘設計,Load board設計,socket選型等多個測試環節。

2021-05-10 06:58:55

STM32系統架構基礎名詞有哪些呢?STM32時鐘系統有哪些性能呢?

2021-12-14 07:49:07

),. clk_out1(link_clock))從serdes TX時鐘制作繪圖時鐘;我希望鏈接時鐘是txusrclk的兩倍,因為GTX一次使用兩個字節。但是link_clock是靜態的,DRP_CLK_O是200Mhz,gt0_pll0lock_out是16Khz的方波。系統似乎一直在重置!戴夫

2020-07-31 09:10:30

我想把c6455 srio配置為1P4X的模式,是不是這種模式下只使用一個port,那么我在設置寄存器SERDES_CFGRXn_CNTL和SERDES_CFGTXn_CNTL的時候,只使能

2019-01-21 15:42:20

大家好。BUFG資源和DCM / PLL模塊在許多FPGA線路上使用專用時鐘布線資源。對于SerDes應用,我們使用BUFIO2來獲得DDR SerDes IOCLK,SerDes Strobe

2019-07-30 10:35:37

大家好, 在一個I / O塊中有一個主serdes和一個slave serdes。如果我使用主設備,奴隸不能使用,是不是?謝謝。最好的祝福。

2020-06-08 15:03:22

什么是SerDes?

2021-06-24 07:52:02

嗨, 我計劃在我的設計中使用SERDES(LVDS)作為背板。我已經瀏覽了virtex5用戶指南中的advnced IO部分,并看過ISERDES_NODELAY和OSERDES宏。我已經看到了一些

2020-07-13 15:54:49

沖突、降低開關噪聲、更低的功耗和封裝成本等許多好處。而SERDES技術的主要缺點是需要非常精確、超低抖動的元件來提供用于控制高數據速率串行信號所需的參考時鐘。即使嚴格控制元件布局,使用長度短的信號并

2019-05-21 05:00:13

本文將討論通過優化封裝內的阻抗不連續性和改善其回波損耗性能,以滿足10Gbps SerDes鍵合線封裝規范。

2021-04-25 07:42:13

約束將無法在時序分析期間返回任何路徑”,因此,當我們使用輸入SerDes時鐘資源來生成DDR時鐘時,我們不會期望任何分析甚至是建立/保持違規的通知。2)在同一白皮書中,“OFFSET約束不優化由內部

2019-08-09 09:54:33

我在官網上下載了CH569的數據手冊和參考應用例程(EVT), 發現對SerDes這塊的介紹很少, 而且EVT里也沒有SerDes相關的例程.我想使用SerDes連接SFP模塊來測試光纖通信.請問可以提供下關于SerDes的詳細資料嗎, 謝謝.

2022-05-18 08:37:16

需要生成一個低速單端時鐘來測試非常慢的serdes通道(長篇故事為什么它如此低和單端)。我試圖在低頻模式下使用V5 DCM接受2.5MHz的輸入時鐘并產生15MHz-17.5MHz。當我使用GUI

2020-06-15 16:11:09

如何更有效地使用可編程時鐘器件?設計SERDES參考時鐘源面臨的挑戰有哪些?如何去實現XAUI參考時鐘源?

2021-04-20 06:03:53

Recovery,時鐘數據恢復),完成100~200Mhz的板間SERDES單通道通信,該SERDES接口方案具有成本低、靈活性高、研發周期短等特點。

2019-10-21 07:09:44

SerDes的基本結構是由哪些部分組成的?怎樣去更好地使用SerDes?

2021-09-22 06:25:17

SerDes是怎么工作的?SerDes有傳輸時鐘信號嗎?

2021-10-18 08:53:42

SERDES的作用有哪些?SerDes的主要構成可以分為哪幾部分?

2021-10-18 09:25:08

漂移及漂移形成的原因是什么?光纖漂移引起的SERDES FIFO溢出問題分析BBU SERDES 雙系時鐘方案及具體實現

2021-04-19 08:35:11

的serdes?2、如果serdes是各自的,是否共享輸入時鐘?(外部時鐘,對于我們來說是156.25MHz)3、在研究SRIO速率配置時發現文檔中描述:serdes的輸出時鐘不能超過3.125GHz,該描述是否準確?是否適用于所有的serdes模塊?謝謝!

2018-08-06 06:17:36

6678中的srio的serdes和以太網的serdes是共用還是各自有自己的serdes?

2018-08-02 06:11:31

7系列系列中的SERDES是否有最小延遲規范?我想了解如果SERDES直接(最短路徑)連接到另一個SERDES以實現GTH收發器之間的最小延遲串行到串行連接,那將是什么樣的。

2020-07-22 13:45:34

bufg用于非時鐘輸入邏輯?你可以使用組合邏輯和serdes選通來獲得時序嗎?以上來自于谷歌翻譯以下為原文I'm a bit confused on the Spartan 6 clocking when

2019-06-19 06:38:52

選擇SerDes參考時鐘。各功能需要的時鐘如下圖:這就是我們需要配置的PLL1和PLL2,硬件和軟件需要同時做好。參考的時鐘源我們在核心板上已經做好,用戶不需要額外做這部分的硬件。 具體是這樣實現

2020-10-28 17:15:14

之后,還需要選擇SerDes參考時鐘。各功能需要的時鐘如下圖:?這就是我們需要配置的PLL1和PLL2,硬件和軟件需要同時做好。參考的時鐘源我們在核心板上已經做好,用戶不需要額外做這部分的硬件。 具體

2020-11-01 20:21:02

SERDES結構是怎樣構成的?高速SERDES接口在網絡方面有哪些應用?

2021-04-28 07:19:38

SerDes/Differential Pair-- The Feature of High Speed Designreference list– reference1:link 應對未來高速

2021-11-12 06:46:26

引言在有線通信中,需要從數據中恢復時鐘。將時鐘編碼到數據中的優點是可以省卻發送時鐘的線路,也有助于處理偏移問題。SERDES(串行器-解串器)器件諸如SCAN25100可

2008-08-15 22:51:17 21

21 M31 SerDes PHY IP M31 SerDes PHY IP為高帶寬應用提供高性能、多通道功能和低功耗架構。SerDes IP支持從1.25G到10.3125Gbps的數據速率

2023-04-03 20:29:47

串行接口常用于芯片至芯片和電路板至電路板之間的數據傳輸。隨著系統的帶寬不斷增加至多吉比特范圍,并行接口已經被高速串行鏈接,或SERDES (串化器/ 解串器)所取代。起初

2010-02-25 23:03:44 38

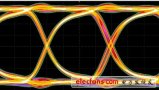

38 利用眼圖模板評估串行器和解串器(SerDes)的性能

Abstract: Maxim has developed a family of serializer and deserializer

2008-11-26 14:08:24 2054

2054

摘要:Maxim開發了一系列串行器和解串器,廣泛用于視頻顯示和數字圖像系統中的高速、串行數據互聯。目前,設計人員急需找到一種測試由串行器和解串器(SerDes)芯片組搭建的串行

2009-05-02 10:32:33 2031

2031

該應用筆記介紹如何根據STO超時、時鐘頻率和UART位時鐘計算MAX9257/MAX9258可編程串行器/解串器(SerDes)的CCEN持續時間。

2011-07-30 22:55:13 1353

1353

討論了物理設計中時鐘網絡的設計技術,并以現有的CPU時鐘網絡的為例,介紹了高性能CPU的時鐘網絡設計技術。

2011-12-27 15:28:56 46

46 SERDES在數字系統中高效時鐘設計方案,無論是在一個FPGA、SoC還是ASSP中,為任何基于SERDES的協議選擇一個參考時鐘源都是非常具有挑戰性的。

2012-02-16 11:23:43 5384

5384

本文以TLK3132為例,詳細介紹了SERDES工作原理和器件特點,并以WI系統中的CPRI應用需求為例,提供TLK3132的設計方法等。

2012-05-07 16:01:58 6293

6293

電子發燒友網: 本文主要講述的是 LatticeECP4 高速可配置SERDES。 LatticeECP4 FPGA系列結合了高性能 FPGA 結構、高性能I/O和多達16個通道的嵌入式SERDES,帶有相關的物理編碼子層(PCS)邏輯。每

2012-06-12 10:41:35 1439

1439

FPGA SERDES的應用需要考慮到板級硬件,SERDES參數和使用,應用協議等方面。由于這種復雜性,SERDES的調試工作對很多工程師來說是一個挑戰。

2013-03-15 14:55:13 10360

10360

如何使用 HyperLynx DRC 來查找 SERDES 設計問題

2016-01-06 14:49:36 0

0 如何使用 HyperLynx DRC 來查找 SERDES 設計問題

2016-05-24 17:12:50 0

0 沖突、降低開關噪聲、更低的功耗和封裝成本等許多好處。而SERDES技術的主要缺點是需要非常精確、超低抖動的元件來提供用于控制高數據速率串行信號所需的參考時鐘。即使嚴格控制元件布局,使用長度短的信號并遵循信號走線限制,這些接口的抖動

2017-10-26 15:37:45 4

4 高性能CPU的時鐘網絡設計

2017-10-30 15:28:58 23

23 在很多無線或者有線的系統應用中,都需要器件的接收端能夠和鏈路的發送端的頻率做跟隨。通常的實現方案都是通過將SERDES的恢復時鐘引到芯片外部,然后通過一個cleanup PLL過濾抖動,然后同時再生出低相位抖動的跟隨時鐘,然后將此時鐘作為SERDES的參考時鐘。

2017-11-18 12:08:49 5864

5864

的量產測試。那么,Nautilus UDI方案是如何實現包括UDI結構、輸入時鐘設計、Load board設計、socket選型等多個測試環節高速SerDes測試的呢?

2018-06-10 10:51:17 4434

4434

對于10Gbps及以上數據速率的SerDes,每個數據位的單位間隔是隨著近 20~30ps的信號上升/下降時間而縮短的。

2018-07-18 17:18:48 7390

7390

Recovery,時鐘數據恢復),完成100~200Mhz的板間SERDES單通道通信,該SERDES接口方案具有成本低、靈活性高、研發周期短等特點。

2019-05-24 15:33:25 4073

4073

只要SERDES接口的高級架構是合理的,SERDES總線的成功實現就歸結為“實現細節”。

2019-08-14 17:57:00 2615

2615 隨著SerDes 速度的增加,參考時鐘所需的 RMS 相位抖動性能隨之減少。在本次網絡研討會上,我們概述最新一代FPGA、光學DSP、相干DSP 和網絡處理器的參考時鐘要求,并重點介紹Si54x Ultra Series XO 和 VCXO 產品家族的關鍵功能

2020-11-03 17:13:10 2613

2613 為滿足目前的56GPAM-4 SerDes技術,以支持更高帶寬的100G+以太網和光網絡設計。硬件開發人員通常需要100fs(典型值)以下RMS相位抖動規范的時鐘。這些設計通常需要與CPU和系統時鐘等其他頻率時鐘混用。

2020-11-12 15:25:55 4154

4154 為了學習xilinx serdes 原語的使用,以及交流學習經驗,在工程項目中方便的應用SERDES進行設計,故編寫此文檔。

2021-02-26 10:04:00 37

37 ADN2865:連續速率12.3Mb/s至2.7 Gb/s時鐘和數據恢復IC,帶環路定時SERDES初步數據表

2021-05-09 14:33:49 7

7 ,另一個優勢是能夠通過一對差分對信號引腳(而不是8、16、32或N個數據引腳和一個時鐘引腳)發送數據。在串行傳輸這個方面得益于更小的數據包和更密集的pcb而節省了成本。具體取決于晶片成本、封裝成本、PCB成本和PCB擁塞等因素。 距離優勢 在過去的十年里,SERDES在PCB和基

2021-07-23 11:59:46 3795

3795 SerDes/Differential Pair-- The Feature of High Speed Designreference list– reference1:link 應對未來高速

2021-11-07 10:21:00 47

47 SERDES最明顯的優勢是具備更少的引腳數量和線纜/通道數量。對于早期的SERDES,這意味著數據可以通過同軸電纜或光纖發送。

2022-07-22 10:39:21 2436

2436 112Gbps SerDes設計將根據應用情況在各種配置中被采用。下圖展示了長距離(LR)、中距離(MR)、極短距離(VSR)和超短距離(XSR)拓撲,其中112G信令路徑在每個拓撲中都突出顯示。

2022-07-27 15:05:16 1091

1091 FPGA發展到今天,SerDes(Serializer-Deserializer)基本上是標配了。

2022-10-31 11:28:41 1350

1350 SerDes 是空間到時間到空間的轉換。并行數據同時傳輸但占用不同的物理互連,串行數據共享相同的物理空間但占用不同的時間時刻

2023-01-31 14:13:37 3369

3369 到Serial RIO……等等,都是在借助SerDes來提高數據傳輸的性能。SerDes是非常復雜的數模混合設計,用戶手冊的內容只是描述了相對粗略的概念以及使用方法,并不能完全解釋SerDes是怎么工作

2023-03-16 10:28:11 1915

1915

同時介紹一種采用光電集成技術的,即采用光SerDes而非電SerDes的高速收發器。

2023-04-01 09:28:58 1078

1078 首先我們要了解什么是SerDes,SerDes的應用場景又是什么呢?SerDes又有哪些常見的種類?

2023-06-06 17:03:55 4707

4707

8/10b的SerDes接口,包括SERDES收發單元,通過完全數字化的方法實現SERDES的CDR(Clock Data Recovery,時鐘數

2023-07-27 16:10:01 1566

1566

Xilinx公司的許多FPGA已經內置了一個或多個MGT(Multi-Gigabit Transceiver)收發器,也叫做SERDES(Multi-Gigabit Serializer/Deserializer)。MGT收發器內部包括高速串并轉換電路、時鐘數據恢復電路、數據編解碼電路、時鐘糾正和通道綁定電路

2023-07-29 16:47:04 468

468

業界高端FPGA的卓越性能和高口碑聲譽都有哪些因素了?其中很重要的一個因素就是FPGA內部豐富的時鐘資源使得FPGA在處理復雜時鐘結構和時序要求的設計中具有很大優勢。設計師可以更好地控制和管理時鐘信號,提高時序性能、減少時鐘相關問題,并滿足設計的高性能和穩定性要求。

2023-08-31 10:44:01 530

530 到Serial RIO……等等,都是在借助SerDes來提高數據傳輸的性能。SerDes是非常復雜的數模混合設計,用戶手冊的內容只是描述了相對粗略的概念以及使用方法,并不能完全解釋SerDes是怎么工作

2023-10-16 14:50:37 558

558

盡管設計和驗證很復雜,SERDES 已成為 SoC 模塊不可或缺的一部分。隨著 SERDES IP 模塊現已推出,它有助于緩解任何成本、風險和上市時間問題。

2023-10-23 14:44:59 449

449

正在加载...

電子發燒友App

電子發燒友App

評論