安全高效的狀態機設計對于任何使用FPGA的工程師而言都是一項重要技能。選擇Moore狀態機、Mealy狀態機還是混合機取決于整個系統的需求。無論選擇哪種類型的狀態機,充分掌握實現方案所需的工具和技巧,將確保您實現最佳解決方案。本文主要介紹如何在FPGA中實現狀態機

2013-03-29 15:02:57 12361

12361

FPGA 對絕大多數的人來說相對有些陌生。經常有朋友問我,你們成天搞的這個 FPGA 到底是什么東西。 我想很難用一兩句通俗易懂的語言解釋什么是 FPGA ,因為當今的 FPGA 已經是一個非常復雜

2018-03-31 08:20:01 25704

25704 1. 初識XILINX 初識XILINX,是PYNQ-Z2。當時剛學完學校的數字電路課程,對FPGA并不了解,學校課程也僅僅是用VHDL驗證了一些基礎的FPGA實驗,例如生成一個n進位序列

2020-11-05 15:56:42 4204

4204 即是相應的 HDL 程序以及最新非常流行的基于高層次綜合的程序方法,如Xilinx的一系列工具HLS、SDSoC和Altera的SoC EDS等。 (1)選擇FPGA(SoC)的若干理由 a)FPGA

2020-12-17 12:58:21 4094

4094 用軟件從 C 轉化來的 RTL 代碼其實并不好理解。今天我們就來談談,如何在不改變 RTL 代碼的情況下,提升設計性能。 本項目所需應用與工具:賽靈思HLS、Plunify Cloud 以及

2020-12-20 11:46:46 1416

1416

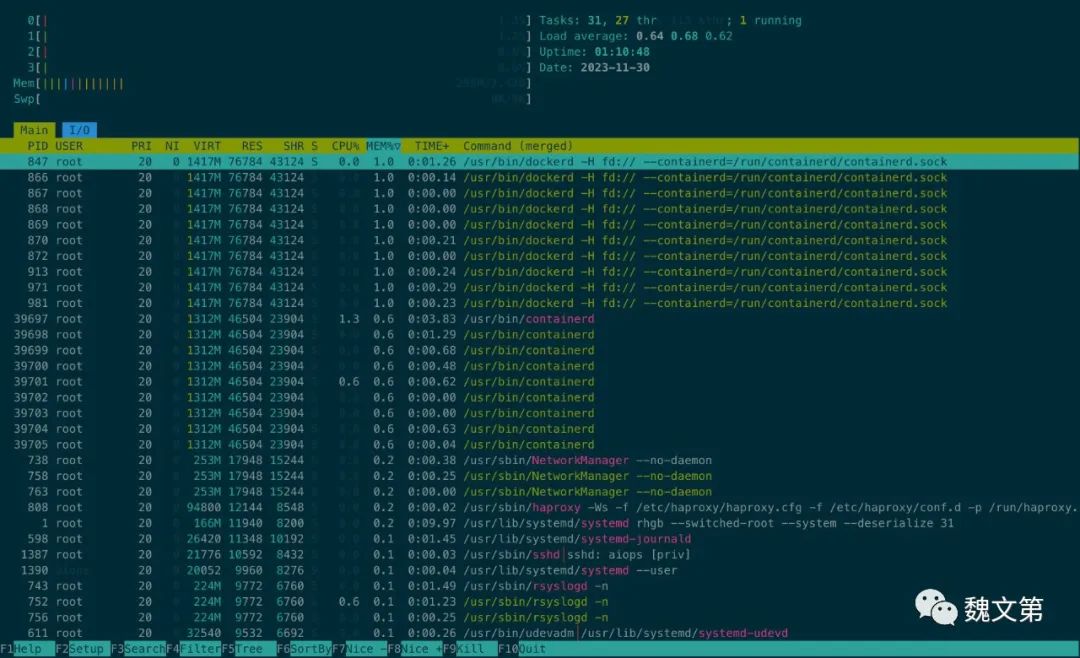

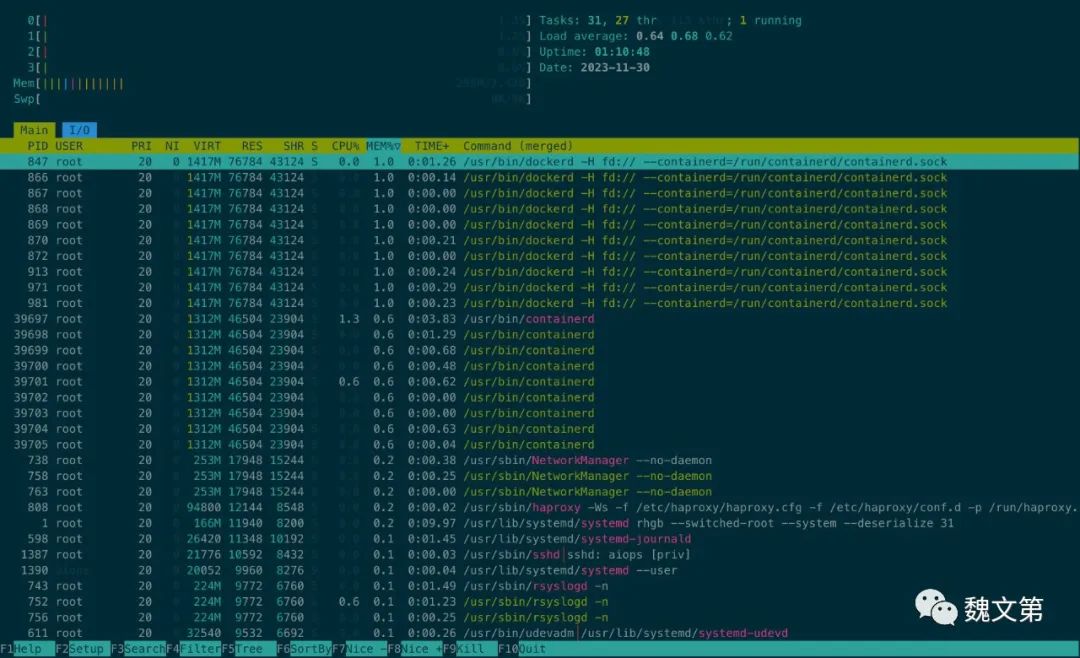

本文介紹如何在 Linux 中使用 htop 命令。

2023-12-04 14:45:28 441

441

和 GPU 不同, FPGA 不需要在內存和編程之間切換,這使得存儲和檢索數據的過程更高效。FPGA 架構靈活性更高,因此您可以自定義您希望 FPGA 用于特定任務的電源。

這種靈活性有助于將能耗極高的任務從

2023-06-28 18:18:57

簡化了 FPGA 的開發流程,使畫家的畫筆更好用更易用。HLS (High level Synthesis,高層次綜合)工具給“畫家”提供了新的畫筆——可以直接用抽象級別更高的c/c++進行硬件編程

2018-08-13 09:31:45

,大大簡化了 FPGA 的開發流程,使畫家的畫筆更好用更易用。HLS (High level Synthesis,高層次綜合)工具給“畫家”提供了新的畫筆——可以直接用抽象級別更高的c/c++進行硬件

2018-08-10 09:16:48

嗨, 我是National Instruments公司的應用工程師。如您所知,我們在許多產品中使用您的FPGA芯片組,最近我們收到了一位非常關注安全問題的客戶提出的問題。眾所周知,使用FPGA芯片組

2020-03-09 09:56:44

重要組成部分,所以我們將重點介紹Vitis HLS。LUT 或 SICELUT 或 SICE是構成了 FPGA 的區域。它的數量有限,當它用完時,意味著您的設計太大了!BRAM 或 Block

2022-09-07 15:21:54

BOARD EVAL FPGA BLACKFIN EXTENDR

2023-03-30 12:06:40

MODULE USB-TO-FPGA TRAINING TOOL

2023-04-06 11:27:13

MODULE USB-TO-FPGA TOOL W/MANUAL

2023-04-06 11:27:29

MODULE USB-TO-FPGA SPARTAN3

2023-04-06 11:27:13

MODULE USB-TO-FPGA SPARTAN 3A

2023-04-06 11:27:11

BOARD EVAL FOR ORCA OR4E6 FPGA

2023-03-30 11:49:36

TINYFPGA AX1

2024-03-14 22:18:36

TINYFPGA AX2

2024-03-14 22:18:36

TINYFPGA BX

2024-03-14 22:18:36

VIRTEX-5FPGA - DC and Switching Characteristics - Xilinx, Inc

2022-11-04 17:22:44

)對正點原子FPGA感興趣的同學可以加群討論:8767449005)關注正點原子公眾號,獲取最新資料第一章HLS簡介為了盡快把新產品推向市場,數字系統的設計者需要考慮如何加速設計開發的周期。設計加速

2020-10-10 16:44:42

為什么要在顯示器應用中使用FPGA?一種Spartan-3E顯示器解決方案板

2021-06-04 06:47:39

本帖最后由 eehome 于 2013-1-5 09:56 編輯

《成為Xilinx FPGA設計專家(基礎篇) 》是一朋友查閱各方面資料后加以梳理后整理出來的電子書。我在這里幫她宣傳一下...

2012-07-26 22:15:57

HLS是Vitis AI重要組成部分,所以我們將重點介紹Vitis HLS。LUT 或 SICELUT 或 SICE是構成了 FPGA 的區域。它的數量有限,當它用完時,意味著您的設計太大了!BRAM 或

2022-09-09 16:45:27

FPGA入門嵌入式塊RAM使用為FIOF(First In First Out)單時鐘FIOF、雙時鐘FIOF(普通雙時鐘和混合寬度雙時鐘)由于單時鐘FIOF只有一個時鐘信號,所以可以在FPGA內部中使用單時鐘FIOF用以其他模塊數據的緩存。...

2021-12-17 07:59:18

國外的融合技術專家展示了一項基于FPGA的數據采集系統,用于合成孔徑成像技術。采用了Xilinx ISE設計軟件,支持ARM AMBA AXI4接口。文風犀利,觀點新穎,FPGA中使用ARM及AMBA總線中不可多得的資料在賽靈思FPGA中使用ARM及AMBA總線[hide][/hide]

2012-03-01 15:48:17

FPGA的HLS案例開發|基于Kintex-7、Zynq-7045_7100開發板前 言本文主要介紹HLS案例的使用說明,適用開發環境:Windows 7/10 64bit、Xilinx

2021-02-19 18:36:48

你好xilinx用戶,我正在使用FPGA實現人工神經網絡。我想知道如何在FPGA中使用0.784,1.768..etc等數字。表示這些數字的方法是什么。以上來自于谷歌翻譯以下為原文hello

2019-03-04 13:38:31

美好的一天!我想知道如何在FPGA上有持久的價值,我的意思是當我修改它的值時,當塊再次運行時,值不會被改變?在Matlab中通過定義一個像:persistent u的值,它會完成,但VHDL怎么樣

2019-02-20 11:17:46

嗨,我是Xilinx FPGA的新手。我該如何在FPGA中實現實時時鐘或時間和日期計數器?Xilinx是否為Artix 7提供任何RTC核心或IP?非常感謝您的建議。

2020-05-22 12:41:35

大家好!我想知道如何在FPGA中使用VHDL實現過零檢測器。所以我想實現一個數字常數小數鑒別器。 firt部分提供了雙極性信號,但我想知道如何在vhdl中實現過零檢測器。感謝您的幫助!以上來自于谷歌

2019-01-29 08:16:40

大家好我正在嘗試在斯巴達6上開發UDP / IP堆棧。該FPGA將與外部PHY(DP83640)通信。我已經添加了TEMAC v4.4核心。所以我的問題是: - 如何在FPGA和PHY之間執行自動

2019-11-05 09:46:20

如何在FPGA應用程序中將固定點稱為重要的?以上來自于谷歌翻譯以下為原文How fixed point can be called important in FPGA Applications?

2019-02-18 13:24:43

]命令失敗:'E9'不是有效的站點或包引腳名稱。 [ “C:/lab/test/test.srcs/constrs_1/new/demo.xdc”:5]如何在FPGA設計中使用E9引腳來控制NOR閃存?謝謝。

2020-06-10 16:52:14

你好!正如我在標題中提出的那樣,希望大家可以討論如何在FPGA設計中測試數字IF信號功率。以上來自于谷歌翻譯以下為原文Hello! as what I put forward

2019-01-09 10:00:59

嗨? 如何在HLS 14.3中編寫pow功能? HLS 14.3不支持exp和pow功能。我在我的代碼中寫了“#include math.h”。但是,它不起作用。 另外,我想知道C代碼中

2019-03-05 13:40:09

在FPGA中,動態相位調整(DPA)主要是實現LVDS接口接收時對時鐘和數據通道的相位補償,以達到正確接收的目的。那么該如何在低端FPGA中實現DPA的功能呢?

2021-04-08 06:47:08

如何在視頻監控系統中使用FPGA進行視頻處理?

2021-06-07 06:12:39

有沒有人知道教程的一些鏈接,如何在設計套件中使用sumulink的指南?我希望找到一個簡單的101教程,它將引導我在Simulink中創建一個簡單的項目(包括Xilinx Sys gen工具箱組件

2019-03-21 16:42:18

如何使用NI LabVIEW FPGA來設計和自定義您的射頻儀器?軟件設計儀器為您的測試系統帶來了哪些好處?

2021-05-24 06:26:34

你好,我想使用Vivado HLS開發FPGA比特流并將其加載到Pynqpython模塊中或使用Linux使用C ++進行ARM加載。到目前為止,我能夠生成FPGA比特流文件,但是知道如何集成它或與Pynq通信。那有什么教程嗎?

2019-09-30 10:50:36

開拓者FPGA DEVB_121X160MM 6~24V

2023-03-28 13:06:25

相比,能夠為通信和多媒體應用提供高達10倍速的更高的設計和驗證能力。Synphony HLS為ASIC 和 FPGA的應用、架構和快速原型生成最優化的RTL。Synphony HLS解決方案架構圖

2019-08-13 08:21:49

您是否曾想在您的FPGA設計中使用先進的視頻壓縮技術,卻發現實現起來太過復雜?那么如何滿足視頻壓縮的需求?

2021-04-08 06:43:18

和生成比特流以對FPGA進行編程4 - 將比特流導入并阻塞到SDK中,基于此生成板級支持包(BSP)并與Zedboard連接。順便說一下,SDK的目標是成為我在Vivado HLS中的測試平臺嗎?即在計算機中觀察Zedboard產生的結果是否為例外情況。

2020-03-24 08:37:03

對大家有所幫助,當然更加希望Xilinx? FPGA工程師/愛好者能跟我們一起來探討學習!《成為Xilinx FPGA設計專家》這本電子書,計劃分為3大部分:基礎篇、提升篇、高級篇。 當然這里講

2014-11-05 13:56:42

設計專家》這本電子書,計劃分為3大部分:基礎篇、提升篇、高級篇。 當然這里講的就是《成為Xilinx FPGA設計專家》(基礎篇)。本電子書主要論述了等相關內容。本電子書旨在解決工程師日常設計中所

2014-11-03 17:15:51

新起點FPGA DEVB_90X128MM 6~24V

2023-03-28 13:06:25

的問題是:所有3種類型都可以在FPGA Spartan 6中使用,如果它們中的任何一種都有利于以更簡單的方式實現。謝謝您的幫助。

2019-08-05 07:38:33

您好我有一個關于vivado hls的問題。RTL是否來自xivix FPGA的vivado hls onyl?我們可以在Design Compiler上使用它進行綜合嗎?謝謝

2020-04-13 09:12:32

您好Xilinx的用戶和員工,我們正在考慮購買Zynq 7000用于機器視覺任務。我們沒有編程FPGA的經驗,并希望使用Vivado HLS來指導和加速我們的工作。關于這種方法的一些問題:您對

2020-03-25 09:04:39

概述EasyGo FPGA Coder Block是嵌入Matlab/Simulink里面的FPGA 仿真工具包軟件。提供了一些基礎的函數庫以及常用的控制函數模塊,配合

2022-05-19 09:16:05

概述EasyGo FPGA Solver是EasyGo開發的專門部署在FPGA 硬件上的解算器軟件。根據不同的應用需求,會有不同的FPGA Solver 選擇

2022-05-19 09:21:43

EP4CE10F17C8N,Cyclone IV FPGA設備,INTEL/ALTERAEP4CE10F17C8N,Cyclone IV FPGA設備,INTEL

2023-02-20 17:00:57

什么是FPGA?FPGA是什么意思,本內容詳加描述了FPGA的相關知識包括FPGA配置模式,PPGA特點及應用

2011-12-07 13:39:00 79099

79099 解決本本黑屏問題 專家教你DIY

問題:最近我的筆記本在以下情況下特別容易出現黑屏(不是純黑,屏上較亮的還以隱約看

2010-01-25 14:45:32 633

633 投影屏幕選購讓專家教你三招

1、不同應用選擇不同材質 表面上看,投影屏幕的外觀顏色都是白的,沒有什么差別,其實不同材質

2010-02-11 09:29:52 424

424 電子發燒友網核心提示 :在嵌入式系統中使用FPGA時會經常出現以下常見問題,如在嵌入式設計中,怎樣使用FPGA、在嵌入式設計中,怎樣采用FPGA進行設計來降低風險等。今天電子發燒友

2012-10-17 13:38:35 906

906 Introduction to FPGA Design with Vivado High-Level Synthesis,使用 Vivado 高層次綜合 (HLS) 進行 FPGA 設計的簡介

2016-01-06 11:32:55 65

65 介紹如何設計HLS IP,并且在IP Integrator中使用它來作一個設計——這里生成兩個HLS blocks的IP,并且在一個FFT(Xilinx IP)的設計中使用他們,最終使用RTL

2017-02-07 17:59:29 4179

4179

高層次綜合設計最常見的的使用就是為CPU創建一個加速器,將在CPU中執行的代碼移動到FPGA可編程邏輯去提高性能。本文展示了如何在Zynq AP SoC設計中使用HLS IP。 在Zynq器件

2017-02-07 18:08:11 3207

3207

通常基于傳統處理器的C是串行執行,本文介紹Xilinx Vivado-HLS基于FPGA與傳統處理器對C編譯比較,差別。對傳統軟件工程師看來C是串行執行,本文將有助于軟件工程師理解

2017-11-18 12:23:09 2377

2377

HLS,高層綜合)。這個工具直接使用C、C++或SystemC 開發的高層描述來綜合數字硬件,這樣就不再需要人工做出用于硬件的設計,像是VHDL 或Verilog 這樣的文件,而是由HLS 工具來做這個事情。

2018-06-04 01:43:00 7171

7171

Achronix的Speedcore系列eFPGA可得到Catapult HLS的全面支持。

Catapult HLS為FPGA流程提供集成化設計與開發環境,率先支持5G無線應用。

2018-08-30 10:09:32 7368

7368 中斷作為硬件與軟件握手和同步的手段而被廣泛使用,可用于表示硬件進程的完成或軟件執行過程中的請求。Gx3500 & GX3700/GX3700e 用戶可編程 FPGA 板卡都支持這一特性,并向 FPGA 設計者開放專用的硬件中斷引腳;軟件方面,三個 API 函數用于中斷管理和設置。

2018-08-31 08:00:00 10

10 作為集成電路設計領域現場可編程門陣列 (FPGA) 技術的創造者之一,賽靈思一直積極推廣高層次綜合 (HLS) 技術,通過這種能夠解讀所需行為的自動化設計流程打造出可實現此類行為的硬件。賽靈思剛剛推出了一本專著,清晰介紹了如何使用 HLS 技術來創建優化的硬件設計。

2018-11-10 11:01:05 2750

2750 亞馬遜網絡服務公司的Gadi Hutt于2018年1月9日在法蘭克福舉行了Xilinx開發者論壇的開幕主題演講.Gadi解釋了Amazon EC2 F1實例的基礎知識,如何在AWS云中加速Xilinx FPGA

2018-11-23 06:15:00 2524

2524 Xilinx FPGA是支持OpenStack的第一個(也是目前唯一的)FPGA。

該視頻快速介紹了如何在小型集群中部署Xilinx FPGA卡,以便在Xilinx SC16展臺上運行每個演示,并使用OpenStack進行配置和管理。

2018-11-23 06:14:00 3322

3322 了解如何在UltraScale +設計中包含新的UltraRAM模塊。

該視頻演示了如何在UltraScale + FPGA和MPSoC中使用UltraRAM,包括新的Xilinx參數化宏(XPM)工具。

2018-11-22 05:50:00 7646

7646 高層次的設計可以讓設計以更簡潔的方法捕捉,從而讓錯誤更少,調試更輕松。然而,這種方法最受詬病的是對性能的犧牲。在復雜的 FPGA 設計上實現高性能,往往需要手動優化 RTL 代碼,這也意味著

2018-12-16 11:19:28 1435

1435

用軟件從 C 轉化來的 RTL 代碼其實并不好理解。今天我們就來談談,如何在不改變 RTL 代碼的情況下,提升設計性能。 本項目所需應用與工具:賽靈思HLS、Plunify Cloud 以及 InTime。 前言 高層次的設計可以讓設計以更簡潔的方法捕捉,從而讓錯誤更少,調試更輕松。

2019-09-15 11:56:00 265

265 本文檔介紹如何在Spartan?6 FPGA中使用GTP收發器。?spartan-6 FPGA GTP收發器簡稱為GTP收發器。

?gtpa1_dual是實例化原語的名稱,它實例化一組

2019-02-15 14:42:47 27

27 展示了賽靈思 SDAccel 開發環境的運行情況,并演示了一個軟件程序員是如何在OpenCL中捕獲一個應用,并利用 FPGA 對其完成加速的。整個過程中該程序員完全不需要是一個FPGA專家或對賽靈思器件設計流程特別熟悉即可獨立完成。

2019-08-01 11:03:25 1528

1528 接著開始正文。據觀察,HLS的發展呈現愈演愈烈的趨勢,隨著Xilinx Vivado HLS的推出,intel也快馬加鞭的推出了其HLS工具。HLS可以在一定程度上降低FPGA的入門門檻(不用編寫

2019-07-31 09:45:17 6232

6232

在本教程中,我們將來聊一聊有關如何在 Vitis HLS 中使用 AXI4-Lite 接口創建定制 IP 的基礎知識。

2020-09-13 10:04:19 5961

5961

一:fifo是什么 FIFO的完整英文拼寫為FirstIn First Out,即先進先出。FPGA或者ASIC中使用到的FIFO一般指的是對數據的存儲具有先進先出特性的一個存儲器,常被用于數據

2021-03-12 16:30:48 2796

2796

FPGA的布局布線軟件向來跑得很慢。事實上,FPGA供應商已經花了很大的精力使其設計軟件在多核處理器上運行得更快。

2022-05-25 09:50:10 959

959 需要門級驗證:FPGA 和 ASIC 一樣需要設計級驗證。但是,FPGA 在門級不是細粒度的,因此它們不需要門級驗證。您將每個門都放置在 ASIC 設計中,因此您需要驗證每個門。

2022-06-20 16:13:05 2184

2184

您是否想創建自己帶有 AXI4-Lite 接口的 IP 卻感覺無從著手?本文將為您講解有關如何在 Vitis HLS 中使用 C 語言代碼創建 AXI4-Lite 接口的基礎知識。

2022-07-08 09:40:43 1232

1232 HLS的FPGA開發方法是只抽象出可以在C/C++環境中輕松表達的應用部分。通過使用Vivado(Xilinx)或Intel(Quartus)工具,HLS工具流程基本上可用于任何BittWare板。

2022-08-02 09:18:32 1340

1340

以供在 Vivado Design Suite 中使用、如何將其連接到其它 IP 核與處理器以及如何在板上運行工程。

2022-08-02 09:43:05 579

579

電子發燒友網站提供《ThunderGP:基于HLS的FPGA圖形處理框架.zip》資料免費下載

2022-10-27 16:49:59 0

0 電子發燒友網站提供《如何在Arduino中使用LDR.zip》資料免費下載

2022-10-31 09:50:41 0

0 1、HLS簡介 HLS(High-Level Synthesis)高層綜合,就是將 C/C++的功能用 RTL 來實現,將 FPGA 的組件在一個軟件環境中來開發,這個模塊的功能驗證在軟件環境

2022-12-02 12:30:02 2571

2571 HLS ?(high-level synthesis)稱為高級綜合, 它的主要功能是用 C/C++為 FPGA開發 算法。這將提升FPGA 算法開發的生產力。 ?? Xilinx 最新的HLS

2023-01-15 12:10:04 2968

2968 電子發燒友網站提供《如何使用HLS加速FPGA上的FIR濾波器.zip》資料免費下載

2023-06-14 15:28:49 1

1 FPGA IP核(Intellectual Property core)是指在可編程邏輯器件(Field-Programmable Gate Array,FPGA)中使用的可復用的設計模塊或功能片段。它們是預先編寫好的硬件設計代碼,可以在FPGA芯片上實現特定的功能。

2023-07-03 17:13:28 4100

4100 本篇博文旨在演示如何在 Zynq 設計中使用 Vitis 視覺庫函數 (remap) 作為 HLS IP,然后在 Vitis 中使用該函數作為平臺來運行嵌入式應用。

2023-08-01 10:18:08 307

307

本篇博客介紹 VVAS 框架所支持調用的 H/W(HLS) 內核。 H/W 內核指的是使用 HLS 工具生成的在 FPGA 部分執行的硬件功能模塊。

2023-08-04 11:00:43 335

335

Vitis? HLS 2023.1 支持新的 L1 庫向導,本文將講解如何下載 L1 庫、查看所有可用功能以及如何在 Vitis HLS GUI 中使用庫函數。

2023-08-16 10:26:16 546

546

電子發燒友網站提供《使用Vivado高層次綜合(HLS)進行FPGA設計的簡介.pdf》資料免費下載

2023-11-16 09:33:36 0

0 Dimitar Panayotov 在 2023 年 QA Challenge Accepted 大會 上分享了他如何在測試中使用 ChatGPT。

2024-02-20 13:57:01 280

280

電子發燒友App

電子發燒友App

評論