前言shineblink core 開發板(簡稱Core)的庫函數支持TF卡讀寫功能,所以只需要調用兩三個API,即可實現TF卡的操作。PS:Core 僅用五、六行代碼即可實現Wifi/Ble/NB

2022-02-09 08:04:24

, I have this basic doubt that why at all HDL coder is there in Matlab when we have system generator

2018-12-18 10:40:58

你好: 我是一個購買的帳戶,所以我的許可證應該允許訪問所有內容。但是當我使用System Generator for DSP時,系統說我的SysGen簽出許可證失敗了。有人知道怎么解決嗎?謝謝

2019-01-28 07:16:36

FPGA中的數字控制器是什么?System Generator中的PID控制器是如何設計的?

2021-04-08 06:51:46

大家好,這是我第一次使用System Generator工具,如果有人能夠解決一個不讓我繼續參與我的硬件協同仿真項目的問題,我想。我正在使用Matlab R2013b,Xilinx ISE 14.7

2020-03-23 06:53:11

根據我的理解,System Generator是MatLab到RTL的轉換,因此不包括Vivado的優化過程。問題1--是真的。確實,Vivado中的優化將大大改變系統描述,而系統描述不會向后兼容

2019-04-25 12:47:45

HI,我正在使用System Generator 2014.4 30天評估包,Matalb 2014B。簡單地說我想使用FIR編譯器,當我嘗試編輯它的參數時,我得到了兩個錯誤: - 1.“來自MEX

2020-03-24 09:01:59

要做一個將hex文件轉化成bin 文件的labview,結果發現不少按一行一行處理的,而是將所有字符串當成一行來處理的,就是假如有5行二十個字符的,要去掉每一行的前八個字符 和最后兩個字符,中間剩下

2015-06-30 14:24:07

,終于找到了一個厲害的武器,不用寫一行程序,也不需要在數據庫中搞這搞那,就可以完成這些查詢。 我找到的,是一個國內經典的老牌網站管理系統,就是CMS了,當然,也不是所有的CMS都能作這個工作,我看了

2012-02-09 17:11:44

=entiresite&q=Xilinx+System+Generator+就這一片還有點價值,但是怎么連接,matlab官網上說xilinx DSPsystem generator

2013-10-05 11:59:34

USE和System Generator何時才能勝任64位Windows 7?以上來自于谷歌翻譯以下為原文When will ISE and System Generator be qualified for 64 bit Windows 7?

2018-11-26 15:05:56

想請教一下在LabView中怎么讀取一個txt,然后把其中一行給刪除。是刪除txt的內容 而不是刪除整個txt。謝謝

2015-05-18 15:34:21

`Labview 怎么用報表生成函數 一行一行自動換行寫表格Excel`

2017-11-21 13:37:29

最近在搞system generator仿真,發現getway in這個模塊參數設置變化導致MATLAB閃退問題,貼圖如下其中getway in 這個模塊數據類型換成定點有符號或者無符號數都不得行,換成布爾值又會出現錯誤,不知為何啊!求教。

2018-01-05 21:43:53

用的RXT操作系統,每一個任務都能創建,可是在執行每一個任務的過程中,每一個任務都只能執行兩行或者是一行的代碼,之后的代碼都不能被執行了,像是程序死在了一個地方的感覺一樣,導致所有的任務都不能執行

2019-10-21 21:46:53

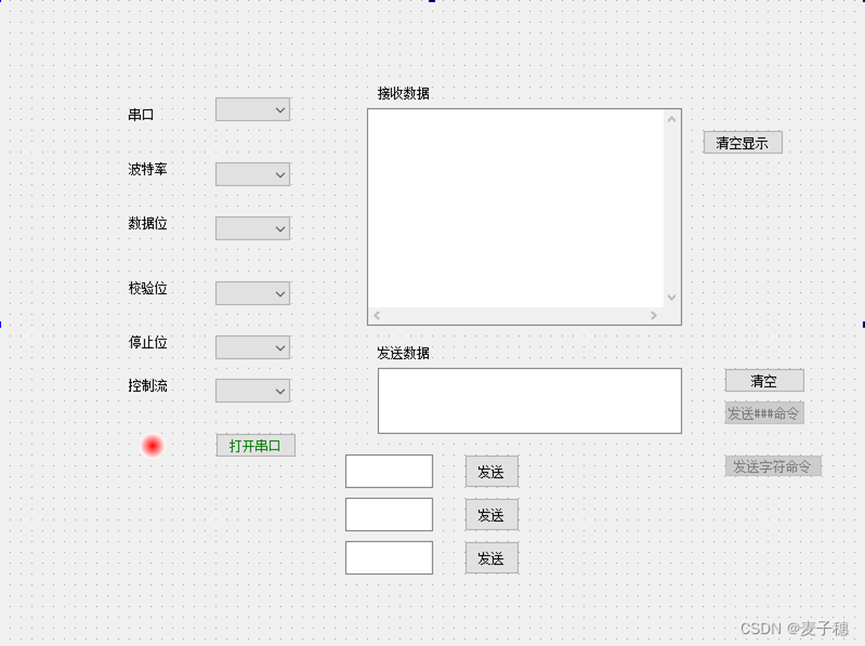

在開始學寫STM32串口通信的代碼實現前,首先先了解一下兩塊芯片之間通信的分類,按照數據傳輸方式可以分為并行通信:數據各個位同時傳輸,速度快,占用引腳資源多串行通信:數據按位傳輸,速度較慢,占用引腳

2021-11-26 07:24:14

翻譯成verilog,在FPGA里面實現,即system generator。altera有沒有類似的接口,與matlab可以互連,直接在matlab里設計我所需要的算法,在翻譯成verilog?

2015-01-14 14:20:50

各位大佬好,我想要將一個二維數組中的所有上一行值一直傳遞給下一行,第一行隨機產生新值,除了列舉法還有什么較為編輯的方法嗎?比如說布爾數組燈中第一次,第一行隨機一個燈(假設為x)亮了,第二次第二行

2020-08-08 19:16:04

() 函數配置系統時鐘,在舊版本的工程中要用戶進入main函數自己調用SystemIni() 函數。

那么使用stm32時是不是啟動代碼都不用改啊?

STM32時鐘有幾種,怎么分配?

2018-09-24 09:13:35

與上位機的串口通信是一個很常用的程序。碧海藍天在剛剛接觸stm32芯片時寫的第一個簡單程序就是串口通信,現在把程序代碼甩出來與大家分享。完整的程序哦~一般人我不告訴他庫版本:ST3.0.0文件

2022-02-22 07:26:13

請寫一段HDL 代碼實現對輸入時鐘三分頻的功能(要求輸出時鐘占空比為50%)[code]module even_division(clk,rst,count1,count2,clk_even

2012-03-15 10:05:52

串口通信時用jlink調試,單步運行能得到第一行的正確結果。但全速運行就成了第二行那樣了

2019-07-10 05:45:22

的水平只是有個基礎,想進FPGA這一行,投了很多簡歷,大部分都是要工作經驗的,面試的機會都不給。感覺進這行好難呀。

2013-03-14 23:40:46

各位好,最近在使用system generator 搭建一個ifft設計模塊,使用ise調用,但是在下載到板子后,示波器輸出波形去在沒有輸入的情況下仍然有波形,確定不是噪聲,波形還是很規律,求解釋呀!

2016-07-13 13:21:30

使用system generator導入xilinx模塊時,只要連線兩個模塊,matlab就崩潰,有知道原因的大佬嗎?

2018-01-19 17:54:57

利用stm32的串口進行數據接收中間總會出現完整的一行無發記錄是為什么?

2021-12-09 06:23:09

simulink我意識到研討會列出了Matlab2012a。我安裝了Matlab R2016b和Matlab R2017a。哪一個與Xilinx System Generator兼容?我是否需要刪除所有工具

2018-12-27 10:55:34

大家好,我正在使用具有Virtex-4 FX100的定制板。在內部,有一個基于VHDL的框架,它將定制板上的不同部分與“DSP內核”連接,后者是在System Generator下開發的。在這

2019-01-15 10:39:11

有做System Generator處理圖像的嗎?遇到一些問題,一起商量下

2020-09-28 19:04:58

、基于模型設計的HDL代碼自動生成技術應用需求近年來,現場可編程門陣列(FPGA)被廣泛應用于航空航天、汽車、通信、工業自動化、電機控制、醫學成像等嵌入式應用領域。傳統的FPGA上的數字設計實現依賴于

2021-06-08 09:29:26

嗨,大家好,我們都知道系統genreator可以生成硬件語言(verliog和VHDL)。但我的問題是:與專業的HDL程序員相比,如何更好地了解系統生成器生成的這些代碼,哪一個更有效?問候瑞安以上

2019-02-20 10:25:40

嗨,我正在嘗試學習如何使用System Generator來創建自己的IP核。首先,我在DocNav中找到了一個ug948-vivado-sysgen-tutorial文檔。我在哪里可以找到本文檔中描述的示例?我在安裝目錄中的“examples”文件夾中找不到完全相同的示例。提前致謝馬丁

2020-05-22 07:22:09

右鍵某一行,根據坐標選中這一行

2016-05-04 23:08:35

大家好!我現在實現了點擊按鈕在表格添加一行數據,如何通過點擊另外一個按鈕,刪除表格中一行

2012-09-30 11:40:18

顯示出數據)疑問:如果采用串口中斷方式,中斷服務函數該怎么寫?我不明白的是:接收到數據后,RI=1,此時單片機進入中斷函數,當發送完數據之后,單片機是不是也進入中斷函數?新手求解另外,下圖中program size 這一行的提示是什么意思?

2015-07-05 17:01:13

各位大佬,我在安裝System Generator時,跟著教程走,發現在vivado中沒有出現System Generator for DSP這個選項,請問是我哪里安裝得不對嗎?

2023-09-26 21:54:58

當我完成SDx 2017.2的安裝時,沒有安裝System Generator的選項。我正在運行從Xilinx下載的安裝程序:https://www.xilinx.com/member/forms

2019-01-07 10:59:00

你好,我叫Joaquín。有人知道,我可以在Matlab / Simulink中使用System Generator創建一個雙向(inout)端口。我正在嘗試為Xilinx的外部存儲器創建一個接口

2019-05-09 14:36:24

最近在使用system generator設計一個rs編碼譯碼的模型,總的思想是在rs編碼產生信號后,插入一個誤碼,然后作為信號源進行解碼,看是否能夠正常的進行解碼,求解是怎么才能把rs編碼后的信號存儲起來作為信號源

2016-07-20 20:13:59

System Generator for DSP的特點是什么?如何使用System Generator for DSP實現系統級建模?怎么在Matlab中實現數字通信FPGA硬件設計?

2021-04-29 06:20:46

目前我做到。把數據一行一行輸入,用添加表格到excel的控件,但是每一次寫入,上一次的數據就沒了。怎么樣實時向excel填入數據,一行一行的填滿。?

2017-12-21 11:52:28

*1000)%1000);理想狀態應該一行一行比較緊湊才對我不知道為啥換了串口助手后會多一個空行,求解釋和解決問題

2022-06-17 09:25:26

各位好:最近遇到一個比較煩的問題。我現在在txt里面存了比較多的數據,大概200M。每一行數據不多但是行數比較多,現在我想讀取最后一行數據,而且還不能把文件全部讀取出來,那樣非常占用內存。大伙有沒有比較好的辦法解決?每一行的數據長度都不一樣

2019-08-05 11:17:11

/STM32F469xx and STM32F479xx devices. This parameter must be a number between Min_Data = 2 and Max_Data = 7*/#endif//正文第一行最后有個"\"是什么意思?去掉之后編譯就會出錯。

2020-03-30 04:35:49

我想從數組中取出非零元素的下標/位置,可是我寫的程序只能取出每一行第一個非零元素的下標,每一行第二個及以后的元素坐標就直接跳過了,緊接著就顯示下一行第一個非零元素的位置了。我寫的圖已經上傳

2019-08-29 19:32:39

`程序員改了一行代碼后...`

2016-04-29 10:36:39

第一行代碼 Android 第2版 郭霖 人郵 2016.12 高清版-2016.12-P580

2018-02-01 11:27:30

第一行代碼Android第2版-郭霖

2020-04-03 12:08:33

如圖,在圖一中把“壓力1”“壓力2”都設為默認值,關掉vi再次打開的時候第一行 第二行都變成了“壓力2”如圖2怎么回事?想要的效果是第一行 第二行 都有自己的默認值,每次打開vi的時候都不需要重新輸入

2017-09-11 15:35:13

必須為整數,也就是說1秒鐘只能顯示1000行數據,我想在一秒鐘在一個一維數組中顯示采集數據的每一行,請問該如何實現

2018-08-13 11:27:39

請問怎么依次發送這個二維數組的第一行第二行,之后跳轉回來再發送第一行 第二行

2017-12-25 19:59:38

使用multiedit后用了MULTIEDIT_SetWrapWord(hItem)這個只是整字換行請問怎樣能實現在一行顯示指定數量的字符后換到下一行?怎樣換行

2019-08-06 21:47:48

請問斷點所在的那一行代碼是否已經執行?

2019-11-11 04:35:48

兄弟們,請問火車站那種顯示當前將要到站列車的LED屏,一行一行往上滾,怎么實現 ??

2020-05-27 05:55:11

請問,我想把字體按規定顯示成我想要的顏色,但是只能是一行顯示,倒下一行來了上一行的顏色又變回很色了,怎么保持顏色?我是新手,請大佬們給指點一下,謝謝!

2019-01-21 14:33:15

采用Gardner算法,對QPSK調制解調系統中的位同步系統進行設計與實現,大大提高了系統性能和資源利用率。重點闡述采用FPGA開發環境System Generator系統設計工具進行位同

2010-07-21 16:12:40 26

26 深入了解賽靈思System Generator中的時間參數

基于模型的設計(MBD)因其在縮小實時系統抽象的數學建模和物理實現之間差距方面的光明前景而備受關注。通過使用相同的

2009-12-29 11:40:30 1300

1300

HDL設計和驗證與System Generator相結合

Xilinx®SystemGeneratoRForDSP是用來協助系統設計的MATLABSimulink模塊集。SystemGeneratorforDSP在熟悉的MATLAB環境中引入XilinxFPGA對象,讓您能夠

2010-01-06 14:39:30 1181

1181

51單片機與串口通信的代碼設計

2011-11-09 17:47:28 172

172 Xilinx公司推出的DSP設計開發工具System Generator是在Matlab環境中進行建模,是DSP高層系統設計與Xilinx FPGA之間實現的橋梁。在分析了FPGA傳統級設計方法的基礎上,提出了基于System Generator的

2013-01-10 16:51:24 58

58 Xilinx FPGA工程例子源碼:System Generator的設計實例

2016-06-07 14:41:57 22

22 環境 ?Matlab 2014 a ?Vivado 2014.4 ?System generator 2014.4 實現步驟 1、模型搭建與仿真 在simulink環境下工程搭建如下 圖3 四路加

2017-02-08 01:10:08 473

473

最新版System Generator支持快速開發和實現基于All Programmable FPGA、SoC和MPSoC的無線電設計 賽靈思日前宣布推出高級設計工具System Generator

2017-02-09 01:23:41 279

279 前一陣一直在忙,所以沒有來得及寫博文。弄完雜七雜八的事情,又繼續FPGA的研究。使用Verilog HDL語言和原理圖輸入來完成FPGA設計的方法都試驗過了,更高級的還有基于System Generator和基于EDK/Microblaze的方法。

2017-02-11 03:10:11 8192

8192

System Generator是Xilinx公司進行數字信號處理開發的一種設計工具,它通過將Xilinx開發的一些模塊嵌入到Simulink的庫中,可以在Simulink中進行定點仿真,可是設置

2017-02-11 11:53:11 3778

3778

system generator是xilinx公司的系統級建模工具,它是擴展mathworks公司的MATLAB下面的simulink平臺,添加了XILINX FPGA專用的一些模塊。加速簡化了FPGA的DSP系統級硬件設計。

2017-02-11 19:21:33 7386

7386

基于FPGA Verilog-HDL語言的串口設計

2017-02-16 00:08:59 35

35 第一行代碼——Android

2017-03-19 11:24:33 0

0 現在的FPGA算法的實現有下面幾種方法: 1. Verilog/VHDL 語言的開發 ; 2. system Generator; 3. ImpulsC 編譯器實現從 C代碼到 HDL 語言; 4.

2017-11-17 14:29:06 7298

7298 在FPGA平臺上應用System Generator工具實現了高精度頻率估計Rife算法。不同于傳統的基于HDL代碼和IP核的設計方法,采用System Generator工具可以使復雜算法

2017-11-18 09:01:51 2208

2208

Xilinx System Generator 是專門為數字信號算法處理而推出的模型化設計平臺,可以快速、簡單地將DSP系統的抽象算法轉換成可綜合的、可靠的硬件系統,彌補了大部分對C語言以及Matlab工具很熟悉的DSP工程師對于硬件描述語言VHDL和Verilog HDL認識不足的缺陷。

2018-07-19 09:32:00 3716

3716

了解如何將Vivado HLS設計作為IP模塊整合到System Generator for DSP中。

了解如何將Vivado HLS設計保存為IP模塊,并了解如何將此IP輕松整合到System Generator for DSP的設計中。

2018-11-20 05:55:00 2940

2940 了解如何在System Generator中使用多個時鐘域,從而可以實現復雜的DSP系統。

2018-11-27 06:42:00 3450

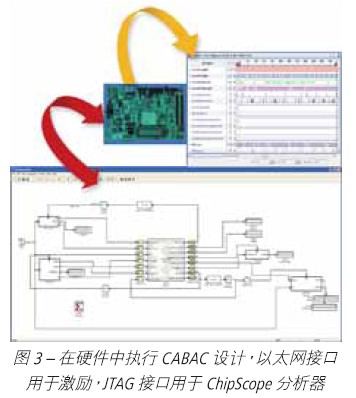

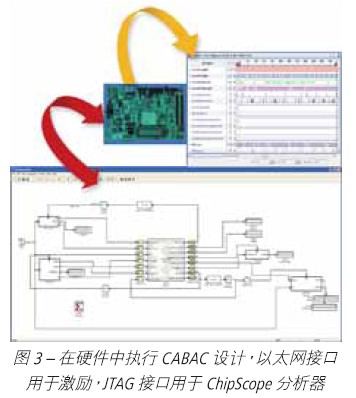

3450 了解如何使用Vivado System Generator for DSP進行點對點以太網硬件協同仿真。

System Generator提供硬件協同仿真,可以將FPGA中運行的設計直接整合到Simulink仿真中。

2018-11-23 06:02:00 4262

4262 本文檔的主要內容詳細介紹的是STC單片機實現串口通信的源代碼免費下載。

2020-06-17 17:32:15 38

38 看了很多串口通信,應該是配置問題很多代碼燒進去都不對,或者沒有反應。代碼控制輸入,串口輸出區輸出自己想要的數據,下面直接上代碼:(代碼親測有效)/*************************************************************************************** 串口通信實驗 *...

2021-11-11 21:06:00 26

26 本篇博文是面向希望學習 Xilinx System Generator for DSP 入門知識的新手的系列博文第一講。其中提供了有關執行下列操作的分步操作方法指南。

2022-02-16 16:21:36 1578

1578

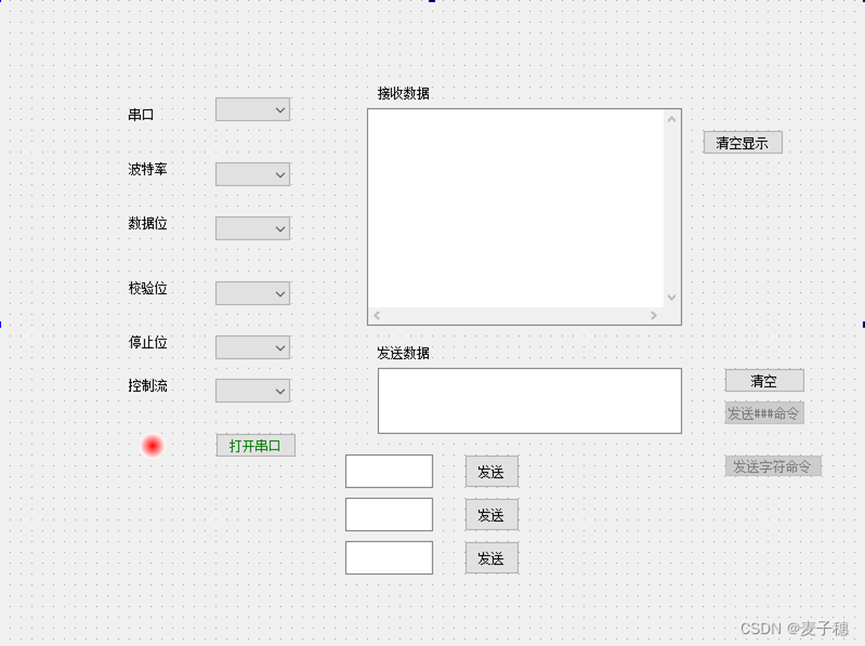

要實現串口通信,需要知道串口通信需要的信息

2023-04-23 17:34:11 3134

3134

正在加载...

電子發燒友App

電子發燒友App

評論