DDR31.DDR3概述DDR3內存控制器主要用于以JESD79-3C標準做SDRAM設備的外部存儲接口。支持的內存類型有DDR1 SDRAM,SDRSDRAM, SBSRAM。DDR3內存控制器

2018-01-18 22:04:33

嗨,我是FPGA領域的新手。現在我正在使用Genesys2。我必須控制DDR3內存。我在Digilent網站上找到了一些使用micrlaze處理器的DDR3示例。但是,在我的情況下,我不必

2019-05-05 15:29:38

江山科技最新推出JS-9500內存測試儀(SD/DDR/DDR2/DDR3)為領先業界的軟硬件測試系統,采用國際內存業界最先進自動儲存器測試程序,能快速、準確檢測內存條, 內存

2009-02-10 22:50:27

江山科技最新推出JS-9500內存測試儀(SD/DDR/DDR2/DDR3)為領先業界的軟硬件測試系統,采用國際內存業界最先進自動儲存器測試程序,能快速、準確檢測內存條, 內存

2009-02-10 22:55:45

江山科技最新推出JS-9500內存測試儀(SD/DDR/DDR2/DDR3)為領先業界的軟硬件測試系統,采用國際內存業界最先進自動儲存器測試程序,能快速、準確檢測內存條,筆記本

2009-08-17 23:00:19

DDR3(double-data-rate three synchronous dynamic random accessmemory)是應用在計算機及電子產品領域的一種高帶寬并行數據總線。DDR3 在 DDR2

2019-05-22 08:36:26

。為了充分利用和發揮DDR3存儲器的優點,使用一個高效且易于使用的DDR3存儲器接口控制器是非常重要的。視屏處理應用就是一個很好的示例,說明了DDR3存儲器系統的主要需求以及在類似數據流處理系統中

2019-05-24 05:00:34

DDR3存儲器接口控制器是什么?有什么優勢?

2021-04-30 06:57:16

XILINX MIG(DDR3) IP的AXI接口與APP接口的區別以及優缺點對比

2021-11-24 21:47:04

Achieving High Performance DDR3 Data Rates in Virtex-7 and Kintex-7 FPGAs。Xilinx官方DDR3資料。

2016-05-27 16:39:58

4的JEDEC標準DDR4接口的變體,它包含了對完整系統支持所需的獨特功能。本文將幫助工程師了解Xilinx FPGA控制器的Everspin STT-DDR4設計指南

2021-01-15 06:08:20

modelsim仿真DDR3時,出現下面錯誤。Instantiation of 'B_MCB' failed. The design unit was not found.并沒有用ISE聯合仿真

2016-01-21 10:12:40

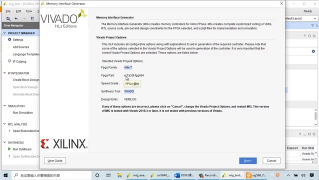

”。13.點擊“Generate”生成MIG控制器。四、生成文檔點擊“Generate”,生成MIG控制器相關的設計文檔。以上就是基于Xilinx 的K7 DDR3 IP核的生成配置過程。

2019-12-19 14:36:01

看完保證你會做DDR3的仿真

2015-09-18 14:33:11

xilinx平臺DDR3設計教程之仿真篇

2020-03-12 08:54:20

xilinx平臺DDR3設計教程之設計篇_中文版教程3

2023-08-05 18:39:58

“你能不能實現一個理想情況下應該在每個時間片開始時執行的監控任務,并確定前一個時間片的利用率。如果利用率過高,則應發出警告。如果我們可以使用空閑時間,那么我們就可以衡量利用率。為了設置這個監視器

2022-12-06 06:00:31

要計算當前CUP利用率,是不是就使能OS_TASK_STAT_EN就可以了,并不要單獨建立一個任務去執行OSTaskStat(),是這樣嗎?參看戰艦例程,沒有找到哪里執行了OSTaskStat()!

2020-05-18 22:05:37

(flight-time skew)來降低共同切換噪聲(SSN)。走線擺率可以達到0.8tCK,這個寬度導致無法確定在哪兩個時鐘周期獲取數據,因此,JEDEC為DDR3定義了校準功能,它可以使控制器

2019-04-22 07:00:08

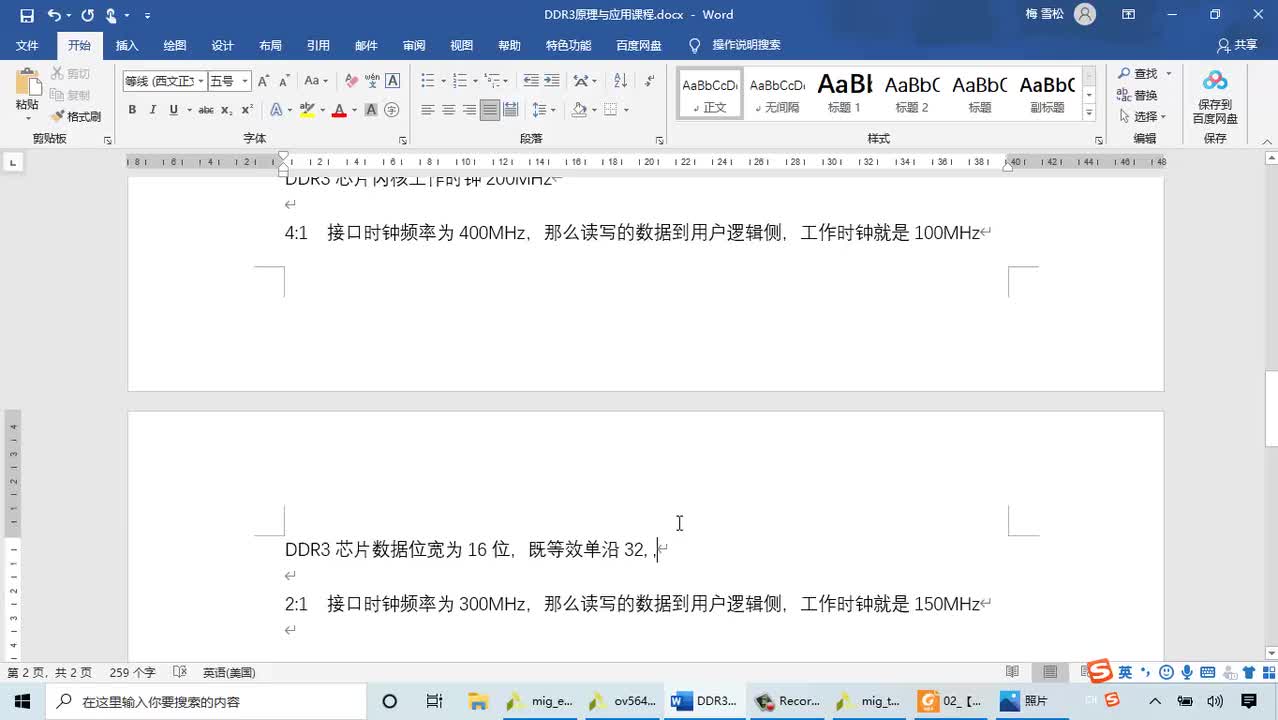

DDR3的理論帶寬怎么計算?用xilinx的控制器輸入時鐘200M。fpga與DDR的接口如下:

2016-02-17 18:17:40

嗨,Post綜合后的利用率只不過是實施后的利用率......?謝謝娜文G K.

2020-05-12 08:57:23

空閑線程中做運算,即利用率視為0%影響計算精度的問題:調度鎖只把調度器關了,中斷依然可以正常搶占,如systick會1ms打斷一次,如果一個線程執行時間超過1ms,則會被systick打斷,那么本次計算

2022-05-13 15:27:45

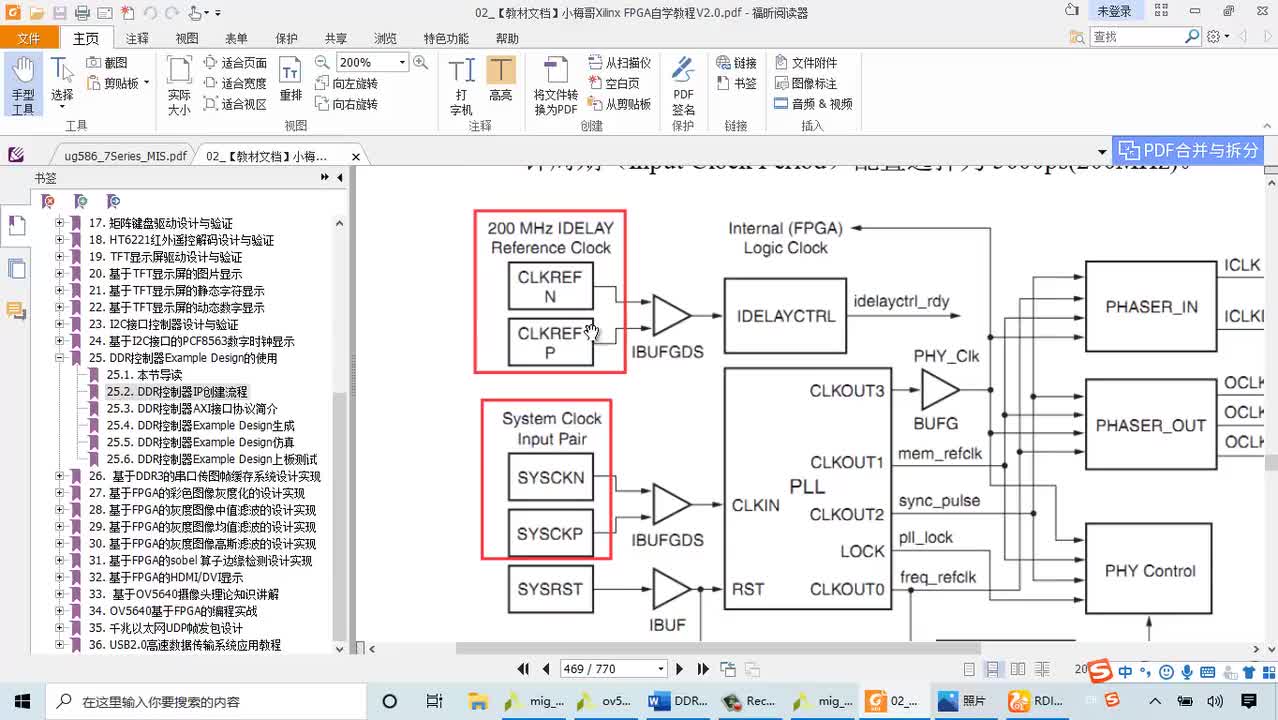

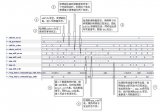

6655時鐘PLL配置與DDR3的配置1 時鐘概述PLL與PLL控制器的邏輯組成和處理流程如圖1所示。PLL控制器能夠通過PLLDIV1到PLLDIV16這些分頻器靈活便利的配置和修改內部的時鐘信號

2018-01-24 21:27:10

整機功耗過高風險,需實時監測功耗變化,進行針對性的功耗壓制。L3/MB 控制:當前底層硬件提供了 L3 緩存和內存帶寬隔離能力,但仍需軟件動態控制,以實現干擾控制和資源利用率的平衡。「資源隔離

2022-07-06 09:54:19

你好,我使用的是Vc707板,14.5 ISE DS。在XPS項目的開發過程中,我遇到了ddr3內存接口的問題。在我的XPS設計中(基于Xilinx網站上提供的參考vc707 BIST項目)軟件

2019-09-09 10:20:26

你好。我最近第一次對待Vivado。我想使用DDR3內存和IDELAYE2。該設備是Kintex-7。當我一起使用DDR3控制器和IDELAYE2時發生錯誤,并且無法形成位文件。當我丟失

2020-08-20 09:40:23

& 14用于DDR3內存接口,但由于我使用的是3.3V的fash存儲器IC,我必須使用bank 14進行閃存存儲器接口。原因是需要的資源僅在Bank 14中可用.DDR3存儲器連接的bank應該工作在

2020-04-17 07:54:29

的。DDR3控制器調用Write leveling功能時,需要DDR3 SDRAM顆粒的反饋來調整DQS與CK之間的相位關系,具體方式如下圖一所示。Write leveling 是一個完全自動的過程。控制器

2022-12-16 17:01:46

。為了充分利用和發揮DDR3存儲器的優點,使用一個高效且易于使用的DDR3存儲器接口控制器是非常重要的。視屏處理應用就是一個很好的示例,說明了DDR3存儲器系統的主要需求以及在類似數據流處理系統中

2019-05-27 05:00:02

進行了DDR3 SDRAM控制器的編寫,分析并提出了提高帶寬利用率的方法。最終將其進行類FIFO接口的封裝,屏蔽掉了DDR3 IP核復雜的用戶接口,為DDR3數據流緩存的實現提供便利。系統測試表明,該

2018-08-02 09:34:58

設計,簡化了DDR3多通道讀寫的復雜度,隨著有效數據周期的提升,最高端口速率可達5.0 GB/s以上,帶寬利用率可達80%以上。1 總體設計架構本文所設計的六通道讀寫防沖突總體架構如圖1所示,主要包括通道判

2018-08-02 09:32:45

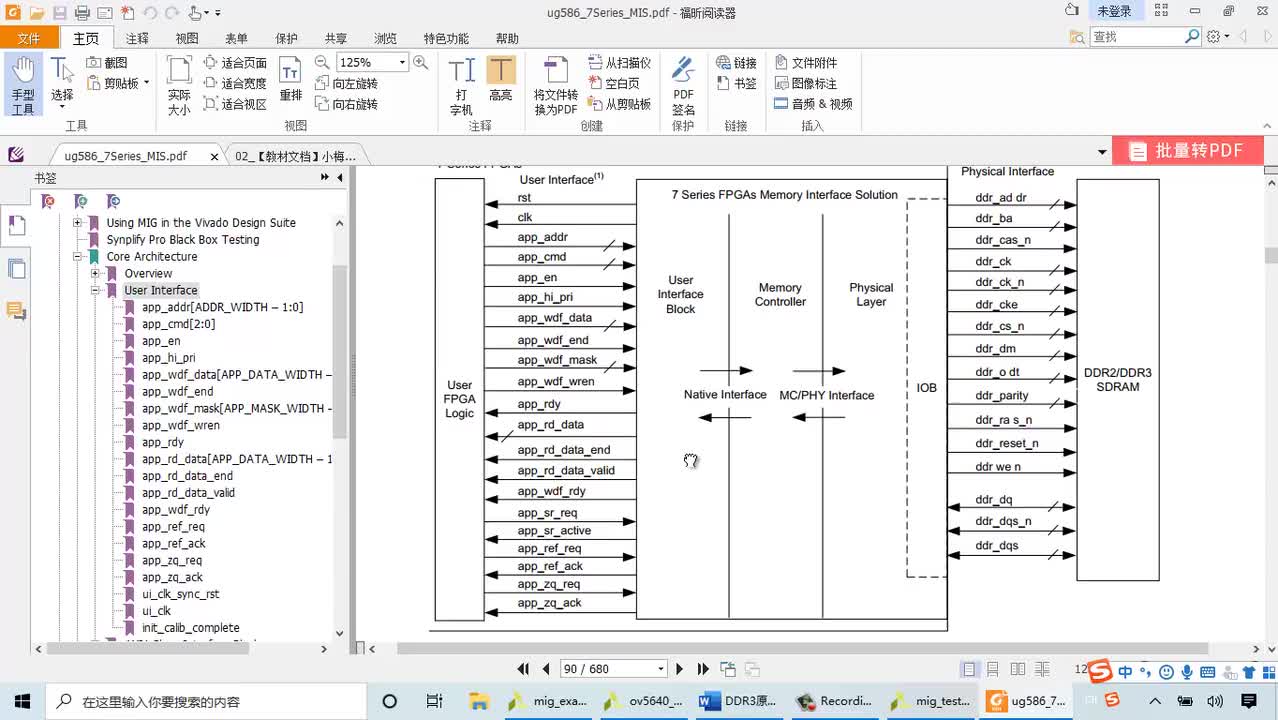

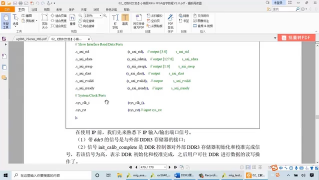

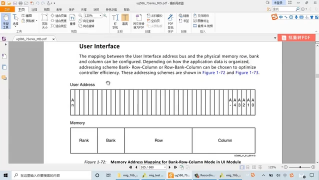

1 DDR3存儲管理系統設計框圖DDR3存儲器控制模塊采用Xilinx公司的MIG[4](Memory Interface Generator)方案,通過用戶接口建立FPGA內部控制邏輯到DDR3

2018-08-02 11:23:24

12位,擴展成16位后進行存儲,DDR3內部以1067M處理速度,32位的處理帶寬進行存儲,寫數據時從地址全0寫到地址全1,讀數據時也從地址全0讀到全1,經對比無誤,說明該控制器能夠較好地進行高速讀寫操作。`

2018-08-30 09:59:01

冒昧的問一下各路大神,假如我們利用UCOSII中的統計任務 OS_TaskStat()知道了CPU利用率100%,則應該怎樣操作,把利用率降下來?另外,利用率太高的話會不會不太好?

2019-07-12 04:36:16

DDR3存儲器控制器面臨的挑戰有哪些?如何用一個特定的FPGA系列LatticeECP3實現DDR3存儲器控制器。

2021-04-30 07:26:55

,ddr3的帶寬利用率也只有20%-30%左右。這里就覺得比較糾結。burst length太大,frame buffer的輸出端當要對輸入的視頻幀進行截取一部分的時候會變相降低DDR3帶寬利用率,這樣

2015-08-27 14:47:57

的工作時鐘頻率。然而,設計至DDR3的接口也變得更具挑戰性。在FPGA中實現高速、高效率的DDR3控制器是一項艱巨的任務。直到最近,只有少數高端(昂貴)的FPGA有支持與高速的DDR3存儲器可靠接口的塊

2019-08-09 07:42:01

嗨,我已將Xilinx CDMA(中央DMA控制器)連接到EDK項目。現在我需要使用SDK中的C程序來測試它。我的項目中有DDR3和BRAM。如何編寫C程序通過CDMA將DDR3數據寫入BRAM

2019-02-18 09:57:56

如何獲取棧利用率?

2022-02-16 07:34:32

旁邊的數字意味著什么的文檔和資源的指針?具體來說:1)它們各自意味著什么?,2)它們是在VHDL代碼中明確使用的,還是選擇了ISE(例如DSP48的數量)來實現我的設計?3)如果我的設計在上面100%的資源利用率,如何更改我的VHDL代碼以依次減少每個資源的使用?謝謝!

2020-03-24 10:14:15

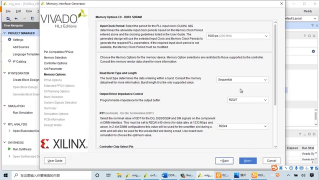

大家好,我試圖通過vivado v14.3生成DDR3控制器。我正在選擇DDR3 SODIMM模塊“MT8KSF1G72HZ-1G6”。該工具支持該器件,最高頻率可達666.66MHz,但該模塊的數據表明最高頻率可達800MHz。請幫我確定問題所在。感謝致敬Tarang JIndal

2020-07-31 06:07:43

你好我們計劃使用XC7Z020 PS部分的DDR3內置控制器將其連接到2個芯片[MT41K128M16] -32位數據寬度。我們計劃再使用一個DDR3組件來支持ECC。請告知我們XC7Z020 PS中DDR3控制器引腳的詳細信息,包括ECC引腳詳細信息。謝謝Pench

2020-03-24 09:34:32

嗨,大家好,我遇到了Xilinx ISE映射過程的棘手問題。當我綜合我的設計時,我得到了一些FPGA資源的利用。雖然在映射過程中映射到FPGA上的LUT時,所有利用率都會達到0%。他很可能是由于

2020-06-13 09:57:50

目前有一個項目需要使用DDR3作為顯示緩存,VGA作為顯示器,FPGA作為主控器,來刷圖片到VGA上。VGA部分已經完成,唯獨這個DDR3以前沒有使用過,時序又比較復雜,所以短時間內難以完成,希望做過DDR3控制器的大神指點一二。急求!!!!

2015-11-16 09:18:59

影響無線信道利用率的因素有哪些?無線利用率與網絡質量間的關系是什么?調整和提高無線信道利用率的建議有哪些?

2021-05-27 06:46:55

本文介紹了DDR3 SDRAM 的基本特點和主要操作時序,給出了一種基于ALTMEMPHY宏功能的DDR3 SDRAM控制器的設計方法。詳述了控制器基本結構和設計思想,分析了各模塊功能與設計注意事項,并

2010-07-30 17:13:55 30

30 要:本應用筆記說明了如何計算DS31256 HDLC控制器的總線帶寬。并展示了一個實驗室實測的結果。同時演示了一個總線利用率速算表,該速算表如果需要可以索要。

2009-04-18 11:24:11 1181

1181

用中檔FPGA實現高速DDR3存儲器控制器

引言

由于系統帶寬不斷的增加,因此針對更高的速度和性能,設計人員對存儲技術進行了優化。下一代雙數據速率(D

2010-01-27 11:25:19 879

879

Xilinx FPGA工程例子源碼:Xilinx DDR3最新VHDL代碼(通過調試)

2016-06-07 14:54:57 77

77 基于協議控制器的DDR3訪存控制器的設計及優化_陳勝剛

2017-01-07 19:00:39 15

15 描述:在此項測試中,每個Bank只訪問一次,接著依次訪問其它Bank。DDR3有限制在一定時間內可以輸入的Bank打開指令個數,即在一定時間內只允許輸入最多4個Bank打開命令。

2017-02-11 01:46:30 4005

4005

描述:在此項測試中,發起四次讀寫訪問,其中讀寫操作分別間隔開,四次讀寫操作訪問的地址都是同一個,由此觀察讀寫切換引入的帶寬開銷。

2017-02-11 01:48:08 4726

4726

為解決超高速采集系統中的數據緩存問題,文中基于Xilinx Kintex-7 FPGA MIG_v1.9 IP核進行了DDR3 SDRAM控制器的編寫,分析并提出了提高帶寬利用率的方法。最終將其進行

2017-11-16 14:36:41 19504

19504

為了滿足高速圖像數據采集系統中對高帶寬和大容量的要求,利用Virtex-7 系列FPGA 外接DDR3 SDRAM 的設計方法,提出了一種基于Verilog-HDL 語言的DDR3 SDRAM

2017-11-17 14:14:02 3290

3290

本文詳細介紹了在Xilinx Virtex-6系列FPGA中使用MIG3.7 IP核實現高速率DDR3芯片控制的設計思想和設計方案。針對高速實時數字信號處理中大容量采樣數據通過DDR3存儲和讀取

2017-11-17 14:26:43 24269

24269

為了解決視頻圖形顯示系統中多個端口訪問DDR3的數據存儲沖突,設計并實現了基于FPGA的DDR3存儲管理系統。DDR3存儲器控制模塊使用MIG生成DDR3控制器,只需通過用戶接口信號就能完成DDR3

2017-11-18 18:51:25 6412

6412

使用中速Kintex-7 325T FPGA演示DDR3控制器和接口,運行速度高于1866 Mbps數據速率。

2018-11-30 06:21:00 5277

5277

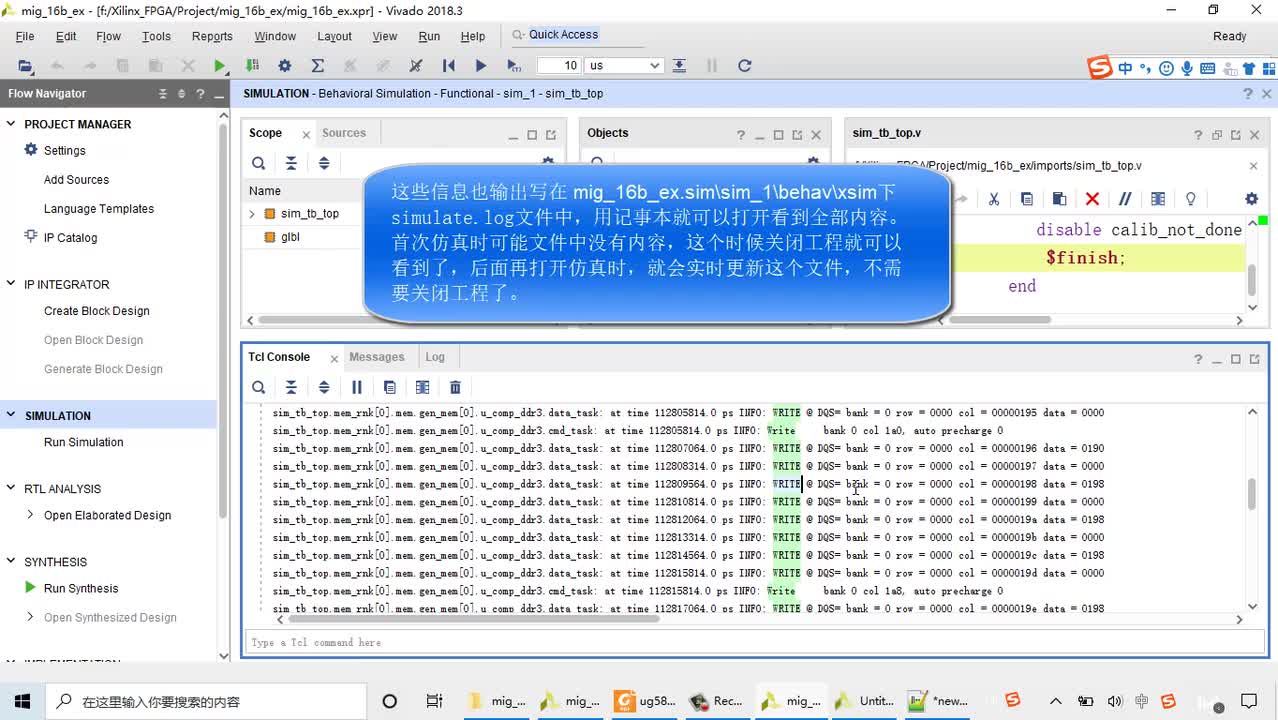

DDR對于做項目來說,是必不可少的。一般用于數據緩存和平滑帶寬。今天介紹下Xilinx DDR控制器MIG IP核的例化及仿真。 FPGA芯片:XC7K325T(KC705) 開發工具:Vivado

2020-11-26 15:02:11 7386

7386

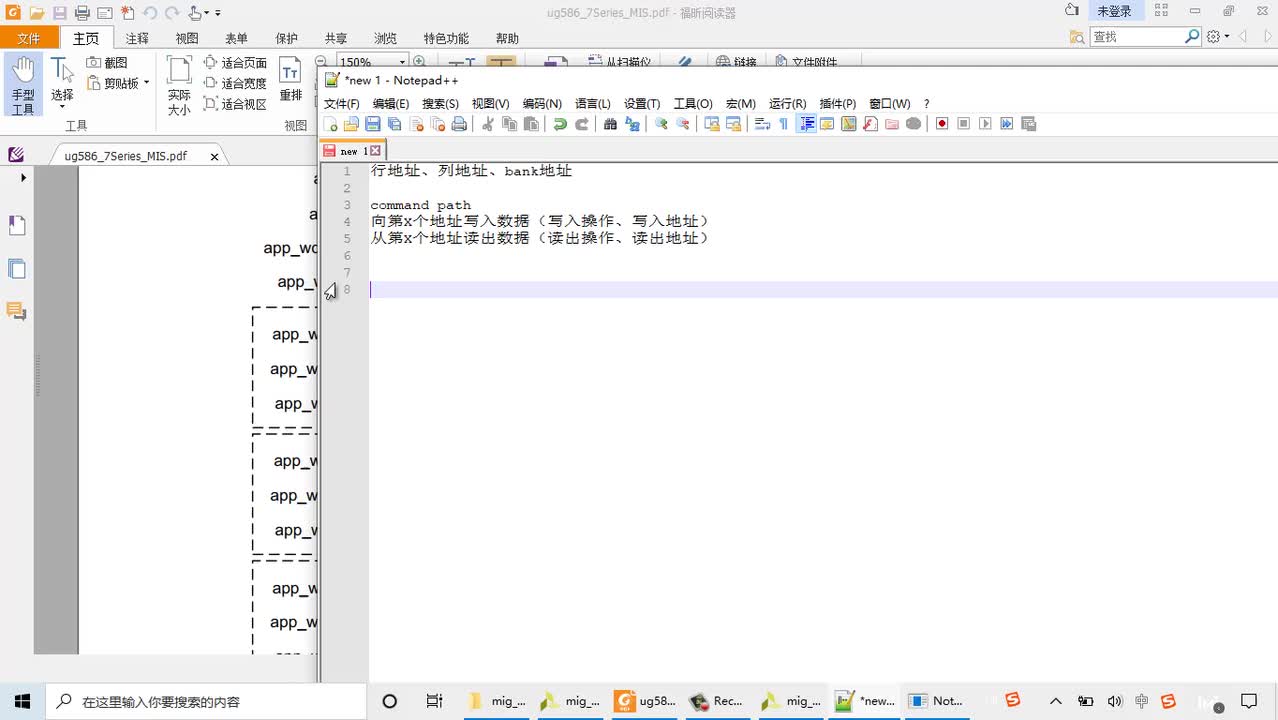

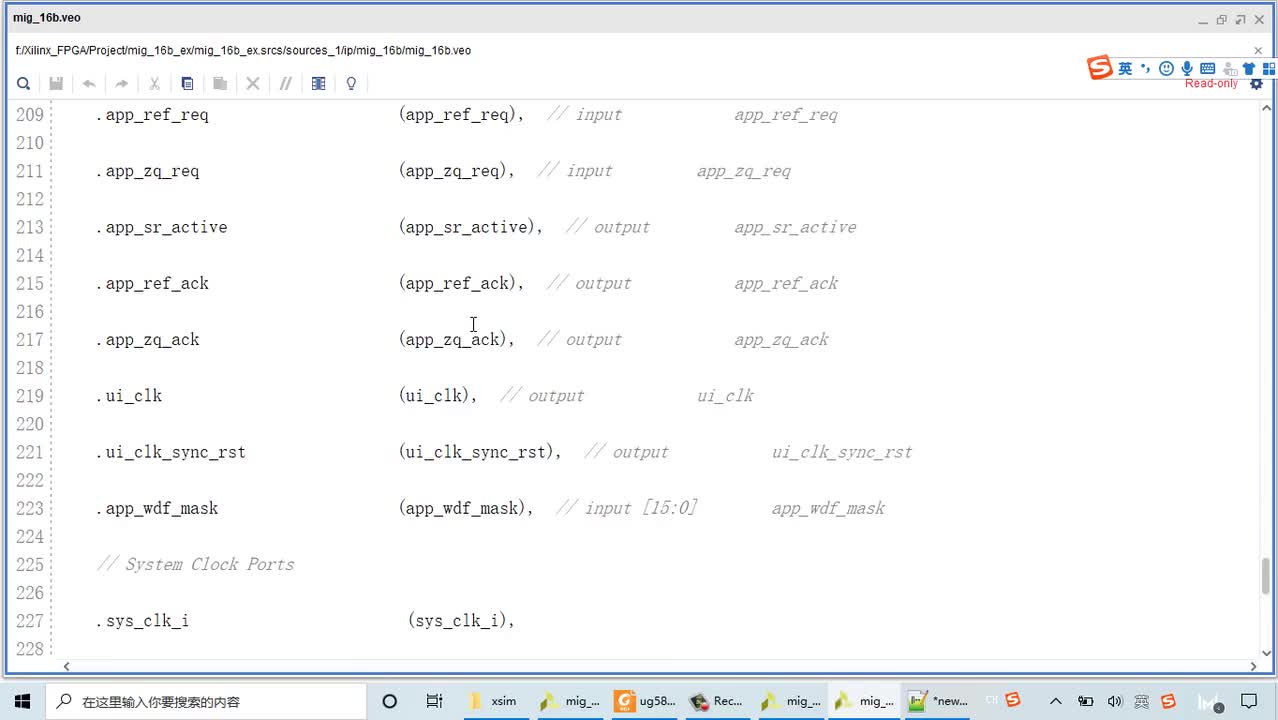

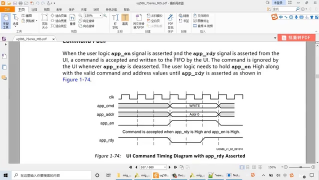

,以及對應的波形圖和 Verilog HDL 實現。我們調取的 DDR3 SDRAM 控制器給用戶端預留了接口,我們可以通過這些預留的接口總線實現對該 IP 核的控制,本章節將會講解如何根據 Xilinx 官方提供的技術參數來實現對 IP 核的寫控制。寫命令和寫數據總線介紹DDR3 SDRAM控制器I

2021-12-04 19:21:05 4

4 ??這篇文章我們講一下Virtex7上DDR3的測試例程,Vivado也提供了一個DDR的example,但卻是純Verilog代碼,比較復雜,這里我們把DDR3的MIG的IP Core掛在Microblaze下,用很簡單的程序就可以進行DDR3的測試。

2022-08-16 10:28:58 1241

1241 本文開源一個FPGA項目:基于AXI總線的DDR3讀寫。之前的一篇文章介紹了DDR3簡單用戶接口的讀寫方式:《DDR3讀寫測試》,如果在某些項目中,我們需要把DDR掛載到AXI總線上,那就要通過MIG IP核提供的AXI接口來讀寫DDR。

2023-09-01 16:20:37 1896

1896

本文介紹一個FPGA開源項目:DDR3讀寫。該工程基于MIG控制器IP核對FPGA DDR3實現讀寫操作。

2023-09-01 16:23:19 745

745

電子發燒友網站提供《完整的DDR、DDR2和DDR3內存電源解決方案同步降壓控制器數據表.pdf》資料免費下載

2024-03-13 10:16:45 0

0

電子發燒友App

電子發燒友App

評論