在數字電路中,出于應用的需要,我們可以使用無符號數,即包括0及整數的集合;也可以使用有符號數,即包括0和正負數的集合。在更加復雜的系統中,也許這兩種類型的數,我們都會用到。 有符號數通常以2的補碼

2020-11-18 17:46:10 16178

16178 不知道有沒有人像我一樣,長久以來將verilog中的有符號數視為不敢觸碰的禁區。

2023-12-04 16:13:21 259

259

無符號整型數據,將這兩數相乘后強制轉換為無符號字符型數據。并通過P0口將運算結果顯示出來在keil c51中創建新工程ex8,編寫如下程序代碼,編譯并生成ex8.hex文件。//實例87:利用P0

2012-03-22 10:43:43

:01010010這樣計算更為簡便符號描述運算規則&:與兩個位都為1時,結果才為1| :或兩個位都為0時,結果才為0^:異或兩個位相同為0,相異為1~:取反0變1,1變0>> :右移各二進位全部右移若干位,對無符號數,高位補0,有符號數,各編譯器處理方

2021-12-24 07:44:47

想法是,定義一個32位無符號整形,然后把它用二進制的形式顯示出來。如圖所示。 但是,最高8位一旦超過0x7f,就不正常了。這不是有符號整形才有的特點嗎? 無符號整形不應該呀。求好心人指點下。

2015-09-17 22:06:35

一.如果對一個32位無符號數開方,那么結果一定是一個16位無符號數。現設被開方的數為a,開方結果:b = b[15] * 2^15 + b[14] * 2^14 + ... + b[0] * 2^0

2009-09-21 09:12:45

轉換器的數據總線的邏輯構件。一、實驗目的1、了解算術邏輯運算器(74LS181)的組成和功能。2、掌握基本算術和邏輯運算的實現方法。二、實驗內容運用算術邏輯運算器 74LS181 進行有符號數/無符號數的算術運算和邏輯運算。三、實驗元器件1、算術邏輯運算器(74LS181)。2、三態門(74LS24

2022-01-25 08:11:31

hi,everyone:

我做優化時候,需要將一個有符號的32位 ?int 類型的數,做一個飽和操作,變成一個

無符號的8位的數。具體代碼如下:

int ?var;

if(var>255

2018-06-21 02:36:07

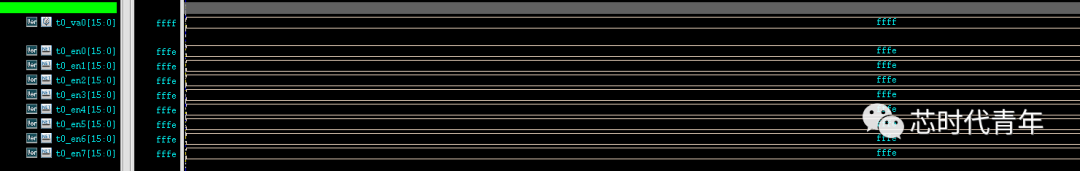

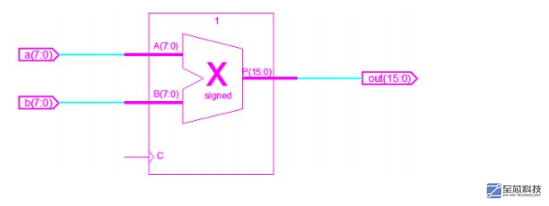

。 VerilogHDL中默認數據類型為無符號數,因此需要數學運算的場合必須要用“signed”聲明,如:reg signed [8-1:0] signal_a; wire signed [32-1:0

2018-08-13 09:27:32

;>>;有符號數算術移位和邏輯移位,兩者左移時一樣,右移時邏輯移位最高位填充的是0,算術移位最高位填充的是符號位。`

2012-02-23 16:45:35

LabVIEW對8-bit圖像進行濾波或算術運算8-bit(U8)無符號整數圖像并不包含負數,這樣的話如果對其進行的操作,例如IMAQ Convolute,IMAQ Subtract等等,結果出現

2022-06-16 20:58:21

Matlab符號數學工具箱應用說明Matlab符號運算是通過集成在Matlab中的符號數學工具箱(Symbolic Math Toolbox)來實現的。和別的工具箱有所不同,該工具箱不是基于矩陣

2009-09-22 15:28:46

在Bits的基礎上,SpinalHDL提供了UInt、SInt數據類型,從而能夠進行有符號/無符號數操作。變量定義/初始化UInt/SInt的初始化與Bits類型相似:邏輯操作符UInt/SInt

2022-07-14 14:45:15

Verilog HDL應用實例

2017-09-19 23:03:44

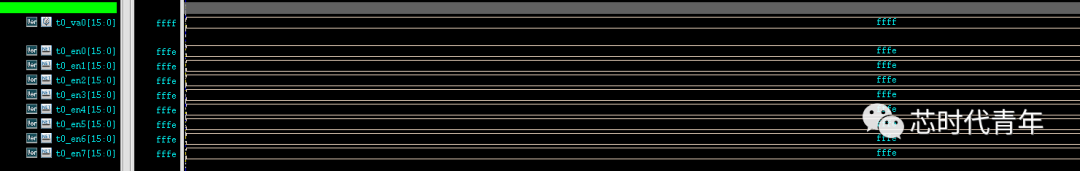

在代碼里面d和cnt都是無符號數,但是在編寫測試文件仿真的時候,modelsim中變成了有符號數,cnt計數到1023后也會變成負的,這是什么原因呢

2021-01-11 15:45:36

…………………………………………………………………………………………… 51、 無符號數一位乘法 …………………………………………………………………………… 72、 符號數一位乘法 ……………………………………………………………………………… 83、 布思算法(Booth

2012-08-12 11:59:01

stm32無符號8位轉換為int類型的方法是什么

2021-12-20 07:14:30

xilinx dds IP核輸出能不能改為無符號數,因為一般DA轉化器只能轉化正數

2015-09-29 18:30:23

常量90.00006 // 實數型常量"BOND" // 串常量;每個字符作為 8 位 ASCII 值存儲表達式中的整數值可被解釋為有符號數或無符號數。參數類似于常量,并且使用參數

2018-09-20 09:23:23

的C51定點運算庫,在乘除相關指令方面,沒能充分運用中穎SH79/88/89/F51系列自帶的 16位X8位硬件乘法器 和 16位/8位硬件除法器,網上搜了一下,中穎SH79/88/89/F51系列有個

2011-11-22 19:26:19

為什么MCU中的除法運算要比乘法運算的效率低

2023-10-09 07:45:11

乘除法運算本應用例的目的在于提供乘、除運算的函數及介紹乘除運算在SPMC75F2413A中的使用。應用例提供有符號和無符號數的乘除,其中包括32-Bit/16-Bit、16-Bit/8

2009-09-21 09:26:57

(1)加法帶符號數進行加法運算時,加數與被加數均用補碼形式表示,其結果仍為補碼,只要結果不超過規定的數表示的范圍,也就是只要不發生溢出,則結果總是正確的。而當發生溢出時,使符號位遭到破壞,則結果出錯

2019-12-11 17:58:19

,存儲無符號數)Tab = -4'd12;//整數Tab的十進制數為-12,位形式為110100.(因為Tab是整數寄存器變量,存儲有符號數)我的困惑是,-12的二進制補碼應該是10100,為什么這里寫成110100了?前面為啥多個1??求大神指教~謝謝!

2013-11-02 14:13:19

小弟我最近被一個問題糾結好久,就是有符號,無符號數,原碼補碼之間的運算,比如舉個例吧,-6和7,我去算它們之間的加法和乘法。假設輸入數據用8位2進制表示。首先,-6的原碼是10000110,補碼

2021-06-24 10:00:57

我有一個純粹的原理圖設計。當我嘗試獲取它的HDL實例化模板時,我得到這些錯誤:錯誤:找不到符號“mult32”錯誤:找不到符號“sub32”錯誤:找不到符號“sqrt”錯誤:找不到符號

2019-10-30 08:59:06

原碼、補碼、反碼、有符號數、無符號數概念.pdf

2012-11-15 08:44:54

雙狀態無符號數據類型雙狀態有符號數據類型四狀態數據類型

2021-01-18 06:03:15

問題:(1)從外部擴展RAM中讀取被乘數和乘數,乘數存放于0100H處開始,總共3個乘數,每個乘數是3字節的有符號數。被乘數存放于0200H處開始,總共3個被乘數,每個被乘數是3字節的有符號數。(2

2021-12-01 07:27:23

跪求各位大神有沒有基于verilog HDL的高速對數運算模塊設計的CORD IC算法實現自然對數運算的代碼

2016-03-10 12:39:28

我剛來這地方。對于Verilog中的FPGA乘法,在進行多重校對之前,是否需要擴展有符號數的符號位?或者,有一個庫可以自動處理這部分,就像我們如何使用VHDL進行乘法一樣?

2019-11-05 09:47:09

如何去實現單片機開發中無符號數的左移和右移運算呢?對于左移和右移的操作分別是如何呢?

2022-02-25 06:42:54

HelloIm試圖編寫代碼來計算16位無符號整數乘法的16位的機器周期,IM使用PIC16F87 4 MHz振蕩器。我知道在4 MHz時,1個機器周期需要1U。但是我不知道如何用16位無符號整數乘法

2019-03-27 06:47:34

LCD(16BPP)的ASCII(8x16)字庫數組為什么定義成16位無符號而不是8位,圖片資源文件為什么定義成8位:const uint16 ascii[4096] ={ };const uint8 gImage[614400] ={ };

2015-05-02 21:01:32

大家好,我在Virtex5上實現MAC(乘法和累加)單元。乘法器輸入8位被乘數和9位有符號乘法器。我的問題是實施的可行性是什么; DSP Slice或Fabric邏輯片? Y'

2020-03-27 10:33:23

為什么很多嵌入式算法 都將浮點數轉化為無符號整形,再進行運算,有些DSP自帶浮點運算庫的,但還是這樣轉換,本人初到,接觸了一部分歷程,有TI提供的,有大牛自己寫的,感覺對IQmath不熟悉,但知道

2017-04-26 20:07:55

嗨,可能是個愚蠢的問題。我有兩個像這樣的無符號變量(XC32):當在兩個變量之間求差時,我得到一個有符號的結果(即,在某個點上可能有負值)。為了糾正這個問題,我得到了結果的絕對值。我的問題是:我能配置XC嗎?32,使得兩個無符號變量的差值也是無符號的,從而避免了用戶的絕對設計錯誤。歡迎任何評論。

2020-03-24 07:50:43

本帖最后由 hq1987 于 2015-4-29 11:52 編輯

對于無符號數大家都基本理解,我主要說說有符號數,浮點數在機器世界里到底是怎么表示的。1、有符號數機器表示以16位有符號數為例

2015-04-29 10:15:32

兩個四位十進制數(BCD碼表示)的乘法運算

2013-04-04 13:34:59

求無符號數的平均數文章目錄題目重述問題分析以及求解思路程序代碼題目重述試求內部RAM30H~37H單元中8個無符號數的算術平均值,結果存入38H。問題分析以及求解思路待完善(請耐心等待)程序代碼

2021-12-01 08:01:16

求EDA四位乘法器實現0~9的平方運算

2017-06-12 10:58:53

1、實驗內容一 1.1、問題一: 設ROM中的表格TAB中存儲有8個無符號數(小于等于10),求這8個無符號數的算術平均值(結果只保留整數位),結果存入內部RAM30H中(先將TAB中存入8個常數

2021-07-14 08:08:08

基于FPGA的64位流水線加法器的設計基本要求: FPGA 可自行選擇可實現64位無符號數的加法運算8級流水線深度

2014-12-18 11:00:42

1. 移位運算符移位運算符是雙目運算符,將運算符左邊的操作數左移或右移運算符右邊的操作數指定的位數,用0來補充空閑位。如果右邊操作數的值為X或Z,則移位結果為未知數X。Verilog HDL中有兩種

2015-04-30 09:43:36

用Rom比較兩個4bit無符號數,怎么實現?ROM寬度和深度怎么計算?

2015-09-24 14:33:07

請問AFE5801 AD轉換后數字信號是用有符號數還是無符號數表示的啊?

2019-05-24 08:04:13

小弟最近在用STM32F030C6T6芯片完成電機的SVPWM控制。現在發現算法中,運行速度很慢。打算將所有的除法運算改成移位運算。一般的,無符號數的右移幾位和除以2的幾次冪是等效的。但是,在STM32里面,有符號數的右移也和除法運算等效嗎?

2019-01-22 08:14:26

嗨,如何在Vivado項目中實例化hdl系統生成器輸出的多個實例?在vivado項目中很容易實例化一個hdl系統生成器輸出。當我想將另一個實例實例化到同一個項目時,我在合成狀態下面臨一些錯誤。最好的祝福

2020-07-31 10:38:59

和signed在一種類型下,unsigned表示在這個范圍大小的整數,signed一般都是在這個范圍內的從負到正,即其最高位為符號位。unsigned( 無符號整數 ):無符號整數 (unsig...

2021-07-02 07:59:47

1. 計算機中的符號位l 數據類型的最高位用于標識數據的符號A. 最高位為1,表面這個數為負數B. 最高位位0,表面這個數為正數2. 有符號表示法l 在計算機內部用補碼表示有符號數A. 正數的補碼為

2017-05-16 21:43:16

的時候怎么都不正確,具體原因如下,字符串轉數值的時候只發現可以轉換成無符號數,而采集下來的數據是有符號數,轉換成無符號數之后就無法正確顯示波形了。請教采集卡采集下來的有符號字符串類型的數據如何正確

2012-05-02 11:55:08

6.1 無符號數和有符號數6.2 數的定點表示和浮點表示6.3 定點運算6.4 浮點四則運算6.5 算術邏輯單元

2009-04-11 09:33:33 0

0 Verilog hdl教程實例

【例 3.2】4 位計數器module count4(out,reset,clk);output[3:0] out;input reset,clk;reg

2010-02-09 09:41:01 54

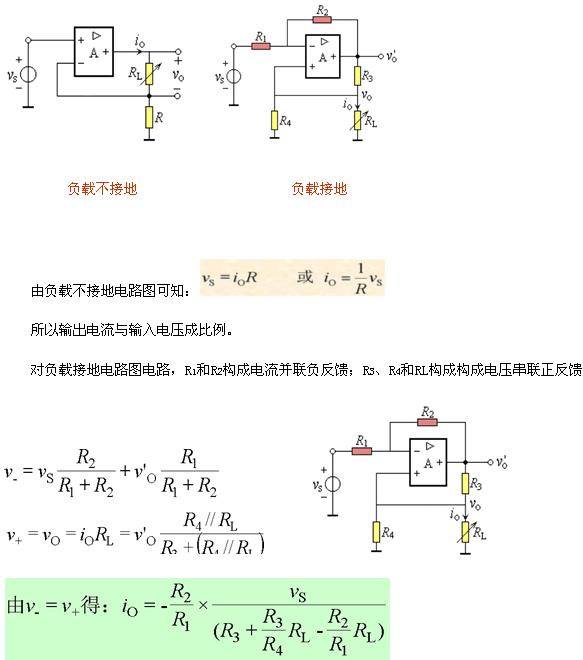

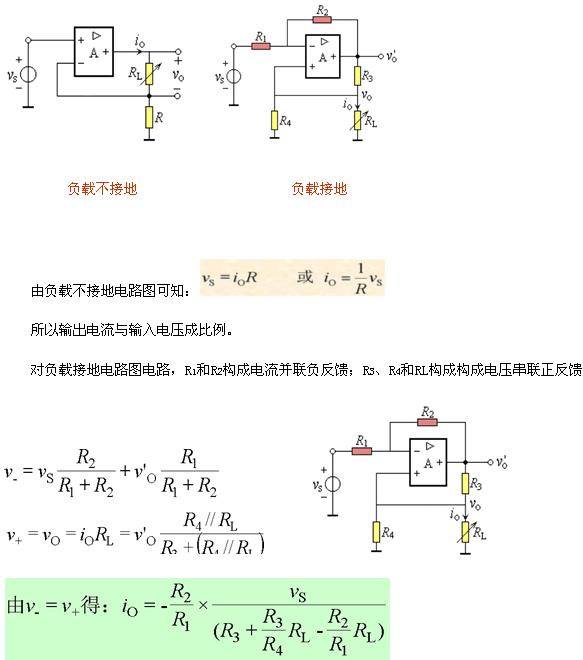

54 模擬乘法器在運算電路中的應用

8.6.1 乘法運算電路

8.6.2 除法運算電路

8.6.3 開方運算電路

2010-09-25 16:28:45 145

145 乘除運算電路

基本乘除運算電路,乘法電路

乘法器符號

2008-01-17 12:54:12 2705

2705

單字節無符號數據塊排序(增序)

入口條件:數據塊的首址在R0中,字節數在R7中。出口信息:完成排序(增序)影響資源

2009-01-19 22:58:25 1005

1005 原碼一位乘法的實現算法(一) 用原碼實現乘法運算是十分方便的。原碼表示的兩個數相乘,其乘積的符號為相乘兩數符號的異或值,數值則為兩數絕對值之積。假

2009-10-13 22:53:26 10820

10820

原碼乘法,原碼乘法原理詳解

1.人工算法與機器算法的同異性 在定點計算機中,兩個原碼表示的數相乘的運算規則是:乘積的符號位由兩數的

2010-04-13 10:55:30 31588

31588 補碼乘法,補碼乘法計算詳細解說 1.補碼與真值得轉換公式 補碼乘法因符號位參與運算,可以完成補碼數的“直接”乘法,而不需要求補級

2010-04-13 11:05:06 35427

35427 電路簡單的PWM乘法運算電路

電路的功能

脈沖寬度調制的乘法運算器

2010-05-08 14:23:16 3167

3167

乘法器在模擬運算電路中的應用

相乘運算

2010-05-18 16:48:06 1879

1879 本內容介紹了應用Verilog HDL進行數字系統設計實例

2011-09-27 16:30:29 87

87 該ALU采取層次化設計方法,由控制模塊、邏輯模塊、加減法模塊、乘法模塊和除法模塊組成,能實現32位有符號數和無符號數的加減乘除運算,另外還能實現9種邏輯運算、6種移位運算以

2012-02-09 15:24:55 80

80 該程序實現功能:16位無符號數的乘法運算

2012-05-16 11:02:00 3198

3198 Verilog HDL應用程序設計實例精講。

2016-05-20 11:16:35 90

90 Verilog HDL應用程序設計實例精講

2016-05-20 11:16:35 284

284 MSP430硬件乘法器是一種外圍設備,并不構成MSP430 CPU的一部分。它允許進行簽名和無符號數的乘法運算。還支持乘法和累加(MAC)操作,這對于實現諸如有限脈沖響應(FIR)濾波器的數字信號處理(DSP)任務是有用的。

2018-05-07 09:38:18 8

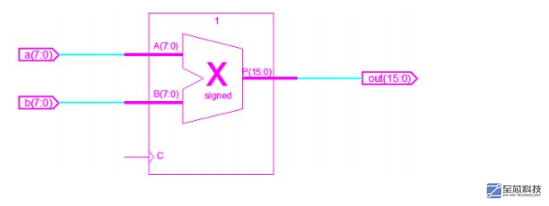

8 ?在設計中,所有的算數運算符都是按照無符號數進行的。如果要完成有符號數計算,對于加、減操作通過補碼處理即可用無符號加法完成。對于乘法操作,無符號數直接采用“*”運算符,有符號數運算可通過定義輸出

2018-10-09 15:22:29 5658

5658

Matlab 符號運算是通過符號數學工具箱(Symbolic Math Toolbox)來實現的。Matlab 符號數學工具箱是建立在功能強大的 Maple 軟件的基礎上的,當 Matlab 進行符號運算時,它就請求 Maple 軟件去計算并將結果返回給 Matlab。

2018-10-31 08:00:00 0

0 Matlab 符號運算是通過符號數學工具箱(Symbolic Math Toolbox)來實現的。Matlab 符號數學工具箱是建立在功能強大的 Maple 軟件的基礎上的,當 Matlab 進行符號運算時,它就請求 Maple 軟件去計算并將結果返回給 Matlab。

2019-07-24 16:03:26 33

33 輸入系統的有正有負的模擬信號在AD采樣前,會加上了直流偏置變成全正信號才輸入AD的,所以在AD采樣后送給FPGA的信號是無符號數。

2019-08-11 11:43:39 2821

2821 理解:對于兩個有符號數X,Y,不外乎有四種情況,即(正,負),(負,正),(正,正),(負,負)。所有程序里就這四種情況進行討論就行了。

2019-10-17 15:59:35 7502

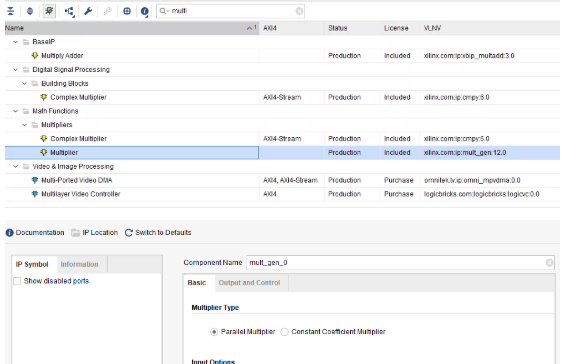

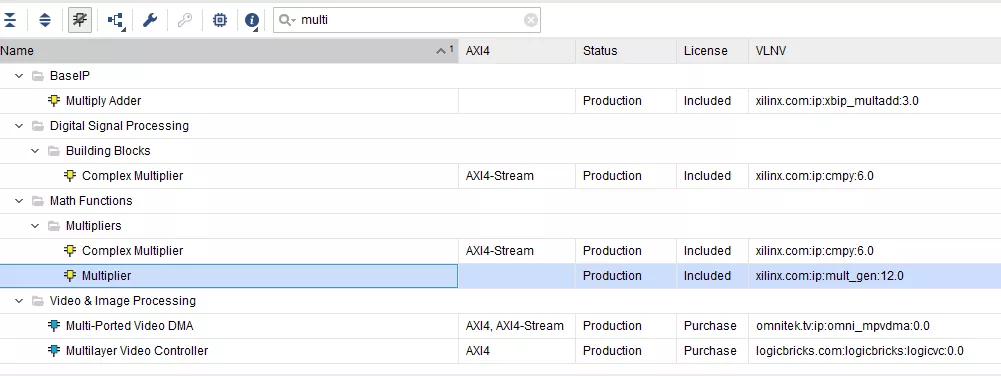

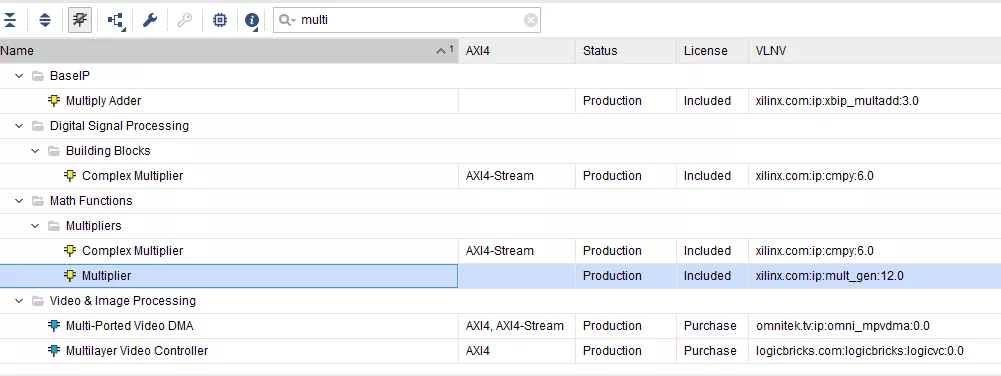

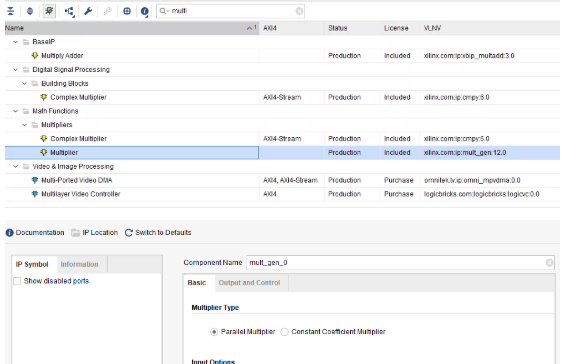

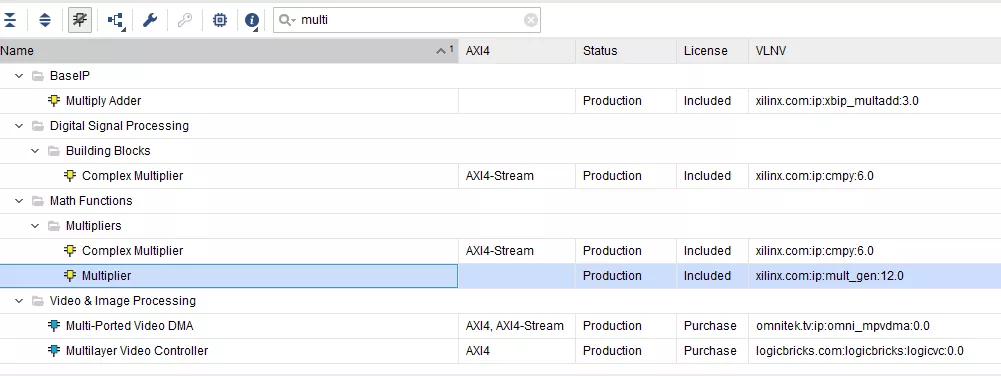

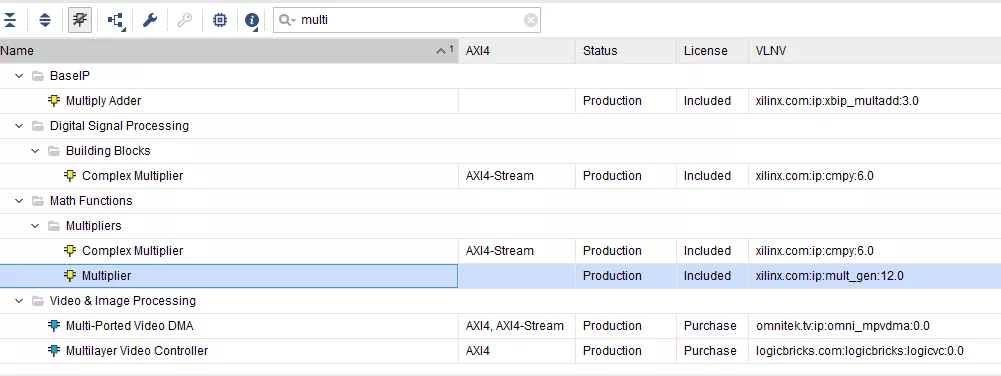

7502 FPGA中乘法器是很稀缺的資源,但也是我們做算法必不可少的資源。7系列及之前的FPGA都是25x18的DSP,UltraScale中是27x18,我們可以通過調IP Core的方式或者原語的方式來進行乘法操作。在里面可以設置有符號還是無符號數乘法。

2020-03-08 17:14:00 6251

6251

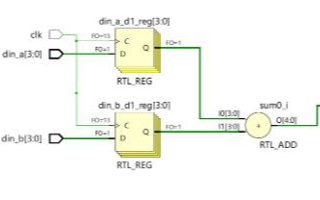

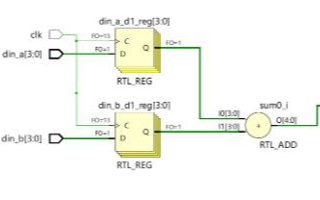

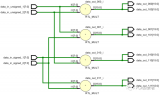

采用HDL代碼描述加法運算只需要用操作符+即可,這看似很簡單,這里我們以兩個4-bit數相加為例,對輸入/輸出數據均寄存,從而形成如下圖所示電路。 此電路對應的HDL代碼如下圖所示。這里采用

2020-09-24 14:31:15 1996

1996

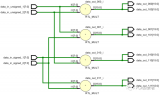

原語的方式來進行乘法操作。在里面可以設置有符號還是無符號數乘法。 當然,我們也可以直接使用*符合來進行乘法,對于無符號的乘法 reg [7:0] ubyte_a;reg [7:0] ubyte_b

2020-09-27 15:12:52 8952

8952

有符號數的計算在 Verilog 中是一個很重要的問題(也很容易會被忽視),在使用 Verilog 語言編寫 FIR 濾波器時,需要涉及到有符號數的加法和乘法,在之前的程序中我把所有的輸入輸出和中間信號都定義成有符號數,這樣在計算時沒有出現問題,下面實際試驗一下 Verilog 的乘法問題;

2021-05-02 10:48:00 6035

6035

基于空間相關性分析的符號數據分類

2021-06-09 14:41:15 8

8 問題:(1)從外部擴展RAM中讀取被乘數和乘數,乘數存放于0100H處開始,總共3個乘數,每個乘數是3字節的有符號數。被乘數存放于0200H處開始,總共3個被乘數,每個被乘數是3字節的有符號數

2021-11-23 10:21:09 25

25 在單片機開發中,通常會使用左移和右移操作做快速的乘法和除法運算。例如,將0x0001左移1位,相當于乘以2^1左移2位相當于乘以2^2,以此類推,左移n位,相當于乘以2^n。右移則相當于除以

2022-01-13 13:17:21 2

2 FPGA中乘法器是很稀缺的資源,但也是我們做算法必不可少的資源。7系列及之前的FPGA都是25x18的DSP,UltraScale中是27x18,我們可以通過調IP Core的方式或者原語的方式來進行乘法操作。在里面可以設置有符號還是無符號數乘法。

2022-02-16 16:21:36 4197

4197

給定四個無符號數,請找出最小值。無符號數可以與標準比較運算符(a < b)進行比較。使用條件運算符描述一個兩路的最小值電路,然后組合它來創建一個4路最小電路。可能需要一些線向量作為中間結果。

2022-09-28 17:07:03 929

929 我們學習一下Systemverilog中的有符號數據類型的賦值。

2022-10-17 14:40:26 694

694 為了省流,還是先甩結論。有符號數和無符號數的最本質區別就是:符號位的識別和高位拓展。除此之外,另一個區別就是從人的角度如何如何讀這個數,或者說$display(%d)打印時打印的值是什么(而從機器的角度它壓根就不區分signed和unsigned)。

2023-12-10 10:50:46 380

380

電子發燒友App

電子發燒友App

評論