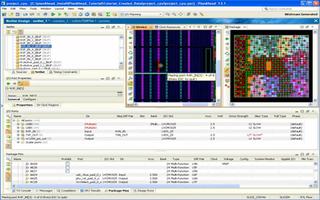

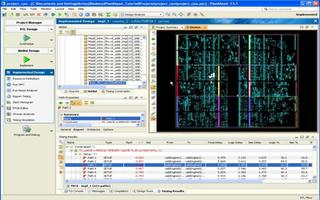

原文:在排布FPGA管腳生成ucf文件的過程中,當(dāng)FPGA管腳較多的時(shí)候,手工排布管腳不僅效率低,而且很容易出錯。借助PlanAhead和Adept等工具,可以很方便快速的實(shí)現(xiàn)管腳排布。特別是當(dāng)需要排布的管腳有一定的規(guī)律或者需要滿足一些條件時(shí),使用工具進(jìn)行管腳排布具有很明顯的優(yōu)勢。??

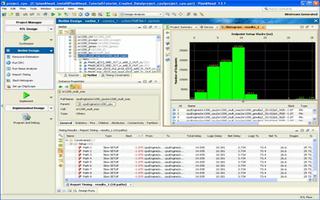

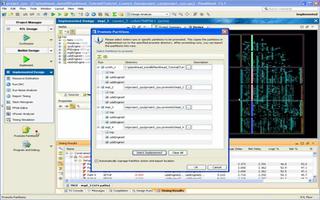

當(dāng)大量管腳需要分配時(shí),首先需要將這些管腳分配到指定的區(qū)域內(nèi),如將同一條總線的管腳分配在同一個(gè)bank里面,將同一個(gè)接口所有管腳分配在幾個(gè)連續(xù)的bank里面等等。因此,首先可以準(zhǔn)備一個(gè)ucf,然后將需要分配的管腳錄入,只指明線網(wǎng)名字和電平標(biāo)準(zhǔn)。然后在PlanAhead里面建立一個(gè)進(jìn)行IO Planning的工程,導(dǎo)入這個(gè)ucf。如果導(dǎo)入的是一個(gè)已經(jīng)排布好的管腳,需要重新排布,可以選中所有管腳,去除現(xiàn)有排布;如果有差分信號線,首先將差分信號線的P和N綁定。然后指定所選bank里面的禁用管腳,將指定的管腳組(如一條總線)放入此bank中,使用的命令是place IO port in an IO bank。對于放置在同一個(gè)bank中的不同類型信號,如普通數(shù)據(jù)總線和時(shí)鐘輸入信號,可以先將該bank的所有時(shí)鐘功能管腳、VREF管腳、VRP/VRN功能都先禁止掉,然后把數(shù)據(jù)總線排布下去,然后打開被禁用的是時(shí)鐘功能管腳,再將時(shí)鐘功能管腳自動排布下去。按照此方法,依次將所有的管腳放入指定區(qū)域。此時(shí),所有管腳都已經(jīng)按一定的順序規(guī)則的排布在各個(gè)bank里面,如一條位寬為36bits的總線,總線內(nèi)各個(gè)管腳按編號從小到大一次排布在芯片的連續(xù)36個(gè)管腳位置;如果是差分信號,則P/N對分別放置在bank的一對P/N管腳上。?? ?完成此過程以后,將管腳排布結(jié)果導(dǎo)出到ucf里面,然后再將ucf導(dǎo)入到Adept中,進(jìn)行小范圍內(nèi)的調(diào)整。在Adept界面中,可以看到一個(gè)bank中各種管腳的類型,現(xiàn)在需要做的,是在bank范圍內(nèi)做微調(diào)。具體而言,如果隨路時(shí)鐘輸入沒有走時(shí)鐘管腳,則需要將隨路時(shí)鐘輸入放置在SRCC或MRCC管腳上,如果本bank有管腳電平標(biāo)準(zhǔn)需要用到VREF和DCI,則必須把VREF和VRP/VRN管腳保留,不能用作用戶管腳。這些操作只需在Adept界面執(zhí)行簡單的粘貼復(fù)制命令就能完成,不容易引入書寫錯誤,而且只需花費(fèi)少量的時(shí)間就可完成。當(dāng)這些細(xì)節(jié)調(diào)整做好以后,就可以將結(jié)果再次導(dǎo)出到ucf中,此時(shí)ucf中管腳排布按照bank整齊的排列,在同一個(gè)bank中也是按順序排布。在此ucf的基礎(chǔ)上,稍作整理,就產(chǎn)生了最終可用的ucf文件。

如何使用PlanAhead/Adept加速管腳排布

- FPGA(591969)

- PlanAhead(9692)

- Adept(1514)

相關(guān)推薦

“套種式”陣列排布的高性能天線的設(shè)計(jì)方案

本期將介紹通過將單極子天線(Monopole)與空氣貼片天線(Patch)等距交錯排布,形成一種“套種式”的陣列排布方式以提高天線間的隔離度,該方案結(jié)構(gòu)簡單,效果顯著,適用于大規(guī)模高性能天線的設(shè)計(jì)。

2022-09-30 15:17:28 982

982

982

982PCB疊層設(shè)計(jì)層的排布原則和常用層疊結(jié)構(gòu)

層疊結(jié)構(gòu)是影響PCB板EMC性能的一個(gè)重要因素,也是抑制電磁干擾的一個(gè)重要手段。本文介紹多層PCB板層疊結(jié)構(gòu)的相關(guān)內(nèi)容。對于電源、地的層數(shù)以及信號層數(shù)確定后,它們之間的相對排布位置是每一個(gè)PCB工程師都不能回避的話題;

2016-08-04 11:27:07 6502

6502

6502

6502PlanAhead 14.4無法在Win7 x64上加載

我不能在運(yùn)行Win7 64bit的2臺不同PC上運(yùn)行PlanAhead 14.4。將出現(xiàn)一個(gè)命令窗口,其中包含TCL提示和消息:特定于應(yīng)用程序的初始化失敗:無法重命名“auto_load”:命令

2018-11-27 14:32:52

PlanAhead 14.6無法在Windows 8.1 x64上打開

我嘗試從Xilinx ISE項(xiàng)目導(dǎo)航器中打開PlanAhead后期合成... PlanAhead加載將顯示一秒然后消失。我從cmd附加了以下錯誤。如果有人有修復(fù)或者遇到同樣的問題,請告訴我。

2020-03-24 09:38:45

PlanAhead 14.6無法運(yùn)行

我剛剛在一臺運(yùn)行13.4的機(jī)器上安裝了ISE 14.6,沒有任何問題。當(dāng)我嘗試從命令行運(yùn)行PlanAhead時(shí)(在運(yùn)行settings64.sh之后 - 它是64位機(jī)器),我得到以下錯誤。我嘗試了一

2018-11-30 11:09:39

PlanAhead 30天試用已激活 使用vc4vsx35進(jìn)行合成失敗

嗨,我剛剛啟動了ISE 13.1的30天試用版,并希望為vc4vsx35合成一些verilog代碼。即使激活似乎有效(planAhead和一大堆IP只被激活了30天),我得到錯誤:錯誤:Xst

2018-11-21 14:27:55

PlanAhead怎么實(shí)現(xiàn)僅靜態(tài)設(shè)計(jì)

我在PR設(shè)計(jì)方面遇到了麻煩,所以我試圖退后一步并在相同的條件下實(shí)現(xiàn)它,但沒有PR約束。我正在嘗試使用相同的工具(PlanAhead)來保持盡可能多的變量。我有一個(gè).ngc,.edf和.ucf,我試圖

2018-10-12 14:34:22

PlanAhead約束丟失

你好,我最近開始使用planahead來處理在6系列設(shè)備上運(yùn)行的一些傳統(tǒng)設(shè)計(jì)。確切地說,我使用synplify進(jìn)行綜合,然后使用planahead來實(shí)現(xiàn)。我的問題是關(guān)于約束。基本上我

2018-11-06 11:34:53

PlanAhead許可證失敗

。在我嘗試運(yùn)行PlanAhead之前,一切似乎都很順利,我收到以下錯誤消息。僅供參考我使用的是第一次安裝ISE時(shí)提供的相同許可證。

2020-03-06 09:01:34

PlanAhead許可證收到此錯誤消息怎么回事

大家好,我為我的不同項(xiàng)目安裝了ISE 14.6和Vivado 2016.4(我使用來自不同系列的FPGA)......我生成了vivado許可證(包括ISE),但如果我嘗試訪問“PlanAhead

2020-05-25 06:08:39

Planahead不能放置攜帶鏈實(shí)例

你好,Planahead讓我瘋狂。我只想說我必須使用planahead,因?yàn)檫@是一個(gè)Spart6項(xiàng)目,因此升級到vivado或準(zhǔn)系統(tǒng)ISE不是一個(gè)選擇。最近,并且由于沒有明顯的原因

2018-11-12 14:34:56

planAhead錯誤,無法找到現(xiàn)有許可證

我的許可證管理器表明我有一個(gè)有效的planAhead許可證,但是當(dāng)我啟動快捷方式時(shí),由于錯誤消息指示無法找到許可證,我無法運(yùn)行。請指教以上來自于谷歌翻譯以下為原文My license manager

2018-12-21 11:10:25

planahead 14.7設(shè)置bitgen選項(xiàng)

在planahed中設(shè)置bitgen選項(xiàng)時(shí)(在附加選項(xiàng)字段中)我需要在應(yīng)用“應(yīng)用”按鈕之前選中/取消選中其中一個(gè)選項(xiàng)。這可以在下一個(gè)planahead用戶界面中解決以上來自于谷歌翻譯以下為原文

2019-03-05 13:58:25

planahead中ip核生成時(shí)的warning如何去掉

我在planahead中產(chǎn)生ip核時(shí)總會有個(gè)warning去不掉如下[sim 0] Verilog simulation file type 'Behavioral' is not valid

2012-10-09 11:24:30

AT89C52各引腳功能及管腳電壓

AT89C52各引腳功能及管腳電壓概述:AT89C52P為40 腳雙列直插封裝的8 位通用微處理器,采用工業(yè)標(biāo)準(zhǔn)的C51內(nèi)核,在內(nèi)部功能及管腳排布上與通用的8xc52 相同,其主要用于會聚調(diào)整

2008-10-10 14:55:27

Digilent Adept USB設(shè)備斷開后立即連接是怎么回事?

= 3 [1001.616308] u*** 2-1:產(chǎn)品:Digilent Adept USB Device [1001.616311] u*** 2-1:制造商:Digilent

2019-09-09 09:19:54

Spartan6中的ODDR2使用Planahead設(shè)置和重置沖突

我正在使用ODDR2生成外部時(shí)鐘(ISE = 13.1,Planahead = 13.1):clk5m_inst:ODDR2通用映射(DDR_ALIGNMENT =>“NONE”, - 將輸出

2019-06-17 14:43:06

USB Type-C引腳及各種模式的排布介紹

您了解USB Type-C連接器嗎?本篇文章主要介紹了USB Type-C引腳的排布,并簡要介紹了其各種模式。USB Type-C是USB連接器系統(tǒng)的規(guī)范,在智能手機(jī)和移動設(shè)備上越來越受歡迎,并且能

2021-12-27 07:59:33

WebPack和PlanAhead 14.1無法獲得許可證

你好,我在Windows 7,64位上運(yùn)行Xilinx ISE 14.1。我獲得了WebPack許可證,ISE 14.1工作正常。但是,當(dāng)我打開PlanAhead 14.1時(shí),我收到以下消息:“無法

2018-11-29 16:14:47

Xilinx PlanAhead部分動態(tài)重配置疑問

Xilinx PlanAhead工具資料說可以用來部分動態(tài)重配置,我現(xiàn)在想對芯片的每一幀中每一位進(jìn)行逐位翻轉(zhuǎn)的動態(tài)重配置,使用PlanAhead能夠?qū)崿F(xiàn)么?應(yīng)該怎么理解Planahead的部分重配置,如何應(yīng)用?希望知道的朋友告訴下,對這個(gè)有點(diǎn)迷茫。

2015-06-01 10:11:33

為什么我用ISE進(jìn)行fPga引腳約束時(shí)調(diào)用不出PlanAhead呢?

為什么我用ISE進(jìn)行fPga引腳約束時(shí)調(diào)用不出PlanAhead呢?真是好無語啊

2015-01-11 13:10:21

使用Planahead導(dǎo)入項(xiàng)目怎么將微膠片轉(zhuǎn)換為黑盒子

你好,當(dāng)導(dǎo)入和現(xiàn)有的ISE項(xiàng)目進(jìn)入planahead時(shí),我收到一些嚴(yán)重的警告。我試圖為我的項(xiàng)目創(chuàng)建一個(gè)平面圖。令我非常困惑的一件事是,如果我去ISE>用戶約束>布局規(guī)劃區(qū)域邏輯,它打開

2018-10-16 13:25:56

使用Exploreahead和planahead時(shí)地圖錯誤

你好當(dāng)我使用Exploreahead和planahead時(shí),我在映射階段收到以下錯誤消息錯誤:打包:1107- 無法將以下符號組合到單個(gè)IOB組件中:BUF符號`Circuit_M5M

2018-10-09 15:42:52

關(guān)于xilinx adept下載問題

我用的是xilinx basys2的板子,前邊用adept下過幾個(gè)程序但是今天謝了一個(gè)流水燈的程序后在用adept加載生成的.bit文件的時(shí)候顯示unable to associate file

2012-11-24 10:29:32

關(guān)于通過PlanAhead修改管教約束但是ucf文件修改不成功的問題,來個(gè)大神解答。

原工程是在xilinx sp-6芯片上的現(xiàn)在想在v-6的評估板上跑,所以我用PlanAhead來改了管腳約束,然后保存了。但是打開ucf一看發(fā)現(xiàn)管腳約束一點(diǎn)都沒變,然后布線的時(shí)候也發(fā)生報(bào)錯。求大神

2015-09-07 15:57:46

在64位Ubuntu 10.04 LTS上運(yùn)行PlanAhead 13.2收到錯誤消息

在64位版本的Ubuntu 10.04(LTS)上啟動PlanAhead 13.2時(shí),收到以下錯誤消息:[:43:GNU / Linux:意外的運(yùn)算符/ opt / Xilinx / 13.2

2018-11-22 11:46:33

如何使用Digilent的Adept和工具來編寫devkit

這是一個(gè)如何使用Digilent的Adept和工具來編寫這個(gè)devkit,專門針對Windows用戶。在影響13.3時(shí)遇到了一些問題,所以我一直在尋找一種更直接的方法來設(shè)計(jì)開發(fā)板。看看

2019-07-04 13:45:15

如何使用Xilinx PlanAhead合并EDK和ISE系統(tǒng)?

嗨,是否有任何文檔可以解釋如何使用Xilinx PlanAhead合并EDK和ISE系統(tǒng)? (我閱讀了Xilinx EDK概念,工具和技術(shù)指南......)關(guān)于Zynq-7000 SoC(在

2019-02-22 09:03:57

如何啟用planAhead部分重新配置?

尊敬的先生/女士,我沒有在新項(xiàng)目設(shè)計(jì)源中指定合成(edif或ngc)網(wǎng)表選項(xiàng)下設(shè)置PR項(xiàng)目,使用planahead進(jìn)行部分重新配置..我在設(shè)置分區(qū)階段面臨問題..當(dāng)我在網(wǎng)表視圖中選擇分區(qū)時(shí)..i沒有設(shè)置用于可重新配置分區(qū)的分區(qū)向?qū)?.請告訴如何啟用PR..please幫助

2019-11-05 07:14:38

如何在PlanAhead I / O引腳分配中啟動LVDS系統(tǒng)時(shí)鐘?

如何在PlanAhead I / O引腳分配中啟動LVDS系統(tǒng)時(shí)鐘? I / O STD列中沒有LVDS選項(xiàng)?

2019-09-17 08:19:59

如何將EDK planAhead項(xiàng)目遷移到vivado

大家好,我正在將EDK planAhead項(xiàng)目遷移到vivado。在遷移我的一個(gè)pcoreblock時(shí),我收到了該錯誤,并且遷移根本沒有發(fā)生。“錯誤:[filemgmt 20-730]找不到文件集

2020-05-05 16:59:20

如何將在EDK中的BMM文件導(dǎo)入PlanAhead

嗨,我需要正確導(dǎo)入EDK系統(tǒng)到PlanAhead。目前我的系統(tǒng)在SDK程序開始運(yùn)行時(shí)出錯。錯誤是“錯誤:目標(biāo)上不支持調(diào)試操作”。我認(rèn)為錯誤的原因是BMM文件沒有從EDK正確導(dǎo)入PlanAhead。1

2019-03-25 12:03:25

如何更改planahead啟動目錄?

嗨,我正在Windows 7上運(yùn)行planahead 14.7。它給出了一個(gè)錯誤“無法打開句柄planAhead.jou。請檢查目錄'C:\'的訪問權(quán)限。您應(yīng)該從可寫的工作目錄重新啟動應(yīng)用程序。”我

2019-03-07 14:14:43

如何更改ise,edk和planahead的菜單字體?

嗨,我在redhat 5 linux平臺上安裝了ise 12.3。如何更改ise,edk和planahead的菜單字體?它們很小,看得很清楚。我可以更改編輯器的字體,但無法找到與之相關(guān)的選項(xiàng)菜單

2018-11-26 14:41:53

安裝14.1時(shí)缺少PlanAhead文件

,XST14.psg。當(dāng)我啟動PlanAhead時(shí),這些會導(dǎo)致錯誤。也許更重要的是,.xinstall \ mnf \ planahead_0014.mnf是空的。進(jìn)行猜測,看起來

2018-12-05 10:57:28

怎么將VHDL模塊添加到PlanAhead頂級verilog文件

我有通過PlanAhead生成的MicroBlaze設(shè)計(jì)。我想將VHDL邏輯連接到XPS中生成的BRAM。 MicroBlaze將通過本地存儲器總線訪問一個(gè)端口,將第二個(gè)端口訪問VHDL。編寫

2019-03-05 13:31:25

怎么改多媒體鍵盤的鍵值和按鍵排布順序?

\EVT\EXAM\BLE\HID_Keyboard\Project怎么改多媒體鍵盤的鍵值和按鍵排布順序有沒有什么軟件可以生成HID的描述符摳藍(lán)牙HID協(xié)議真的是很費(fèi)勁

2022-09-05 07:57:08

無法在Win32 XP上啟動Vivado和Planahead 14.4

Planahead。對于這兩個(gè)我收到類似這樣的錯誤消息(德語為“應(yīng)用程序無法正確初始化”):從本文檔的第12頁開始http://www.xilinx.com/support/documentation

2018-12-03 15:46:41

未在PlanAhead中實(shí)施

嗨,我的項(xiàng)目在ISE中運(yùn)作良好。當(dāng)我使用PlanAhead時(shí),會收到這些錯誤[NgdBuild 604]無法解析類型為“dcm_fixed”的邏輯塊“Inst_SysCon

2018-10-25 15:25:51

硬件電路的設(shè)計(jì),排布的資料誰有,分享下或者給個(gè)鏈接

小白,想補(bǔ)充一些硬件電路的知識,太深奧的我也不會,就想找一些硬件電路的設(shè)計(jì),排布一類的適合初學(xué)者的 學(xué)習(xí)資料

2015-12-05 11:45:27

請問沒有USB2 Adept端口時(shí)我的主板將有多少受損?

您好,我?guī)滋烨百I了一塊Atlys主板,今天早上我打破了主板,這是我的錯,我試圖放入一個(gè)太小的機(jī)箱,而且Adept USB2插頭已經(jīng)連接了一根電纜,因?yàn)樗饕瑢?b class="flag-6" style="color: red">Adept USB2端口拆開,說實(shí)話我

2019-09-02 06:33:31

輸入錯誤:44:網(wǎng)絡(luò)未完全放置和布線planahead 14.7

嗨,我已經(jīng)在planahead中實(shí)現(xiàn)了一個(gè)非常簡單的設(shè)計(jì)(有三個(gè)模塊)。兩個(gè)模塊在經(jīng)過一些計(jì)算后將值發(fā)送到第三個(gè)模塊,該模塊通過UART發(fā)送數(shù)據(jù)。這是在virtex-7板上完成的,特別是

2020-04-20 07:18:18

#硬聲創(chuàng)作季 #FPGA 明德?lián)P FPGA至簡設(shè)計(jì)原理與應(yīng)用29_QUARTUS_編譯和配置管腳

fpga管腳

水管工發(fā)布于 2022-09-20 12:06:47

用PlanAhead的必要設(shè)計(jì)——賽靈思培訓(xùn)課程

PlanAhead軟件特征;把設(shè)計(jì)導(dǎo)入到PlanAhead工程環(huán)境;為優(yōu)化速度分配I/O;運(yùn)行DRC和噪聲分析;導(dǎo)入HDL源,闡述和分析RTL網(wǎng)表;從Xilinx IP目錄實(shí)例化一個(gè)核心。

2010-12-14 15:04:47 0

0

0

0Xilinx可編程邏輯器件設(shè)計(jì)與開發(fā)(基礎(chǔ)篇)連載37:Spartan

這里介紹如何用PlanAhead進(jìn)行RTL代碼開發(fā)與分析。需要說明一點(diǎn),本章所用的所有實(shí)例都可以在PlanAhead的安裝目錄E:\Xilinx\11.1\PlanAhead\testcases\PlanAhead_Tutorial下找到,本節(jié)使用的是source文件夾中的文件。

2017-02-11 07:34:36 618

618

618

618

Virtex5 FPGA在ISE + Planahead上部分可重構(gòu)功能的流程和技術(shù)要點(diǎn)

部分可重構(gòu)技術(shù)是Xilinx FPGA的一項(xiàng)重要開發(fā)流程。本文結(jié)合Virtex5 FPGA,詳細(xì)講解在ISE + Planahead上完成部分可重構(gòu)功能的流程和技術(shù)要點(diǎn)。

2018-07-04 02:17:00 3419

3419

3419

3419

如何使用PlanAhead Design工具來提高設(shè)計(jì)性能?

PlanAhead 設(shè)計(jì)方法提供了性能、生產(chǎn)力以及結(jié)果的可重復(fù)性。憑借其層次化設(shè)計(jì)流程,PlanAhead 軟件可讓您減少運(yùn)行 PAR 然后返回 RTL 與綜合的反復(fù)次數(shù)。相反,您可以分析設(shè)計(jì)并在實(shí)現(xiàn)之前解決物理方面的問題。

2018-07-18 10:30:00 4073

4073

4073

4073

【PlanAhead教程】-3 Synthesis and Implementation

教您如使用PlanAhead 13.1進(jìn)行設(shè)計(jì)應(yīng)用,通過一個(gè)設(shè)計(jì)程序,來體驗(yàn)PlanAhead的功能強(qiáng)大

2018-06-05 09:46:00 3008

3008

3008

3008

【PlanAhead教程】-1 Introduction

教您如使用PlanAhead 13.1進(jìn)行設(shè)計(jì)應(yīng)用,通過一個(gè)設(shè)計(jì)程序,來體驗(yàn)PlanAhead的功能強(qiáng)大

2018-06-04 13:47:00 2495

2495

2495

2495

【PlanAhead教程】-6 IO Pin Planning

教您如使用PlanAhead 13.1進(jìn)行設(shè)計(jì)應(yīng)用,通過一個(gè)設(shè)計(jì)程序,來體驗(yàn)PlanAhead的功能強(qiáng)大

2018-06-04 13:47:00 4239

4239

4239

4239

【PlanAhead教程】-5 Netlist Analysis and ChipScope Core Insertion

教您如使用PlanAhead 13.1進(jìn)行設(shè)計(jì)應(yīng)用,通過一個(gè)設(shè)計(jì)程序,來體驗(yàn)PlanAhead的功能強(qiáng)大

2018-06-04 13:47:00 2632

2632

2632

2632

【PlanAhead教程】-2 Start_Project and Source File Management

教您如使用PlanAhead 13.1進(jìn)行設(shè)計(jì)應(yīng)用,通過一個(gè)設(shè)計(jì)程序,來體驗(yàn)PlanAhead的功能強(qiáng)大

2018-06-04 13:47:00 2446

2446

2446

2446

【PlanAhead教程】-7 Results Analysis and Floorplanning

教您如使用PlanAhead 13.1進(jìn)行設(shè)計(jì)應(yīng)用,通過一個(gè)設(shè)計(jì)程序,來體驗(yàn)PlanAhead的功能強(qiáng)大

2018-06-04 01:47:00 2618

2618

2618

2618

【PlanAhead教程】-4 RTL and IP Design

教您如使用PlanAhead 13.1進(jìn)行設(shè)計(jì)應(yīng)用,通過一個(gè)設(shè)計(jì)程序,來體驗(yàn)PlanAhead的功能強(qiáng)大

2018-06-01 13:52:00 2864

2864

2864

2864【PlanAhead教程-9】Summary and More Information

教您如使用PlanAhead 13.1進(jìn)行設(shè)計(jì)應(yīng)用,通過一個(gè)設(shè)計(jì)程序,來體驗(yàn)PlanAhead的功能強(qiáng)大

2018-06-01 13:47:00 2408

2408

2408

2408

【PlanAhead 13.1教程】Design Preservation

教您如使用PlanAhead 13.1進(jìn)行設(shè)計(jì)應(yīng)用,通過一個(gè)設(shè)計(jì)程序,來體驗(yàn)PlanAhead的功能強(qiáng)大

2018-05-22 13:47:54 3549

3549

3549

3549

如何在Zynq-7000的PlanAhead/XPS流程中使用MIO與EMIO配置

了解MIO和EMIO如何相關(guān)以及如何使用首選的PlanAhead / XPS流將信號傳遞到“真實(shí)世界”。

2018-11-26 06:27:00 3272

3272

3272

3272組件排布方式及接線對光伏系統(tǒng)成本的影響

前 言隨著平價(jià)上網(wǎng)和低補(bǔ)貼時(shí)代的到來,對系統(tǒng)的精細(xì)化設(shè)計(jì)要求越來越高;小固發(fā)現(xiàn),對于不同的組件和逆變器,優(yōu)化的組件排布和接線能夠降低投資成本,提升系統(tǒng)發(fā)電量。此外,我們還整理了文章,方便大家查看

2019-07-18 11:26:02 8873

8873

8873

8873不同形式的組件排布,哪種收益更高?

前言在光伏系統(tǒng)里組件排布的設(shè)計(jì)非常重要,好的組件排布對整體安裝容量、安裝難易程度、長期發(fā)電量及保障投資收益,都有不少區(qū)別,小固今天探討的話題就是不同安裝形式的組件排布哪種收益更高。一般來說,常見

2019-07-29 11:45:47 3294

3294

3294

3294關(guān)于不同形式的組件排布的收益研究

通過比較:橫向雙排的用鋼量要比豎向雙排排布要略多一些,經(jīng)優(yōu)化后,實(shí)際應(yīng)用中組件橫排與豎排用鋼量幾乎一致,尤其是橫向三排或四排VS豎向雙排的對比;但水泥墩要多一些成本。

2019-10-21 11:43:47 1672

1672

1672

1672如何排布LED燈可以實(shí)現(xiàn)三種基本色

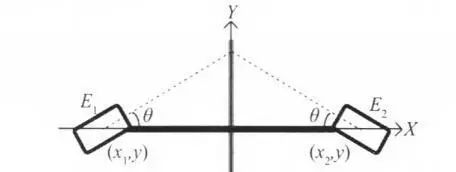

一種三種基本色LED的五燈排布方法,其排布具有如下特征:每個(gè)LED均勻規(guī)則等距離分布,整個(gè)顯示屏由RGBGR方陣作為基本單元排列組成,其組成元素構(gòu)成正方形

2019-10-15 16:28:10 5701

5701

5701

5701cache的排布與CPU的典型分布

對cache的掌握,對于Linux工程師(其他的非Linux工程師也一樣)寫出高效能代碼,以及優(yōu)化Linux系統(tǒng)的性能是至關(guān)重要的。簡單來說,cache快,內(nèi)存慢,硬盤更慢。在一個(gè)典型的現(xiàn)代CPU中比較接近改進(jìn)的哈佛結(jié)構(gòu),cache的排布大概是這樣的:

2022-10-18 09:01:12 1195

1195

1195

1195電池排布方式對21700鋰電池相變熱管理系統(tǒng)的影響

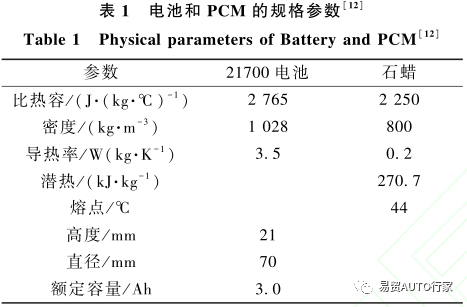

本文以21700鋰離子電池組為研究對象,通過對不同排布方式下的鋰電池分別控制電池間距?對流換熱系數(shù)和PCM導(dǎo)熱率,并分別進(jìn)行仿真分析,研究電池間距?對流換熱系數(shù)和PCM導(dǎo)熱率的變化對不同排布方式下以相同比體積的相變材料包裹下21700鋰離子電池的最高溫度和溫差的影響?

2023-04-04 14:45:29 905

905

905

905

八字形和雙T形電感排布方案介紹

八字形電感排布方案 八字形電感排布同樣也可以跟雙水平電感一樣,在直道行駛時(shí)保持良好的采集數(shù)據(jù)獲取。 通過計(jì)算分析兩端電感數(shù)值,判斷出小車與賽道中心線的偏離方向及偏差量,從而做出相應(yīng)的方向控制 并且在

2023-11-28 17:37:05 344

344

344

344

電子發(fā)燒友App

電子發(fā)燒友App

評論