電子發(fā)燒友網(wǎng)核心提示:本文為玩轉(zhuǎn)賽靈思Zedboard開發(fā)板(3):基于Zynq PL的流水燈,內(nèi)容精彩,敬請對電子發(fā)燒友網(wǎng)保持密切關(guān)注。基于Zynq PL的流水燈是使用PL做流水燈實(shí)驗(yàn),目的是為

2012-12-05 14:25:41 12770

12770 8.5部分實(shí)例

2015-03-12 17:44:47

。如圖所示,在Zstar板子左側(cè)靠下的位置有一排的LED指示燈,從左往右數(shù)第4個、第5個和第6個LED指示燈分別是D3、D2和D1。 2 板級調(diào)試參考文檔《玩轉(zhuǎn)Zynq-環(huán)境篇

2019-08-28 09:26:47

and Configuration 《Xilinx Zynq Soc與嵌入式Linux設(shè)計(jì)實(shí)戰(zhàn)指南》第3章更多資料共享 鏈接:https://share.weiyun.com/5s6bA0s`

2019-04-16 06:56:32

靈活性也就越小。在Xilinx的FPGA器件中,IP核設(shè)計(jì)是非常重要并且必不可少的一部分,應(yīng)該說,前述的軟IP、固IP和硬IP,在我們Zstar板載的Zynq上都能夠找到蹤影。而對于Vivado來說

2019-09-06 08:13:18

`玩轉(zhuǎn)Zynq連載28——[ex50] 第一個Zynq系統(tǒng)工程“HelloZynq” 更多資料共享騰訊微云鏈接:https://share.weiyun.com/5s6bA0s百度網(wǎng)盤鏈接

2019-09-30 12:57:32

`玩轉(zhuǎn)Zynq連載30——[ex52]基于Zynq PS的GPIO控制 更多資料共享騰訊微云鏈接:https://share.weiyun.com/5s6bA0s百度網(wǎng)盤鏈接:https

2019-10-10 11:21:06

的就是PL的引腳)。關(guān)于MIO和EMIO的關(guān)系,更形象直接的可以示意如圖所示。MIO和EMIO都是PS的一部分,但是MIO可以直接連接到Zynq芯片的引腳上,和PL無關(guān);而EMIO需要通過PL的IO

2019-10-12 17:35:16

不同通道使用情況下的數(shù)據(jù)吞吐量。大家可以在此基礎(chǔ)上,更改不同的AXI HP總線時鐘頻率,以評估時鐘頻率對AXI HP總線的影響。2 AXI總線協(xié)議介紹參考文檔《玩轉(zhuǎn)Zynq-基礎(chǔ)篇:AXI總線協(xié)議介紹

2019-11-28 10:11:38

參考xilinx下述3個文檔。●pg091-xadc-wiz.pdf●ug480_7Series_XADC.pdf●ug585-Zynq-7000-TRM.pdf的Chapter 30

2019-12-03 11:17:44

一些良好的干凈的怪異樂趣。對于那些使用過不同EDA工具的人,我希望easyEDA.com的一瞥至少是有趣的,如果不是鼓勵,如果你想嘗試不同的東西。在本系列的第2部分中,我將分享我對KiCad的經(jīng)歷

2018-11-01 15:54:02

Wind Turbine (Part 1) 垂直軸風(fēng)力機(jī)(第1部分)以ANSYS 17.0為例。該算例分為兩個部分,第一部分將采用運(yùn)動參考系(Moving Frame of Reference(MRF...

2021-07-12 06:38:54

本帖最后由 飛兒朵朵2012 于 2016-11-3 22:20 編輯

GB 7000.1-2015 燈具 第1部分:一般要求與試驗(yàn)

2016-09-18 22:02:20

GBT 20234.2-2015 電動汽車傳導(dǎo)充電用連接裝置 第2部分 交流充電接口

2018-03-22 08:02:30

IEC 62305-1(雷電防護(hù) 第1部分 總則)前言3簡介31. 范圍和目標(biāo).42. 規(guī)范性參考文件.43. 術(shù)語和定義.44. 雷擊電流參數(shù)... 95. 雷電的損害... 95.1 對建筑物

2011-01-22 17:03:54

PADSlogic電子檔第2部分有需要的可以下載

2013-09-21 18:00:38

Protel99se 安裝好了,一部分ddb文件能打開,一部分pcb格式打不開,該怎么辦

2011-12-21 20:14:15

STM32 F 103 C 6 T 7 xxx 1 2345 6 78 第1部分:產(chǎn)品系列名,固定為STM32 第2部分:產(chǎn)品類型;F表示這是Flash產(chǎn)品,目前沒有其它選項(xiàng) 第3部分

2014-10-09 19:03:28

TCL 9321/9421部分/9621部分(TDA3505/TEA1014)原理圖文件下載

2021-06-25 08:32:05

YY 0505-2012 醫(yī)用電氣設(shè)備 第1-2部分 安全通用要求并列標(biāo)準(zhǔn) 電磁兼容 要求和試驗(yàn) (見附件)

2015-06-03 12:49:54

”的pdf文檔。 《深入淺出玩轉(zhuǎn)FPGA(第2版)》 的主要讀者對象為電子、計(jì)算機(jī)、控制及信息等相關(guān)專業(yè)的在校學(xué)生、從事FPGA/CPLD開發(fā)設(shè)計(jì)的電子工程師以及所有電子設(shè)計(jì)制作的愛好者們。目錄第一部分

2017-02-04 17:06:09

`第58章 SPINBOX控件 本期教程講解STemWin支持的SPINBOX控件。 58. 1 SPINBOX控件介紹 58. 2 官方WIDGET_Spinbox實(shí)例 58. 3 使用官方

2015-05-23 11:56:07

本信號鏈電源優(yōu)化系列文章的第1部分討論了如何量化電源噪聲以確定其影響信號鏈器件的哪些參數(shù)。通過確定信號處理器件可以接受而不影響其所產(chǎn)生信號的完整性的實(shí)際噪聲限值,可以創(chuàng)建優(yōu)化的配電網(wǎng)絡(luò)(PDN)。在

2021-12-19 08:00:00

使用高速轉(zhuǎn)換器時,有哪些重要的PCB布局布線規(guī)則?第一部分討論了為什么AGND和DGND接地層未必一定分離,除非設(shè)計(jì)的具體情況要求您必須這么做。第二部分討論了輸電系統(tǒng)(PDS),以及電源層和接地

2018-10-30 14:56:34

使用高速轉(zhuǎn)換器時,有哪些重要的PCB布局布線規(guī)則?(第2部分)本RAQ的第一部分討論了為什么AGND和DGND接地層未必一定分離,除非設(shè)計(jì)的具體情 況要求您必須這么做。第二部分討論印刷電路板(PCB

2018-10-30 14:57:01

固件和硬核 IP,我們將把它們留給我們的下一部分——第二部分和第三部分。 在本系列文章中,我們將把我們的談話分為以下幾個部分: 保護(hù)您的 IP 內(nèi)核——第一部分軟 IP,第一節(jié):HDL 代碼的加密保護(hù)您

2022-02-23 11:59:45

關(guān)于Zynq的理論部分,文大部分截圖摘抄自《zynqbook》ZYNQ架構(gòu)雙核ARM Cortex-A9 處理器:ARM Cortex-A9 是一個應(yīng)用級的處理器,能運(yùn)行完整的像Linux 這樣

2021-07-23 10:11:25

GB 9706.1-2007 醫(yī)用電氣設(shè)備 第1部分:安全通用要求

2014-12-23 16:12:22

如何玩轉(zhuǎn)STM32-F429系列

2021-10-13 06:45:39

如何玩轉(zhuǎn)STM32-F429系列控制器?

2021-11-12 06:06:38

/Adam-Taylor-s-MicroZed-Chronicles-Part-180-All-about-the-Xilinx/ba-p/756988但該芯片自帶板,Zynq 7020屬于Zynq家族。是否可以在電路板上使用它?如果沒有,支持reVision的官方(Xilinx / AVNet / ...)主板的最低成本是多少?籌碼怎么樣?

2019-10-10 06:25:58

如何零死角玩轉(zhuǎn)STM32-F429系列

2021-10-13 08:47:02

如何零死角玩轉(zhuǎn)STM32-F429系列?

2021-10-12 07:43:14

的C2000™ F28379 MCU,開發(fā)人員現(xiàn)在可以避免上文提到的很多缺點(diǎn)。

在本系列的下一部分中,我們進(jìn)一步研究將FPGA引入到驅(qū)動和伺服機(jī)控制架構(gòu)中時所遇到的其它挑戰(zhàn)。

原文鏈接

2018-08-31 15:41:28

布局電源板以最大限度地降低EMI:第1部分

2019-09-05 15:36:07

布局電源板以最大限度地降低EMI:第2部分

2019-09-06 08:49:33

問題:1.第1部分看懂一點(diǎn),第2部分完全不知道要干什么,第3部分那樣處理也不知道是要做什么。2.這個電路要實(shí)現(xiàn)的功能是一個從幾十到幾百赫茲的帶通濾波。3.已經(jīng)用Multisim仿真過,得到的結(jié)果是

2018-07-26 10:00:39

構(gòu)建混合測試系統(tǒng)第1部分:為成功過渡奠定基礎(chǔ)

2019-11-06 09:36:06

DN110- 微功率降壓/升壓電路,第2部分:將四節(jié)電池轉(zhuǎn)換為5V *

2019-06-11 16:31:41

。圖1.抽取系數(shù)為8時,每8個樣本僅選擇第8個樣本,拋棄7個樣本。你們猜猜第二個問題是什么?在第2部分中,我們將看看其他常見問題之一,敬請期待。

2018-10-26 11:16:21

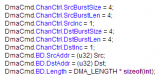

我昨天才發(fā)現(xiàn)我的兩塊microZED板都有相同的MAC地址(第一次將它們同時插入網(wǎng)絡(luò))。通過u-boot代碼,我看到MAC地址被烘焙到環(huán)境中(在zync_common.h中)。#define

2019-09-16 14:57:55

STM32部分知識共享:

2015-08-10 13:43:15

基礎(chǔ)普及 筆記1 初識FPGA 筆記2 應(yīng)用領(lǐng)域 筆記3 開發(fā)流程 第二部分 設(shè)計(jì)技巧 筆記4基本語法 筆記5 漫談狀態(tài)機(jī)設(shè)計(jì) 筆記6 復(fù)位設(shè)計(jì) 筆記7 FPGA重要

2012-02-27 10:45:37

STM32標(biāo)準(zhǔn)庫的引入視頻課程-第3季第6部分 互聯(lián)網(wǎng)課程品牌《朱老師物聯(lián)網(wǎng)...

2021-08-03 06:31:06

跪求《深入淺出玩轉(zhuǎn)FPGA(第2版)》這本書電子版

2015-10-08 07:44:27

在學(xué)習(xí)運(yùn)算放大器穩(wěn)定性分析(TI合集)第5部分的時候,計(jì)算beta是有點(diǎn)疑惑,為什么beta = VFB / delta VOA ?而不是beta = VFB / VOA?

2022-04-01 10:21:51

野火系列之STM32從初級到玩轉(zhuǎn)單片機(jī)PDF教程全集

2013-11-21 20:28:50

本文基于FPGA的 PicoBlaze嵌入式平臺,開發(fā)了一種利用串口通信,可實(shí)時控制的計(jì)時器系統(tǒng)。分析了PicoBlaze和串口的結(jié)構(gòu)、原理,提出了計(jì)時器的設(shè)計(jì)方案。基用Virtex-II Pro系列FPGA開發(fā)

2010-01-20 15:48:37 19

19 摘要:詳細(xì)分析8位微處理器IP core PicoBlaze的結(jié)構(gòu)、原理與設(shè)計(jì)方案;介紹PicoBlaze的指令集和調(diào)試工具pblazeIDE,討論PicoBlaze的編程方案和應(yīng)用設(shè)計(jì)實(shí)例;列

2009-06-20 10:54:39 741

741

By Adam Taylor 到目前為止的文章中,我們已經(jīng)研究了MicroZed開發(fā)板上使用以太網(wǎng)的數(shù)據(jù)傳輸問題。我們還沒有涉及片上外設(shè)通信的問題:實(shí)時時鐘,非易失內(nèi)存以及獨(dú)特的傳感器。這些通信涉及到I2C或者SPI總線。

2017-01-13 11:07:11 748

748 在Adam Taylor玩轉(zhuǎn)MicroZed系列的前期部分中,我們介紹了IP棧的概念。(見Adam Taylor玩轉(zhuǎn)MicroZed系列第79部分:Zynq SoC以太網(wǎng)第3部分)接下來就是在我們的設(shè)計(jì)中使用該協(xié)議棧了。SDK開發(fā)環(huán)境允許我們創(chuàng)建BSP的時候包含一個輕量級的IP棧(lwIP)。

2017-01-13 11:17:11 1033

1033

By Adam Taylor 在本系列博客的前兩部分中,我們研究了帶有Zynq SoC PS(處理器系統(tǒng))的以太網(wǎng)MAC(介質(zhì)訪問控制層),包括深入探討了一個MAC使用范例。以太網(wǎng)MAC是一個基礎(chǔ)的構(gòu)建模塊,它允許我們實(shí)現(xiàn)一個IP棧,然后因此給我們的工程創(chuàng)建聯(lián)網(wǎng)條件。

2017-01-13 11:24:11 669

669 By Adam Taylor 在約束系列的最后,我們講講關(guān)聯(lián)布局宏(RPM)的約束。RPM允許你在FPGA的布局中將DSP、FF、LUT和RAMS等資源組合在一起。與PBlocks不同,RPM并不

2017-11-10 14:49:02 748

748 By Adam Taylor 在過去一周中,我接到了很多不同人的來信,他們正在使用以Zynq為基礎(chǔ)的開發(fā)工具。他們非常想知道怎么樣去把MicroZed系列博客教程應(yīng)用到他們所選擇的硬件平臺上。加上

2017-02-08 02:12:49 426

426

研究了相關(guān)的時序約束后,在設(shè)計(jì)中我們也不能忽視所能運(yùn)用到的物理約束。一個工程師最常用的物理約束是I/O管腳的放置和與每個I/O腳相關(guān)的參數(shù)定義(標(biāo)準(zhǔn)、驅(qū)動能力等)。然而,還有其它類型的物理約束: ?放置約束——定義元件位置 ?布線約束——定義信號布線 ?I/O腳約束——定義I/O腳位置和I/O腳參數(shù) ?配置約束——定義配置方法 按照慣例,有一些約束獨(dú)立于這些組之外。Vivado套件有三個約束,并且主要用于網(wǎng)表: ?DONT_TOUCH——用來防止

2017-02-08 02:20:11 206

206

By Adam Taylor 在先前的博客中我們研究過I/O約束,下一個合乎邏輯的步驟就是研究如何在我們的設(shè)計(jì)中用FPGA進(jìn)行放置和布線約束。使用放置約束的原因如下:為了幫助實(shí)現(xiàn)時序,或者

2017-02-08 02:22:11 238

238 通過前面的學(xué)習(xí),我們已經(jīng)對Zynq系列的PL和PS部分已經(jīng)有了相當(dāng)多的了解。其中有關(guān)約束的部分我們曾經(jīng)提到過但是沒有重點(diǎn)關(guān)注。約束可以添加特定的信息到你的設(shè)計(jì),并在綜合工具和實(shí)現(xiàn)工具中可以得到實(shí)現(xiàn)

2017-02-08 03:58:43 645

645

上周的博客中我們完成了硬件的搭建,并且把硬件部分導(dǎo)入到SDK,見Adam Taylor’s MicroZed Chronicles Part 67: AXI DMA II,下一步通過寫一個簡單的程序

2017-02-08 05:53:11 303

303

作者Adam P. Taylor,e2v首席系統(tǒng)工程師 PicoBlaze是一個緊湊型8位軟核處理器,F(xiàn)PGA工程師可以在他們選擇的賽靈思FPGA將其例化。一旦實(shí)現(xiàn),該核完全位于FPGA架構(gòu)

2017-02-08 06:22:11 210

210 上周的博客中我們學(xué)習(xí)了Zynq SoC的AXI DMA,我解釋了怎樣利用AXI DMA控制器將數(shù)據(jù)從PL搬運(yùn)到PS。在本期博客中我們將學(xué)習(xí)怎樣完成硬件的搭建。 首先我們要更深入的了解一下AXI

2017-02-08 08:10:39 286

286 有意思的方面,就是它能夠?qū)?shù)據(jù)從PL(可編程邏輯)部分移動至存儲器中——例如片上存儲器或者DDR SDRAM,而存儲器是映射到PS的地址空間上的。 作為工程師我們一直想這樣做,將在Zynq PL部分實(shí)現(xiàn)的硬件存儲器映射到PS部分的地址空間中,這是非常有用的,因?yàn)檫@樣做可以允

2017-02-08 08:14:11 153

153

在本系列上一篇博客中,我們學(xué)習(xí)了解了使用XMD和XSDB來調(diào)試我們的應(yīng)用和系統(tǒng)。然而為了確保我們的應(yīng)用在性能上是優(yōu)化的,另一個非常重要的方面就是對應(yīng)用程序進(jìn)行詳細(xì)分析。 分析不同于調(diào)試,就分析功能

2017-02-08 09:53:00 130

130 在此系列博客的前面幾期中,我們已經(jīng)可以運(yùn)行示例應(yīng)用并獲得用于分析的程序運(yùn)行數(shù)據(jù)。運(yùn)行分析器可以生成一個gmon.out格式的文件,它包含了分析數(shù)據(jù)。當(dāng)應(yīng)用程序運(yùn)行自然結(jié)束或者通過SDK來終止應(yīng)用程序

2017-02-08 09:56:49 180

180

在上一篇的MicroZed系列博客中,我們學(xué)習(xí)了兩種與XADC進(jìn)行通信的方法:Zynq SoC 的AXI或者DevC接口。通過在每個驅(qū)動程序中輸出XADC的基地址,我演示了這兩種XADC通信方法

2017-02-08 09:58:42 221

221 討論,這個問題解決之后我們將回來繼續(xù)學(xué)習(xí)PicoBlaze。 前面的博客中提到,有多種方式可以實(shí)現(xiàn)XADC與Zynq之間的交互,除了JTAG接口: 1.我們可以借助DevC接口實(shí)現(xiàn)XADC與PS(處理器系統(tǒng))之間的直接交互,使用這種方式時,Zynq SoC的PL(可編程邏輯)部分不需要進(jìn)行配置。然

2017-02-08 10:04:11 242

242 前面的幾篇博客中,我們通過介紹怎樣驅(qū)動CCD的一些知識了解了PicoBlaze的一些特點(diǎn),同時也知道了通過Zynq PS(處理器系統(tǒng))可是實(shí)現(xiàn)PicoBlaze的動態(tài)可重配置,我覺得在這次博客當(dāng)中

2017-02-08 11:11:37 134

134 已全部加載完成

電子發(fā)燒友App

電子發(fā)燒友App

評論