第10章 PlanAhead工具應用

PlanAhead工具是Xilinx提供的一個集成的、可視化的FPGA設計工具,它可以被應用于FPGA設計過程中的不同階段,常見的應用包括用PlanAhead進行RTL源代碼的開發、I/O引腳規劃、RTL網表分析、布局布線結果的分析、布局規劃,還可以在PlanAhead中將Chipscope核插入設計輔助調試,從而提高性能。也可以用PlanAhead嘗試各種實現屬性的不同設置,應用不同的時序約束、物理約束和布局規劃技術來提高設計性能。我們還可以將ISE的布局布線結果導入PlanAhead進行分析,定位關鍵路徑,找到影響設計性能的真正原因,并通過添加合理的約束、嘗試多種布局規劃策略以提高設計性能。

PlanAhead具有以下功能。

I/O引腳規劃。

RTL開發和分析。

綜合和實現。

設計分析。

靜態時序預估。

時序約束編輯器。

強大的布局規劃。

基于塊的邏輯設計。

值得一提的是,PlanAhead已經集成于ISE 11.x中,包括綜合前引腳規劃——I/O pin planning(Pre-Synthesis)、綜合后引腳規劃——I/O pin planning(Post-Synthesis)、綜合后區域/引腳/邏輯規劃——Floorplan Area/IO/Logic(Post-Synthesis)和實現后時序分析/設計規劃——Analyze Timing/Floorplan Design(Post-Implementation),它替代了以前常用的PACE和Floorplanner工具。

10.1 PlanAhead開發流程

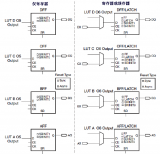

如圖10-1所示,PlanAhead設計流程主要包含三個部分,分別是基本設計流程、實驗流程和設計分析/布局規劃流程。下面分別簡單介紹。

基本設計流程(Base Flow):此流程允許設計者導入RTL源文件,再對其進行綜合、實現和結果分析。如果希望進行設計分析和布局規劃,就要使用設計分析與布局規劃流程。

實驗流程(Run Experimentation Flow):設計者可以應用不同的設計策略,使用多種綜合、實現屬性的組合,嘗試進行多個綜合或實現過程。PlanAhead工具提供了多種不同的實現策略,它也允許設計者自定義策略。例如,設計者可以在綜合階段指定面積優化、速度優化,或者功耗優化策略,運行多個綜合過程,產生不同綜合策略下的綜合結果,再對其進行分析。設計者也可以在實現階段,通過設置不同的翻譯、映射、布局布線屬性,產生多種實現結果。

設計分析與布局規劃流程(Analysis & Floorplanning Flow):PlanAhead可以對綜合后網表進行分析,對邏輯資源、引腳進行布局規劃,還可以將ISE的實現結果導入PlanAhead進行分析和布局規劃。

圖10-1 PlanAhead設計流程

下面會對各種設計流程做詳細的介紹。

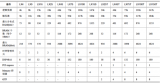

10.2 PlanAhead輸入、輸出文件

PlanAhead的輸入文件:

RTL Source File:源文件,包括Verilog/VHDL等。

Xilinx Cores (NGC / NGO):Xilinx核網表文件。

XST Constraint Files (XCF):XST約束文件。

I/O Port Lists (CSV):I/O引腳列表文件,CSV格式。

I/O Port Lists (HDL - Verilog or VHDL):I/O引腳列表文件,HDL格式。

Top-Level Netlists (EDIF):頂層網表,EDIF格式。

Module-Level Netlists (EDIF):模塊網表,EDIF格式。

Top-Level Netlists (NGC):頂層網表,NGC格式。

Constraint Files (UCF / NCF):約束文件,UCF/NCF格式。

Xilinx ISE Placement Results (NCD/XDL):Xilinx ISE布局結果,NCD/XDL格式。

Xilinx TRCE Timing Results (TWX/TWR):時序分析報告。

PlanAhead輸出報告:

I/O Pin Assignment (CSV):I/O引腳約束文件,CSV格式。

I/O Pin Assignment (RTL - Verilog or VHDL):I/O引腳約束文件,HDL格式。

Log File (planAhead.log):PlanAhead日志文件,包含了運行PlanAhead命令產生的信息內容,可以運行Window→View Log File打開此文件。

Journal File (planAhead.jou):Tcl命令文件。

Error Log Files (planAhead_pidxxxx.debug & hs_err_pidxxxx.log):錯誤日志文件。

DRC Results (results_x_drc.txt):DRC文本文件。

TimeAhead Results (Excel file):時序規劃文件。

Netlist Module, Pblock, and Clock Region Statistics Reports:網表模塊、物理塊、時鐘域統計報告。

SSN Analysis Report:SSN分析報告。

WASSO Analysis Reports:WASSO分析報告。

PlanAhead環境設置信息:

View Display Options File (planAhead.ini &

.patheme):顯示PlanAhead初始化文件,PlanAhead工具的顯示屬性等設置保存在此文件中。

Window Layout Files (.layout):PlanAhead的窗口布局配置文件。

Shortcut Schema (default.xml):PlanAhead的快捷鍵定義文件。

Strategy Files (.psg):PlanAhead實現策略配置文件。

PlanAhead項目數據文件:

Project Directory (

):項目路徑,保存PlanAhead項目文件、項目數據文件和ISE實現結果。

Project File (

.ppr):項目文件,保存PlanAhead狀態,項目的網表信息以及各種布局規劃信息保存在其中。

Project Data Directory (

.data):項目數據路徑,包含了項目中的所有規劃信息(Floorplan)和與網表相關的數據。

Project Data - Netlist Subdirectory (netlist):網表子目錄,對于基于RTL的設計,其中保存了每一個綜合網表;對于基于網表的設計,其中保存了導入的網表,包括所有的NGC網表。

Project Data - Floorplan Subdirectories and Files ():Floorplan子目錄和文件。

Project RTL Directory (

.srcs):RTL源文件目錄,保存了所有導入到項目中的HDL文件。

用于ISE實現的輸出文件:

Run Directory (

.runs):在PlanAhead中可以運行多個ISE實現進程,每個實現結果都會存儲在一個獨立的“運行目錄”中,其中包括EDIF網表和ucf約束文件。

EDIF Netlists (.edf):可以導出EDIF格式的ASIC文件,運行下面任一命令,可以導出此網表,包括:

Run Implementation and Launch Runs (PlanAhead):自動導出EDIF和UCF文件。

File→Export Netlist:導出網表。

File→Export Pblocks:導出指定的Pblock網表EDIF文件及UCF文件,以便進行模塊重用。

File→Export IP:導出指定IP的EDIF和UCF文件,以便進行IP重用。

Xilinx Cores (.ngc/.ngo):Xilinx的IP核網表文件。

ChipScope Core Netlists (.ngc):ChipScope核網表文件。

Constraint Files (.ucf):ucf約束文件。

ISE Launch Scripts (jobx.bat/sh & runme.bat/sh & ..rst):ISE啟動腳本文件。

電子發燒友App

電子發燒友App

評論