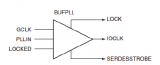

Vrtex-6 HXT器件內的GTH模塊比GTX有更高的線速率,用它可以實現最高性能的高速串行收發器。GTH具有如下特性。

靈活的SERDES 支持多速率應用。

實現40G 和100G 協議等。

功能強大的發射預加重和接收均衡器。

集成式“變速箱”實現了靈活編碼:8B/10B、64B/66B。

低功耗:~220mW(典型值)@10.3125Gbit/s。

符合常見標準的要求,如10/40/100G 以太網、PCI Express、OC-48、XAUI、SRIO 和HD-SDI。

5.1.9 以太網(Ethernet MAC)模塊

Virtex-6器件內置以太網MAC,不需要消耗可編程邏輯資源即可提供無縫的芯片到芯片連接。以太網媒體訪問控制器(MAC)內核支持10/100/1000Mbit/s數據速率,兼容UNH驗證標準并且具有互操作能力,設計符合IEEE 802.3規范的要求,可以單獨運行在1000Mbit/s、100Mbit/s 和10Mbit/s 模式,或者配置成三態模式。支持IEEE標準的MII、GMII和RGMII協議,減少外部物理接口的總線寬度。

圖5-38 所示為以太網MAC 的結構框圖。

圖5-38 以太網MAC 的結構框圖

主機可以通過主機總線或者設備控制寄存器(DCR)總線與以太網MAC 互聯。

物理接口能配置成MII、GMII、RGMII、SGMII 或100BASE-X,但是根據所選擇的物理接口配置,只有一套TX和RX接口被激活。

EMAC有一個可選的管理數據輸入/輸出接口(MDIO),可以訪問外部PHY 的管理寄存器和EMAC內部的物理接口管理寄存器(僅在1000BASE-X 或SGMII 模式配置下有效)。

EMAC輸出統計向量包含了以太網發送和接受數據通路上的幀信息。復用統計向量以減少與外界連接時所需要的引腳數。在FPGA中實現統計IP(Statistics IP)以累計以太網MAC收發數據通路的統計信息。

Virtex-6的EMAC的功能框圖如圖5-39所示。

圖5-39 以太網MAC的功能框圖

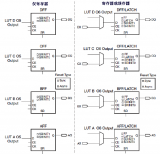

客戶端接口。包含了連接EMAC接受發送引擎的用戶發射接收接口,客戶端接口的數據寬度可以配置為8位或者16位,默認為8位。其中的流控制接口允許客戶控制物理層停止發送幀,直到客戶端有能力接受更多幀。EMAC的流量控制根據IEEE 802.3-2005標準設計,以太網MAC可以在檢測到有效的暫停幀之后,暫停和重啟幀傳輸,EMAC通過發送一定時間的暫停幀實現流量控制。圖5-40所示為流量控制結構圖。

?

圖5-40 流量控制結構圖

EMAC接口路徑上有個接收地址濾波器,它控制接受或拒絕輸入幀。

輸出統計向量包含了以太網發送和接受數據通路上的幀統計信息。發送統計向量TX_STATISTICS_VECTOR包含發送幀的統計信息,由32位向量和內部信號組成。接受統計向量RX_STATISTICS_VECTOR包含接受幀的統計信息,由28位向量和內部信號組成。Xilinx CORE Generator軟件免費提供了一個外部統計模塊,該統計模塊對以太網MAC的發送和接收數據通路上的所有統計信息進行累加。

主機/DCR總線接口。通過主機接口可以訪問EMAC配置寄存器、EMAC地址濾波寄存器、PCS/PMA子層寄存器,還可以驅動MDIO接口控制外部設備。可以通過通用主機總線或者DCR總線(當與處理器連接時)對EMAC主機接口進行訪問。圖5-41所示為主機接口內部結構圖。Xilinx XPS工具提供了XPS_LL_TEMAC軟核通過PLB總線控制EMAC。PLB和DCR總線之間可以通過橋切換。

圖5-41 主機接口內部結構圖

MDIO接口。在配置成1000BASE-X或SGMII模式下,主機接口可訪問EMAC中的PCS管理寄存器。主機接口也可通過MDIO接口訪問外部PHY設備。在MDIO使能,而主機接口不使能的情況下,外部設備也可以在配置成1000BASE-X或SGMII的模式下訪問EMAC中的PCS管理寄存器。

物理端接口。以太網MAC的物理接口,可以配置為媒體獨立接口(MII)、吉比特媒體獨立接口(GMII)、簡化的吉比特媒體獨立接口(RGMII)、串行吉比特媒體獨立接口(SGMII)、1000BASE-X。MII、GMII和RGMII是并行接口,它們通常連接到一個外部物理層(PHY)芯片以提供速率為10/100/1000Mbit/s的BASE-T功能,同時它還支持速率為10/100Mbit/s的半雙工操作以及各種速率條件下的全雙工操作。SGMII和1000BASE-X是串行接口,它們使用以太網MAC中的PCS和PMA部分,它們連接到Virtex-6 RocketIO GTX/GTH串行收發器。當與并行接口一起使用時,SGMII提供了速率為10/100/1000Mbit/s的全雙工BASE-T功能。該串行接口大大減少了與外部PHY芯片相連的引腳數量。當將EMAC配置成1000BASE-X模式時,PCS/PMA 模塊與RocketIO 收發器一起工作,能夠提供與吉比特轉換器

(GBIC)或者小型可插式(SFP)光纖收發器進行直接連接所需要的所有功能。這可以避免1000BASE-X 網絡應用所需的外部PHY 芯片。配置為MII/GMII/RGMII 模式時,可以利用標準IO 訪問外部物理芯片PHY;配置為1000BASE-X 或SGMII 模式時,MAC 中的PCS/PMA 子模塊使能,EMAC 通過PCS/PMA 子模塊連接串行收發器GTX。

時鐘管理模塊。此模塊自動根據以太網MAC 的速度(10Mb/s、100Mb/s 或1000Mb/s)和模式(GMII、MII、RGMII、SGMII 和1000BASE-X)配置正確的輸出時鐘。

設計中可以調用以太網MAC 的原語或者使用CoreGen 工具配置EMAC 參數來使用EMAC 模塊。

5.1.10 PCIe 端點模塊

PCIe2.0 標準對滿足高性能、低功耗應用的需求非常關鍵,特別是在電信、服務器、高端視頻市場。針對越來越多的PCIe 的應用,Virtex-6 FPGA 中嵌入了第二代的PCIe 內核,該集成的第二代PCIe 模塊兼容PCI Express 2.0 標準,已經通過了1-8 通道配置的PCI-SIGPCI Express 2.0 版本兼容性與互操作性測試。

?

圖5-42 Virtex-6 中集成的PCI-E 核

Vrtex-6 FPGA 內的PCI Express 模塊實現了事務處理層、數據鏈路層和物理層功能,能夠以最低的FPGA 邏輯利用率提供完整的PCI Express 端點和根端口功能。內部結構如圖5-41 所示。

5.2 Virtex-6 LXT 型FPGA

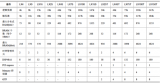

Vitex-6 LXT 平臺FPGA 的Virtex-6 LXT FPGA 針對邏輯優化,同時提供6.5Gbit/s GTX收發器、內置式PCIe 和三態以太網MAC。表5-15 為Virtex-6 LXT 器件列表。

表5-15 Virtex-6 LXT器件

5.3 Virtex-6 SXT型FPGA

Virtex-6 SXT面向DSP優化,DSP48E1 SLICE能實現超過 1000 GMACS的性能,可以高效地完成復雜的數字信號處理,同時提供 6.5Gbit/s GTX 收發器、內置式 PCIe 和三態以太網MAC。表5-16所示為Virtex-6 SXT器件列表。

表5-16 Virtex-6 SXT器件

5.4 Virtex-6 HXT型FPGA

Virtex-6 HXT FPGA 針對那些需要超高速串行連接功能的應用進行了優化,通過 6.5Gbit/s GTX收發器和支持11Gbit/s以上的線路速率的GTH收發器提供了業內最高的串行帶寬,從而實現了新一代分組和傳輸、交換機結構、視頻開關和成像設備。表5-17所示為Virtex-6 HXT器件列表。

表5-17 Virtex-6 HXT器件

Virtex-6 HXT器件的主要特性介紹如下。

(1) 實現了最高的串行帶寬。

帶寬最高的FPGA提供了低風險方法,能夠迅速為面向網絡、電信和成像行業中的橋接、轉換與群集的、功能強大的40Gbit/s和100Gbit/s應用進行原型開發和生產。

面向100GE MAC和100GE-Interlaken橋接的單FPGA解決方案。

面向40Gbit/s發射機應答器/復用轉發器的單FPGA解決方案。

利用FEC有效實現100Gbit/s發射機應答器/復用轉發器。

實現高級功能集成,如分組處理、加密和流量管理。

GTH多速率收發器多達24個,支持11Gbit/s以上的線路速率,用于連至×10Gbit/s、40Gbit/s和100Gbit/s網絡。

GTX多速率收發器多達48個,支持高達6.5Gbit/s的線路速率,實現了到早期ASIC、ASSP和背板的可靠接口。

(2) 新型GTH收發器支持11Gbit/s以上的線速率。

利用支持9.953Gbit/s~11.18Gbit/s線路速率的收發器構建高效的,到×10Gbit/s、40Gbit/s和100Gbit/s以太網網絡的鏈路。

單個Virtex-6 HXT FPGA內的GTH收發器多達24個。

低功耗:220mW(典型值),在10.3125Gbit/s時。

利用內置式Tx預加重、Rx線性均衡和Rx DFE實現芯片—芯片、芯片—光纖和10Gbit/s背板應用所需的信號完整性。

用于實現簡便易用性的復雜自適應均衡引擎。

保證符合常見標準的要求,如10/40/100Gbit/s以太網、OTU-/2/4、OC-192和SFP+。

集成式64B/66B和8B/10B編碼支持。

簡單而高度靈活的時鐘控制結構,實現了多協議設計。

(3) 利用6.5Gbit/s GTX收發器實現低功耗串行連接功能。

利用支持150Mbit/s~6.5Gbit/s線路速率的收發器連至早期ASIC、ASSP和背板。

功耗降低了25%:在6.5Gbit/s下,功率低于150mW(典型值)。

單個Virtex-6 HXT FPGA內的GTX收發器多達48個。

高度靈活的時鐘控制技術實現了獨立Rx和Tx操作,能夠有效地將某些應用的收發器數量加倍。

保證符合常見標準的要求,如10/40/100Gbit/s以太網、PCI Express、OC-48、XAUI、SRIO和HD-SDI。

第二代集成式PCI Express模塊和第三代三態以太網MAC模塊可以輕松實現常見接口。

5.5 小結

Virtex-6 FPGA是基于Virtex-5結構的,采用了第三代的ASMBL架構,比前一代產品功耗降低達50%,成本降低達20%。本章詳細介紹了Virtex-6系列器件的內部各模塊及其架構,以期讀者對Virtex-6系列FPGA有一個較深入的認識,并在此基礎上,提高設計者的設計優化能力。

電子發燒友App

電子發燒友App

評論