利用FPGA實(shí)現(xiàn)雙口RAM的設(shè)計(jì)及應(yīng)用

概述:為了在高速采集時(shí)不丟失數(shù)據(jù),在數(shù)據(jù)采集系統(tǒng)和

2010-04-16 14:08:36 11323

11323

RAM是FPGA中常用的基礎(chǔ)模塊,可廣泛用于緩存數(shù)據(jù)的情況,同樣它也是ROM,F(xiàn)IFO的基礎(chǔ)。本實(shí)驗(yàn)將為大家介紹如何使用FPGA內(nèi)部的RAM以及程序?qū)υ?b class="flag-6" style="color: red">RAM的數(shù)據(jù)讀寫操作。

2021-01-22 09:43:11 4794

4794

在選擇FPGA時(shí),關(guān)注LUT(Look-Up Table)和BRAM(Block RAM)是非常重要的,因?yàn)樗鼈兪?b class="flag-6" style="color: red">FPGA架構(gòu)中的兩個(gè)核心資源,對于設(shè)計(jì)的性能和資源利用至關(guān)重要。

2023-11-21 15:03:06 548

548

.互連線資源(Interconnect)4.嵌入式塊 RAM(BRAM)(Block RAM)5.底層內(nèi)嵌功能單元6.內(nèi)嵌專用硬核7.致謝FPGA 芯片整體架構(gòu)FPGA 芯片整體架構(gòu)如下所示,大體按照...

2021-07-30 08:10:06

、FPGA一般觸發(fā)器資源比較豐富,而CPLD組合邏輯資源更豐富。6、FPGA和CPLD的組成:FPGA基本有可編程I/O單元、基本可編程邏輯單元、嵌入式塊RAM、豐富的布線資源、底層嵌入功能單元和內(nèi)嵌專用硬核

2020-10-21 10:32:50

FPGA由6部分組成,分別為可編程輸入/輸出單元、基本可編程邏輯單元、嵌入式塊RAM、豐富的布線資源、底層嵌入功能單元和內(nèi)嵌專用硬核等。

2019-05-24 06:15:05

利用FPGA設(shè)計(jì)雙口ram,最大設(shè)計(jì)多的空間的?如果是cpld來實(shí)現(xiàn),空間是不是更小?如何去確定這個(gè)大小呢?求指導(dǎo)

2013-10-21 21:23:21

,實(shí)際上每一個(gè)系列的FPGA都有其相應(yīng)的內(nèi)部結(jié)構(gòu)),FPGA芯片主 要由6部分完成,分別為:可編程輸入輸出單元、基本可編程邏輯單元、完整的時(shí)鐘管理、嵌入塊式RAM、豐富的布線資源、內(nèi)嵌的底層功能單元和內(nèi)嵌

2017-05-09 15:10:02

功能(如RAM、時(shí)鐘管理和DSP)的硬核(ASIC型)模塊。如圖1-1所示(注:圖1-1只是一個(gè)示意圖,實(shí)際上每一個(gè)系列的FPGA都有其相應(yīng)的內(nèi)部結(jié)構(gòu)),FPGA芯片主要由6部分完成,分別為:可編程輸入輸出

2023-05-30 20:53:24

一.查找表(Look-Up-Table)的原理與結(jié)構(gòu)采用這種結(jié)構(gòu)的PLD芯片我們也可以稱之為FPGA:如altera的ACEX,APEX系列,xilinx的Spartan,Virtex系列等。查找表

2012-04-28 14:57:28

一、FPGA的基本結(jié)構(gòu) FPGA由6部分組成,分別為可編程輸入/輸出單元、基本可編程邏輯單元、嵌入式摸塊RAM、豐富的布線資源、底層嵌入式功能單元和內(nèi)嵌專用硬核等。 每個(gè)單元簡介如下: 1.

2019-09-24 11:54:53

一、FPGA的基本結(jié)構(gòu) FPGA由6部分組成,分別為可編程輸入/輸出單元、基本可編程邏輯單元、嵌入式摸塊RAM、豐富的布線資源、底層嵌入式功能單元和內(nèi)嵌專用硬核等。 每個(gè)單元簡介如下: 1.

2016-07-16 15:32:39

一、FPGA的基本結(jié)構(gòu) FPGA由6部分組成,分別為可編程輸入/輸出單元、基本可編程邏輯單元、嵌入式摸塊RAM、豐富的布線資源、底層嵌入式功能單元和內(nèi)嵌專用硬核等。 每個(gè)單元簡介如下: 1.

2016-08-23 10:33:54

一、FPGA的基本結(jié)構(gòu) FPGA由6部分組成,分別為可編程輸入/輸出單元、基本可編程邏輯單元、嵌入式摸塊RAM、豐富的布線資源、底層嵌入式功能單元和內(nèi)嵌專用硬核等。 每個(gè)單元簡介如下: 1.

2016-09-18 11:15:11

一、FPGA的基本結(jié)構(gòu) FPGA由6部分組成,分別為可編程輸入/輸出單元、基本可編程邏輯單元、嵌入式摸塊RAM、豐富的布線資源、底層嵌入式功能單元和內(nèi)嵌專用硬核等。 每個(gè)單元簡介如下: 1.

2016-10-08 14:43:50

我有8個(gè)Spartan 6 FPGA設(shè)計(jì)原型和一個(gè)外部DDR RAM。我使用Multi-Port-Memory-Controller并選擇bank 3進(jìn)行外部DDR-RAM連接。我的Spartan

2019-06-20 15:21:24

的Spartan,Virtex系列等。查找表(Look-Up-Table)簡稱為LUT,LUT本質(zhì)上就是一個(gè)RAM。 目前FPGA中多使用4輸入的LUT,所以每一個(gè)LUT可以看成一個(gè)有4位地址線的16x1

2008-05-20 09:46:10

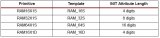

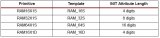

》, Volume I,Section I,3)。Cyclone III中的ram塊是M9k,每一塊中包含8192個(gè)存儲位,加上校驗(yàn)位共9216位,故稱M9k。每個(gè)ram塊可配置為表3-1中的各種模式

2015-09-05 18:59:57

請問版主,OKMX6UL-C2工業(yè)級開發(fā)板的方案四,8位地址,16位數(shù)據(jù)接口有對接ram或者FPGA的例程或者測試程序么?謝謝。

2022-01-11 07:52:59

嗨,為了調(diào)試系統(tǒng),我需要在系統(tǒng)運(yùn)行時(shí)動態(tài)讀取Block-RAM內(nèi)容....我只有JTAG線,我不能在FPGA中制作一個(gè)特定的塊用于讀取內(nèi)容并通過JTAG等發(fā)送它們。我可以使用ISMP 13.2作為

2019-06-11 07:36:08

STM32H743 有各種可用的 ram 塊,如下所示:DTCMRAM - 128kBITCMRAM - 64kBRAM_D1 - 512kBRAM_D2 - 288kBRAM_D3 - 64kB1

2023-02-06 06:19:29

大家好,我想在Spartan 3E XC3S250E中使用100Kbits Memrory(6400字深16位寬),根據(jù)數(shù)據(jù)表,它有216Kbits的總RAM(12個(gè)RAM塊)。數(shù)據(jù)表還說每個(gè)RAM

2019-02-27 09:16:11

本帖最后由 lpc2292 于 2013-2-27 20:24 編輯

“部分 I: 用 Spartan-3 系列 FPGA 進(jìn)行設(shè)計(jì)”第 1 章 “概述”第 2 章 “使用全局時(shí)鐘資源”第 3

2013-02-27 20:20:10

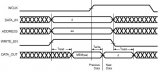

Vivado綜合可以理解多種多樣的RAM編寫方式,將其映射到分布式RAM或塊RAM中。兩種實(shí)現(xiàn)方法在向RAM寫入數(shù)據(jù)時(shí)都是采取同步方式,區(qū)別在于從RAM讀取數(shù)據(jù)時(shí),分布式RAM采用異步方式,塊RAM

2020-09-29 09:40:40

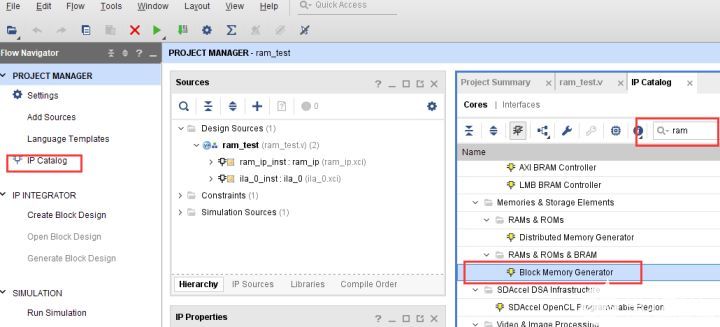

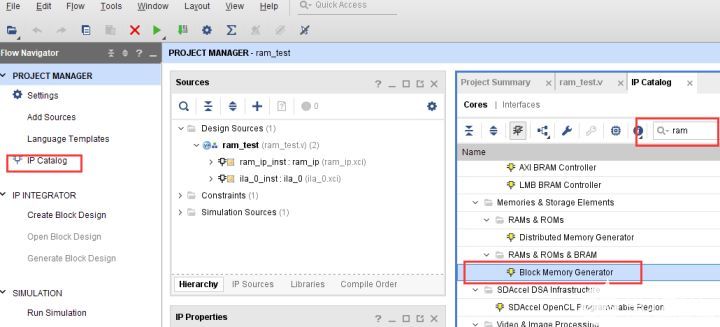

`Xilinx FPGA入門連載48:FPGA片內(nèi)RAM實(shí)例之RAM配置特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1新建源文件打開

2016-01-22 13:39:24

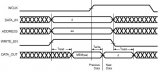

`Xilinx FPGA入門連載49:FPGA片內(nèi)RAM實(shí)例之功能仿真特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1 Xilinx庫

2016-01-25 12:55:23

Cortex-A9 處理器,但該器件上的 FPGA 數(shù)量存在差別,如表 1 所示:[td]Xilinx Zynq SoC可編程邏輯單元塊 RAM 的容量大小 (Mb)DSP 切片

2018-08-31 14:43:05

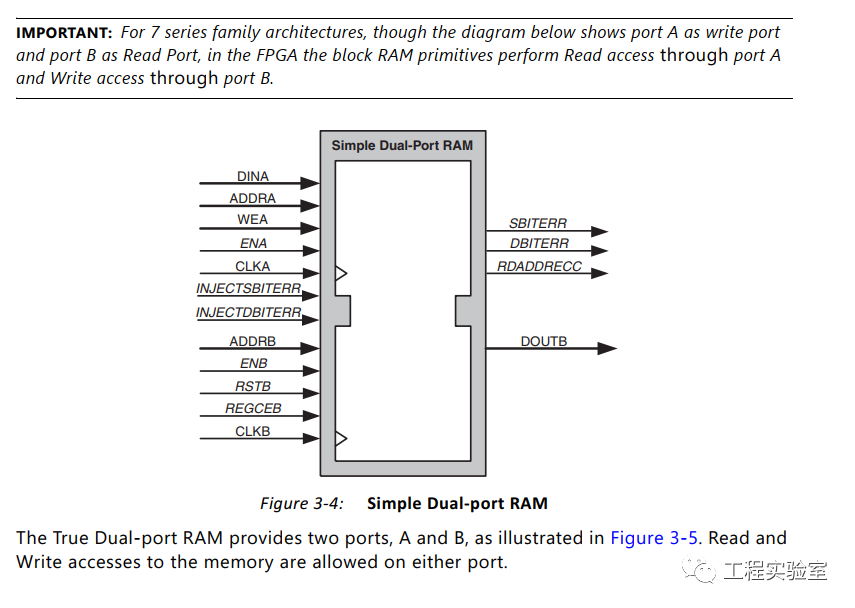

到每一個(gè)觸發(fā)器的時(shí)鐘、時(shí)鐘使能和時(shí)鐘緩存。 Artix-7系列塊存儲器Artix-7系列FPGA的嵌入式塊RAM為雙端口的36Kb塊RAM,位寬高達(dá)72bit。每個(gè)M36K有兩個(gè)完全獨(dú)立的端口,因此可以

2016-11-01 15:52:18

,有對開發(fā)套件感興趣的也可以加技術(shù)支持群472607506了解咨詢。 今天是視頻第十三講,主要講解FPGA芯片中提供的專用嵌入式塊RAM的應(yīng)用實(shí)例之一,也就是RAM IP核的使用。課程首先簡單介紹了

2015-10-23 12:47:16

兩塊TMS320F***通過雙端口RAM通訊,一塊寫入,另一塊讀出,應(yīng)該怎么連接

2016-04-21 10:35:14

我正在運(yùn)行Spartan 6 block ram的模擬。時(shí)鐘速度為100Mhz。塊ram的寫作運(yùn)作良好。我可以在內(nèi)存中看到數(shù)據(jù)。但是當(dāng)我讀取數(shù)據(jù)時(shí),輸出有2個(gè)時(shí)鐘的延遲。在塊ram用戶guidt中

2019-07-25 08:15:27

為什么要在顯示器應(yīng)用中使用FPGA?一種Spartan-3E顯示器解決方案板

2021-06-04 06:47:39

這里要談的是Xilinx的spartan-3系列FPGA的配置電路。當(dāng)然了,其它系列的FPGA配置電路都是大同小異的,讀者可以類推,重點(diǎn)參考官方提供的datasheet,畢竟那才是最權(quán)威的資料。

2019-10-10 06:16:52

什么是雙口RAM?基于FPGA的雙口RAM有哪些應(yīng)用?

2021-05-06 07:41:03

設(shè)計(jì)來增設(shè)全新的芯片功能,據(jù)此實(shí)現(xiàn)了芯片整體構(gòu)造的簡化與性能提升。下面英尚微電子介紹FPGA開發(fā)板內(nèi)部ram是如何操作的。 除邏輯外,所有新的FPGA都有專用的靜態(tài)ram塊,這些塊在邏輯元素之間分布并由

2020-09-10 11:11:57

`例說FPGA連載38:DDR控制器集成與讀寫測試之FPGA片內(nèi)RAM概述特權(quán)同學(xué),版權(quán)所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1c0nf6Qc 我們所

2016-10-12 17:18:25

給大家分享一下關(guān)于Spartan6板子的使用心得。

2021-04-30 07:03:13

求大神分享一些關(guān)于spartan6套件試用心得

2021-04-15 06:42:05

嗨這是來自海得拉巴的kishore。我們正在設(shè)計(jì)一個(gè)系統(tǒng),我們使用的是XC6VSX475T ff1156 -1 FPGA。我們在這個(gè)FPGA中使用的是microblaze軟核處理器。我們的要求是將

2019-02-18 09:01:37

ram或block ram進(jìn)行設(shè)計(jì)的任何眾所周知的標(biāo)準(zhǔn)3.任何人都可以比較所需的參數(shù),例如127x8內(nèi)存的速度,功率和效率,以及內(nèi)存大小是否增加到512x8。請緊急回答

2020-03-23 07:17:45

的FPGA 都有其相應(yīng)的內(nèi)部結(jié)構(gòu)),FPGA 芯片主要由6 部分完成,分別為:可編程輸入輸出單元、基本可編程邏輯單元、完整的時(shí)鐘管理、嵌入塊式RAM、豐富的布線資源、內(nèi)嵌的底層功能單元和內(nèi)嵌專用硬件模塊

2018-08-23 09:14:59

FPGA入門嵌入式塊RAM使用為FIOF(First In First Out)單時(shí)鐘FIOF、雙時(shí)鐘FIOF(普通雙時(shí)鐘和混合寬度雙時(shí)鐘)由于單時(shí)鐘FIOF只有一個(gè)時(shí)鐘信號,所以可以在FPGA內(nèi)部中使用單時(shí)鐘FIOF用以其他模塊數(shù)據(jù)的緩存。...

2021-12-17 07:59:18

我們正在嘗試在Spartan 3器件中創(chuàng)建9個(gè)270個(gè)位置(每個(gè)8位)的RAM塊。這在合成期間失敗了。任何人都可以建議正確的方法嗎?以上來自于谷歌翻譯以下為原文We are trying

2019-05-15 14:06:41

E 系列中以18Kbits 為一塊,在規(guī)模最小的型號XC3S100E 上集成了4 塊這樣的內(nèi)存,如圖2 所示:圖2 Spartan-3E 系列FPGA 集成的Block RAM

2012-05-14 12:37:37

嗨,嗨,我想讓ise實(shí)現(xiàn)我的ram作為雙端口ram,它將有兩個(gè)讀端口(不需要或不使用寫端口)。我在這個(gè)過程中使用以下幾行process_read:process(clk,address1

2019-07-23 10:39:41

RAM是FPGA中常用的基礎(chǔ)模塊,可廣泛用于緩存數(shù)據(jù)的情況,同樣它也是ROM,F(xiàn)IFO的基礎(chǔ)。本實(shí)驗(yàn)將為大家介紹如何使用FPGA內(nèi)部的RAM以及程序?qū)υ?b class="flag-6" style="color: red">RAM的數(shù)據(jù)讀寫操作。1.實(shí)驗(yàn)原理Xilinx

2021-01-07 16:05:28

嗨,我正在使用Xilinx模板創(chuàng)建一個(gè)通用的True Dual端口ram。目標(biāo)是在每個(gè)設(shè)計(jì)中使用此RTL,以便在切換FPGA系列時(shí)簡化器件對器件的可靠性。從V5到K7。我修改了tempelate以

2020-07-23 10:14:09

你好xilinx用戶,我正在使用FPGA實(shí)現(xiàn)人工神經(jīng)網(wǎng)絡(luò)。我想知道如何在FPGA中使用0.784,1.768..etc等數(shù)字。表示這些數(shù)字的方法是什么。以上來自于谷歌翻譯以下為原文hello

2019-03-04 13:38:31

09 C4 30 70 00 64 16 0D 0A我希望在FPGA打開后將此十六進(jìn)制字符串存儲在塊RAM中,以便FPGA可以在需要時(shí)檢索此字符串有沒有辦法用for循環(huán)來實(shí)現(xiàn)這個(gè)?問候費(fèi)薩爾以上

2019-06-14 07:54:16

套件的塊rams中,另一個(gè)塊ram用于存儲另一個(gè)與R G B陣列相同的可變溫度。Xilinx已經(jīng)提到XC5LX110T具有5328Kb的內(nèi)部RAM存儲器,因此我必須使用多大的圖像來確保使用內(nèi)部DDR

2019-01-30 08:36:28

我為哈希程序編寫了一個(gè)代碼,它在合成時(shí)顯示內(nèi)部錯(cuò)誤。但模擬效果很好。有人請告訴我正確的解決方案。如果我在always塊中使用多個(gè)for循環(huán)(2維),這是一個(gè)問題嗎?提前致謝......

2019-10-24 08:31:04

我有一個(gè) ESP32-S3-WROOM1 模塊,其中包含一個(gè)內(nèi)部 SPI 2Mo RAM。我在 Eclipse 下開始了一個(gè)新項(xiàng)目,但我不知道如何在我的項(xiàng)目中聲明 2Mo RAM。此外,我不知道

2023-03-01 06:37:03

大家好, 我使用Ultrascale Virtex Devices和Vivado工具, 在ASIC RAM中,ther是一個(gè)單獨(dú)的奇偶校驗(yàn)寫使能位,但在FPGA RAM中沒有單獨(dú)的Pariaty寫使能位。 如何實(shí)現(xiàn)ASIC RAM奇偶校驗(yàn)寫入啟用ino FPGA RAM。謝謝娜文G K.

2020-04-24 09:37:05

我如何知道 S32K144 中使用了多少 RAM?RAM = Data + Bss,如何知道軟件運(yùn)行時(shí)S32K144使用了多少RAM?S32K144 現(xiàn)在在不固定的點(diǎn)重新啟動。

2023-03-23 07:04:20

親愛的大家我現(xiàn)在正在使用virtex5,我使用核心生成器IP制作塊ram所以我將這些文件添加到項(xiàng)目(.vhd)以模擬代碼IP的聲明也已完成(將其添加為組件)但是在讀取操作期間,我確定了塊ram的地址

2020-06-11 09:47:52

學(xué)習(xí)fpga心得體會

2012-09-14 09:02:40

嵌入式塊ram使用為rom(只讀存儲器)使用PC端的signaltap ii軟件與FPGA內(nèi)部搭建的片上邏輯分析儀連接,時(shí)刻查看FPGA內(nèi)部的信號。使用Quartus II軟件中提

2021-12-17 08:00:26

大家好,我曾使用Xilinx CoreGen生成塊RAM,然后在我的設(shè)計(jì)中使用了它的實(shí)例化。該RAM適用于讀寫操作 - 在RTL sim中得到驗(yàn)證。我現(xiàn)在想要的是在訪問此內(nèi)存時(shí)相應(yīng)地轉(zhuǎn)儲此特定RAM

2019-03-29 12:19:26

字節(jié)的 RAM 組成。FPGA 中存在的塊 ram 的數(shù)量取決于 FPGA 的先進(jìn)程度。例如,Spartan 6 FPGA 擁有比 Spartan 3更大的塊 RAM。塊 RAM 應(yīng)該用于大型的實(shí)現(xiàn)。這兩種

2022-04-03 11:20:18

新手入門FPGA領(lǐng)域心得

2015-11-30 20:59:18

的問題是:所有3種類型都可以在FPGA Spartan 6中使用,如果它們中的任何一種都有利于以更簡單的方式實(shí)現(xiàn)。謝謝您的幫助。

2019-08-05 07:38:33

小弟最近在設(shè)計(jì)一款雙核采集系統(tǒng)使用ep1c6q240c8和tms320vc5509a雙核,兩塊芯片使用外部雙口RAM進(jìn)行數(shù)據(jù)傳輸,請教各位大神ep1c6q240c8怎么和雙口RAM連接啊???????????????????????

2012-11-05 10:42:41

msp430的特點(diǎn)是什么?求大神分享關(guān)于msp430系列單片機(jī)的一些入門心得

2021-09-30 07:08:00

hithanx for ur support.I還有一個(gè)查詢。如何從塊ram(VirtexIIxc2v6000)讀取值。是否必須在未初始化的寄存器中讀取值?這意味著每次我必須創(chuàng)建一個(gè)新變量讀取

2020-05-29 16:40:15

XC6SLX45T-3FGG484C FPGA - 現(xiàn)場可編程門陣列系列提供了成本、功率和性能的最佳平衡,提供了一種新的、更高效的雙寄存器6輸入查找表(LUT)邏輯和豐富的內(nèi)置系統(tǒng)級塊選擇。其中

2022-08-04 11:47:34

為了在高速采集時(shí)不丟失數(shù)據(jù),在數(shù)據(jù)采集系統(tǒng)和CPU之間設(shè)置一個(gè)數(shù)據(jù)暫存區(qū)。介紹雙口RAM的存儲原理及其在數(shù)字系統(tǒng)中的應(yīng)用。采用FPGA技術(shù)構(gòu)造雙口RAM,實(shí)現(xiàn)高速信號采集系

2010-02-11 11:20:27 69

69 基于Actel FPGA 的雙端口RAM 設(shè)計(jì)雙端口RAM 芯片主要應(yīng)用于高速率、高可靠性、對實(shí)時(shí)性要求高的場合,如實(shí)現(xiàn)DSP與PCI 總線芯片之間的數(shù)據(jù)交換接口電路等。但普通雙端口RAM 最大

2010-11-15 17:44:19 82

82 在現(xiàn)代邏輯設(shè)計(jì)中,FPGA占有重要的地位,不僅因?yàn)榫哂袕?qiáng)大的邏輯功能和高速的處理速度,同時(shí)因?yàn)槠鋬?nèi)部嵌有大量的可配置的塊RAM,使其得到了廣泛地應(yīng)用,例如FFT算法的實(shí)現(xiàn)等。

2011-09-27 17:07:12 54

54 然后調(diào)用sinplify,對其進(jìn)行綜合,結(jié)果很不順利。首先是synplify報(bào)不支持器件,才發(fā)現(xiàn)synplify 9.6.2是2008年的產(chǎn)品,比Spartan6器件還要老。更新到Synplify Pro D-2010.03之后,器件是支持了,但是一綜合就報(bào)錯(cuò)停止了,卻不提示有什么錯(cuò)誤。

2017-02-11 12:49:40 2571

2571 帶有異步寫/同步讀的SRAM,其中的同步讀取可以使用與分布式RAM相關(guān)聯(lián)的觸發(fā)器實(shí)現(xiàn)。

2017-02-11 13:54:59 2160

2160

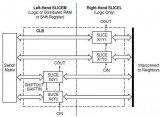

在賽靈思Spartan-3、3E等系列的FPGA中,其邏輯單元CLB中一般含有不同數(shù)量的單端口RAM(SRAM)或者雙端口RAM(DRAM),這里的“單”或者“雙”是由我們開發(fā)人員定義的。

2017-02-11 13:56:11 6348

6348

前面簡要介紹了Spartan-3系列FPGA中分布式RAM的基本特性。為什么不從更高級的Virtex系列入手呢?我仔細(xì)看了一下各個(gè)系列的介紹、對比,Spartan系列基本就是Virtex系列的精簡版,其基本原理是一樣的,所以從簡單的入手來融會貫通未嘗不是一個(gè)好辦法。

2017-02-11 13:57:40 1176

1176

前面講了分布式RAM的方方面面,下面以RAM_16S為例,分別給出其在VHDL和Verilog HDL下面的模板代碼(在ISE Project Navigator中選擇 Edit---

2017-02-11 13:59:33 1323

1323 FPGA內(nèi)部的RAM M9K

2017-04-07 11:40:04 4

4 FPGA中RAM的使用探索。以4bitX4為例,數(shù)據(jù)位寬為4,深度為4。

2018-03-28 17:07:28 9726

9726

大家好,又到了每日學(xué)習(xí)的時(shí)間了,今天我們來聊一聊在FPGA設(shè)計(jì)中RAM的兩種使用方法,RAM是用來在程序運(yùn)行中存放隨機(jī)變量的數(shù)據(jù)空間,使用時(shí)可以利用QuartusII的LPM功能實(shí)現(xiàn)RAM的定制

2018-06-08 11:30:28 19562

19562 本指南是描述所有Spartan-6 FPGA中可用的Spartan?6 FPGA塊RAM的技術(shù)參考。塊RAM用于高效的數(shù)據(jù)存儲或緩沖,用于高性能狀態(tài)機(jī)或FIFO緩沖,用于大移位寄存器、大查找表或ROM。

2019-02-15 16:38:59 13

13 RAM。 今天咱們就聊一聊7系列FPGA里面的Block RAM。 在7系列FPGA里面,每個(gè)Block RAM最

2020-11-23 14:08:43 7379

7379

本文檔的主要內(nèi)容詳細(xì)介紹的是FPGA的RAM存儲資源詳細(xì)資料說明包括了:1、 FPGA存儲資源簡介,2、 不同廠家的 Block RAM 布局,3、 塊 RAM 和分布式 RAM 資源,4、 Xilinx Block RAM 架構(gòu)及應(yīng)用

2020-12-09 15:31:00 10

10 本文檔的主要內(nèi)容詳細(xì)介紹的是FPGA硬件基礎(chǔ)之FPGA的RAM存儲課件和工程文件。

2020-12-10 15:27:00 30

30 在FPGA中block ram是很常見的硬核資源,合理的利用這些硬件資源一定程度上可以優(yōu)化整個(gè)設(shè)計(jì),節(jié)約資源利用率,充分開發(fā)FPGA芯片中的潛在價(jià)值,本文結(jié)合安路科技FPGA做簡單總結(jié),說明基本原理。

2020-12-24 14:28:09 916

916 FPGA可以調(diào)用分布式RAM和塊RAM兩種RAM,當(dāng)我們編寫verilog代碼的時(shí)候如果合理的編寫就可以使我們想要的RAM被綜合成BRAM(Block RAM)或者DRAM(Distributed

2020-12-30 16:27:52 9

9 RAM是FPGA中常用的基礎(chǔ)模塊,可廣泛用于緩存數(shù)據(jù)的情況,同樣它也是ROM,F(xiàn)IFO的基礎(chǔ)。本實(shí)驗(yàn)將為大家介紹如何使用FPGA內(nèi)部的RAM以及程序?qū)υ?b class="flag-6" style="color: red">RAM的數(shù)據(jù)讀寫操作。

2022-02-08 15:50:49 12183

12183

RAM是FPGA中常用的基礎(chǔ)模塊,可廣泛用于緩存數(shù)據(jù)的情況,同樣它也是ROM,F(xiàn)IFO的基礎(chǔ)。本實(shí)驗(yàn)將為大家介紹如何使用FPGA內(nèi)部的RAM以及程序?qū)υ?b class="flag-6" style="color: red">RAM的數(shù)據(jù)讀寫操作。

2021-03-15 06:09:45 14

14 電子發(fā)燒友網(wǎng)站提供《Logos系列FPGA專用RAM模塊(DRM)用戶指南.pdf》資料免費(fèi)下載

2022-09-26 09:31:40 9

9 在FPGA 邏輯設(shè)計(jì)中經(jīng)常用到的數(shù)據(jù)存儲方式有ROM、RAM和FIFO,根據(jù)不同的應(yīng)用場景選擇不同的存儲方式。Xilinx 平臺三種存儲方式在使用過程中的區(qū)別如下。

2023-08-22 16:12:47 1380

1380

FPGA在一個(gè)時(shí)鐘周期可以讀取多個(gè)RAM數(shù)據(jù)嗎?如何理解FPGA中存放程序的RAM? FPGA在一個(gè)時(shí)鐘周期可以讀取多個(gè)RAM數(shù)據(jù) FPGA中的RAM是FPGA中存儲數(shù)據(jù)的主要形式之一,許多FPGA

2023-10-18 15:28:20 598

598 FPGA雙口RAM的使用主要涉及配置和使用雙端口RAM模塊。雙端口RAM的特點(diǎn)是有兩組獨(dú)立的端口,可以對同一存儲塊進(jìn)行讀寫操作,從而實(shí)現(xiàn)并行訪問。

2024-03-15 13:58:14 81

81

電子發(fā)燒友App

電子發(fā)燒友App

評論