Verilog HDL是一種硬件描述語言(HDL:Hardware Discription Language),Verilog HDL語言是一種以文本形式來描述數字系統硬件的結構和行為的語言,用它可以表示邏輯電路圖、邏輯表達式,還可以表示數字邏輯系統所完成的邏輯功能。

Verilog HDL和VHDL是目前世界上最流行的兩種硬件描述語言,都是在20世紀80年代中期開發出來的。前者由Gateway Design Automation公司(該公司于1989年被Cadence公司收購)開發。兩種HDL均為IEEE標準

Verilog HDL語言學習用途就是在最廣泛的C語言的基礎上發展起來的一種件描述語言,它是由GDA(Gateway Design Automation)公司的PhilMoorby在1983年末首創的,最初只設計了一個仿真與驗證工具,之后又陸續開發了相關的故障模擬與時序分析工具。1985年Moorby推出它的第三個商用仿真器Verilog-XL,獲得了巨大的成功,從而使得Verilog HDL迅速得到推廣應用。1989年CADENCE公司收購了GDA公司,使得VerilogHDL成為了該公司的獨家專利。1990年CADENCE公司公開發表了Verilog HDL,并成立LVI組織以促進Verilog HDL成為IEEE標準,即IEEE Standard 1364-1995.

Verilog HDL的最大特點就是易學易用,如果有C語言的編程經驗,可以在一個較短的時間內很快的學習和掌握,因而可以把Verilog HDL內容安排在與ASIC設計等相關課程內部進行講授,由于HDL語言本身是專門面向硬件與系統設計的,這樣的安排可以使學習者同時獲得設計實際電路的經驗。與之相比,VHDL的學習要困難一些。但Verilog HDL較**的語法,也容易造成初學者犯一些錯誤,這一點要注意。

1. 首先講一下為什么需要學習硬件描述語言(Hardware Description Language,HDL)

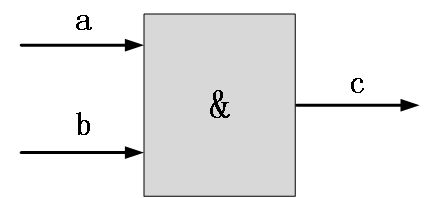

硬件描述語言是一種形式化方法描述數字電路和系統的語言。數字電路,應該是在大二上學期左右學習的課程,是一門非常重要的課程。現在大學的可能主要集中在邏輯門和小規模集成電路的講解上,很少涉及到HDL。當然,我們是可以通過一些列的74系列芯片構成我們想設計數字系統,但是當系統門數增多,設計就會變得非常復雜和困難——但是照樣有老外用這個方法實現了8位處理器,不過說實話,其成本和消耗的精力只能用來賺點眼球效應,而沒太多的實際意義。

隨著EDA技術發展,現在更多的是采用CPLD、FPGA、ASIC等來實現。首先采用HDL由抽象到具體、逐層描述設計思想,最后利用EDA工具進行仿真、綜合,轉換成門級電路網表,接下來再用CPLD/FPGA/ASIC自動布局布線工具把網表轉換成具體電路布線結構的實現(這個概念可能對新手有一定難度,打個比方就好像是選了一堆適用的74芯片,然后再進行了連線)。

現在的數字系統和數字信號處理發展相當快,掌握一門HDL,是理工科大學生的一個基本技能,現在的趨勢是甚至比掌握單片機更加重要。因為我們使用HDL,甚至可以自己編寫一個自己的單片機出來,然后在FPGA/ASIC上實現。

2. 選Verilog還是VHDL?

硬件描述語言的發展至今已經有20多年的歷史。現在主要的語言VHDL(Very High Speed Integerated Hardware Description Language)和Verilog HDL(Verilog Hardware Description Language)適應了歷史發展的趨勢和要求,先后成為IEEE標準。

由我看來,語言的出現就是用語言描述替代圖形化(元件拼湊)設計,把我們要實現的功能和思想用語言的形式寫出來,轉換成實際電路的工作就交給EDA工具去做,從而簡化了我們設計的工作,節約了開發的時間。也可以這么說,對于硬件不是特別明白的人也不必要去了解過多的關于電路的東西就可以開始做開發,對于科研人員可能更為有用。

選Verilog還是VHDL學習,這個問題有很多的爭論。

這個東西好像蠻重要的,因為剛開始就要選定用什么語言,要比較兩種語言的優劣,使用的情況等等,以后才能更好的學習。我只會Verilog,所以不敢亂彈兩者之間的優劣,想從另外一個角度來說一下。

這兩種語言都是用于數字電子系統設計的硬件描述語言,而且都已經是IEEE的標準。VHDL 1987年成為標準,而Verilog是1995年才成為標準的。這個是因為VHDL是美**方組織開發的,而Verilog是一個公司的私有財產轉化而來的。為什么Verilog能成為IEEE標準呢?它一定有其優越性才行,所以說Verilog有更強的生命力。

這兩者有其共同的特點:

1.能形式化地抽象表示電路的行為和結構;

2.支持邏輯設計中層次與范圍地描述;

3.可借用高級語言地精巧結構來簡化電路行為和結構;具有電路仿真與驗證機制以保證設計的正確性;

4.支持電路描述由高層到低層的綜合轉換;

5.硬件描述和實現工藝無關;

6.便于文檔管理;

7.易于理解和設計重用——這點很重要啊!

但是兩者也各有特點。Verilog HDL推出已經有20年了,擁有廣泛的設計群體,成熟的資源也比VHDL豐富(但是好像我在找資料的時候都是VHDL的資料多一些,這個和現在的氛圍有關)。Verilog更大的一個優勢是:它非常容易掌握,只要有C語言的編程基礎,通過比較短的時間,經過一些實際的操作,可以在2~3個月內掌握這種設計技術。而VHDL設計相對要難一點,這個是因為VHDL不是很直觀,需要有Ada編程基礎(我都不知道是什么,暈了),一般認為至少要半年以上的專業培訓才能掌握。

目前版本的Verilog HDL和VHDL在行為級抽象建模的覆蓋面范圍方面有所不同。一般認為Verilog在系統級抽象方面要比VHDL略差一些,而在門級開關電路描述方面要強的多。

近10年來,EDA界一直在對數字邏輯設計中究竟用哪一種硬件描述語言爭論不休,目前在美國,高層次數字系統設計領域中,應用Verilog和VHDL的比率是80%和20%;日本和***和美國差不多;而在歐洲VHDL發展的比較好。在中國很多集成電路設計公司都采用Verilog,但VHDL也有一定的市場。

夏宇聞老師推薦應該先學Verilog,然后再學習VHDL。我覺得也是,只會一門語言是不夠的,否則在交流上會出現問題,而且用原理圖的方法設計數字電路也是一個必備的能力,否則不能軟硬通吃,達到大牛的水平啊。

大學里面有的學校會講述VHDL,但是并不妨礙學習Verilog。

3. 需要一些什么書?

這個問題,可能不同的人回答有不同的答案,每個人推薦的書也不一樣。不過關于Verilog,夏宇聞老師絕對是中國的泰斗級人物,我推薦的幾本書都和他有一定的關系。這個不是因為我個人和他關系好,而是確實這幾本書不錯。我建議大家最好有紙版的書,一個方面是支持夏老師的辛勤工作,另外一個方面也是便于閱讀和學習。

(1)沒有學過數字電路的同學,建議首先購買一本STEPHEN BROWN編寫、夏老師翻譯的《數字邏輯基礎與VERILOG設計(原書第2版)》。這本書在【Altera FPGA/CPLD資料專版】有電子書可以下載。本書可以作為數字電路的課本,也講了Verilog的,是一本不可多得的好書。本來我這個學期準備在學校以這本書為教材開全校選修課的,結果領導不知道什么原因把這個課給卡擦了……

(2)有沒有學過數字電路的同學,都應該有一本《Verilog HDL數字設計與綜合(第二版) 》,該書由Samir Palnitkar 編著,夏老師翻譯。該書的英文原版被視為Verilog的經典著作,美國很多大學的研究生課程的課本,中文版我也看了一部分,覺得還是不錯的書,【Altera FPGA/CPLD資料專版】有中英文兩個版本的電子書。網上有很人攻擊這本書翻譯的不好,不過看了那些評論和書之后,自然有定論,流言自然會不攻自破。

(3)第三本是夏老師編著的《VERILOG數字系統設計教程(第2版)》。這本書在Altera FPGA/CPLD資料專版】有下載,我看過第一版我沒看過,現在這本書還經常翻翻,都已經被我弄得非常破舊了。這本書剛出來的時候國內還沒有很好的Verilog方面的書,我是托人在北京幫我買的(那會兒好像網上書店還沒有呢)。書中對于語法和實際應用都講的非常非常好,強烈建議大家好好閱讀和學習。

書就推薦這么多,可能還需要一些資料,否則光是語言,沒有實戰,不容易有實際的感受。后面我還會推薦一些資料和某些書的一些章節,到了具體的地方再說。

4. 硬件工具

在學習語言的同時,我覺得應該要學習硬件的使用,畢竟我們是為了設計硬件電路才學習語言的。在本站的教程專版有相應的硬件工具,可以從本站購得PCB自己焊接,也可以自己制作相應的電路模塊進行學習。

硬件上必須要花一些錢,不能總是覺得有些東西好像很貴,舍不得。其實現在更多的人寧愿把錢花在玩游戲、吃吃喝喝,也不肯把錢花在學習上。我很喜歡那種自己去找辦法學習知識,自己買硬件或做硬件學習的學生。我遇上這樣的學生,有時候還會主動給他們硬件來學習。而對于那種有惰性的學生,我覺得可能沒幾個老師會喜歡的。

5. 軟件

Altera公司的Quartus II,設計軟件。

Mentor Graphics公司的ModelSim,仿真軟件,Altera的軟件里面也有相應的AE版本。

其它的一些綜合工具、程序編寫工具,可以等到學習的差不多了再弄。

6. 資料篇

軟件的使用,我覺得最直接的方法是看廠商的Help,其次就是上面提到的有兩本書的附錄中也有相應的資料。

DE2板子的10個例子,在【FPGA與SOPC設計教程:DE2實踐 】這本書的第六章有中文版的翻譯,大家可以到下載區找這本書。

其它的學習資料或教程——我也準備寫這么個東西,但是一直在思考是該從編程、硬件應用還是數字邏輯的角度來進行講述,遲遲沒有動筆是因為把握不好方向,一旦方向錯了,會讓很多人走彎路,我可負不起這個責任。

其實,資料并不在多,關鍵是精,另外一個就是找的資料一定要看,不要以自己有多少資料為榮,應該是以自己看了多少資料為榮。

7. 學習的過程

學習的過程,每個人都不太相同。我以個人經驗隨便說兩句吧。

首先是軟件的使用,比如QuartusII的使用應該放在所有的學習之前(學過數字電路的同學,如果沒有學過的話,先把一些基本概念學一下,在學習到《數字邏輯基礎與VERILOG設計》的時候開始用原理圖設計的方法學習使用該軟件),然后就是學習Verilog了,建議在學習的過程中把書中的例子都用軟件做一次,也利用Quartus提供的仿真功能進行仿真。

基本的語法知識學習的同時,書上很多仿真的例子在Quartus里面并不能實行,這個時候就需要學習使用ModelSim了。

進一步學習Verilog的高級編程知識,利用軟件多做一些例子程序。

上面推薦的后兩本書看的差不多的時候(夏老師那本書的中級篇CPU設計之前的內容,另外那本第一部分結束),就可以到板子上編一些實際的應用程序了。這個時候就可以參考DE2那本書的幾個例子,或者是參考電路板上的硬件,針對不同的部件進行編程和驗證。

然后就是根據自己的興趣愛好和專業方向,找一個題目用Verilog去實現(或者找相關的老師,看他們手上有沒有這樣的方向,你可以去幫忙做點什么的),這個過程中需要學習更多其他方面的知識,這樣才能做成真正的應用系統。

這個時候可能手上的CPLD的資源可能就不那么夠了,也許就該用FPGA來做了。此外FPGA和CPLD還是有區別的,兩個器件應用的場合有所不同,這個在學習的過程中也要逐步積累這些知識和經驗。此外,還可以學習一些SOC方面的知識,這里不僅僅是指的Nios II。

后面繼續學習,不斷學習,持續學習——學習是一輩子的事情,不是花上那么幾個月你就能把所有的技能學到手,更多的時候是通過實踐不斷提升自己的能力,這就是所謂的實踐出真知。我想從大二開始學習到大三結束,兩年的時間基本能掌握這門技能,大四的畢業設計應該可以做出自己的優秀設計來。

電子發燒友App

電子發燒友App

評論