從制造的角度來講,FPGA測試是指對FPGA器件內(nèi)部的邏輯塊、可編程互聯(lián)線、輸入輸出塊等資源的檢測。完整的FPGA測試包括兩步,一是配置FPGA、然后是測試FPGA,配置FPGA是指將FPGA通過將配

2011-10-12 15:16:25 1414

1414

基于eFPGAsim的電機(jī)硬件在環(huán)測試系統(tǒng),是面向電驅(qū)HIL測試的高精度FPGA的解決方案,利用最新的eHS (Electric Hardware Solver)技術(shù)實(shí)現(xiàn),在獲得基于FPGA片上仿真

2017-08-09 10:52:21 2930

2930

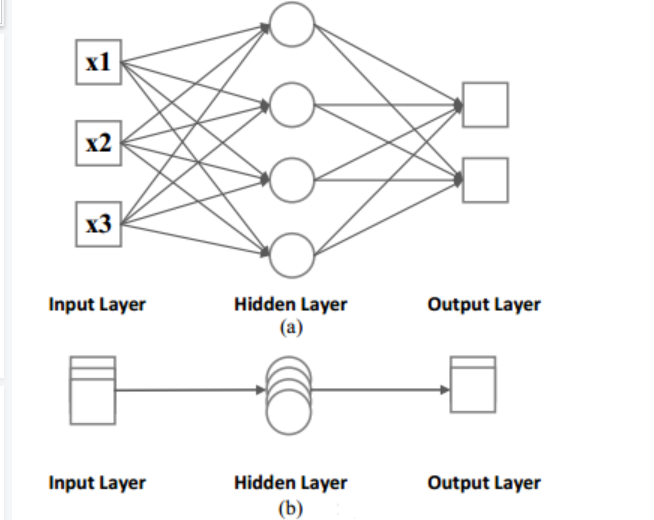

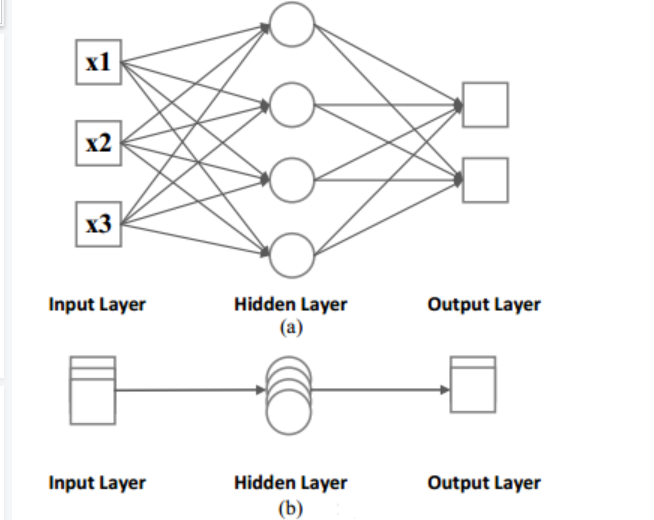

循環(huán)神經(jīng)網(wǎng)絡(luò) (RNN) 是一種深度學(xué)習(xí)結(jié)構(gòu),它使用過去的信息來提高網(wǎng)絡(luò)處理當(dāng)前和將來輸入的性能。RNN 的獨(dú)特之處在于該網(wǎng)絡(luò)包含隱藏狀態(tài)和循環(huán)。

2024-02-29 14:56:10 293

293

FPGA在嵌入式測試系統(tǒng)中的優(yōu)勢是什么?FPGA在嵌入式測試系統(tǒng)中的不足是什么?

2021-05-06 07:19:22

大容量、高速率和低功耗已成為FPGA的發(fā)展重點(diǎn)。嵌入式邏輯分析工具無法滿足通用性要求,外部測試工具可以把FPGA內(nèi)部信號與實(shí)際電路聯(lián)合起來觀察系統(tǒng)真實(shí)運(yùn)行情況。隨著FPGA技術(shù)的發(fā)展,大容量、高速

2019-08-07 07:50:15

的基礎(chǔ)上,給出了一種仿真調(diào)試方 案;利用該方案指出了其中若干邏輯錯誤并對其進(jìn)行修改,最終完成了修改后IP核的FPGA下載測試。1 OC8051結(jié)構(gòu)分析OpenCores網(wǎng)站提供的OC8051 IP核

2012-08-11 11:41:47

進(jìn)行了測試。該實(shí)現(xiàn)比嵌入在Zynq 7020 FPGA上的ARM Cortex-A9 CPU快了21倍。LSTM是一種特殊的RNN,由于獨(dú)特的設(shè)計(jì)結(jié)構(gòu),LSTM適合于處理和預(yù)測時間序列中間隔和延遲非常長

2018-07-31 10:11:00

上面介紹的是整個 FPGA 固件系統(tǒng)的實(shí)現(xiàn)方法,為了驗(yàn)證設(shè)計(jì)的正確性,還需要編寫一個測試平臺對整個系統(tǒng)進(jìn)行仿真。由于實(shí)際情況下 FPGA 是和 PDIUSBD12 進(jìn)行通信,所以在測試平臺中需要虛擬

2018-11-28 15:22:56

判斷配置是否成功,決定是否可以開始測試。如果配置成功,軟件則開始向被測FPGA發(fā)送測試激勵數(shù)據(jù)并讀回測試響應(yīng)保存在電腦中,由軟件對測試響應(yīng)進(jìn)行分析決定是否需要進(jìn)行下一次配置和測試流程。如果需要,在一定

2020-05-14 07:00:00

FPGA時序分析與約束(1)本文中時序分析使用的平臺:quartusⅡ13.0芯片廠家:Inter1、什么是時序分析?在FPGA中,數(shù)據(jù)和時鐘傳輸路徑是由相應(yīng)的EDA軟件通過針對特定器件的布局布線

2021-07-26 06:56:44

FPGA易測試性分析

2012-08-12 11:47:33

在進(jìn)行FPGA的設(shè)計(jì)時,經(jīng)常會需要在綜合、實(shí)現(xiàn)的階段添加約束,以便能夠控制綜合、實(shí)現(xiàn)過程,使設(shè)計(jì)滿足我們需要的運(yùn)行速度、引腳位置等要求。通常的做法是設(shè)計(jì)編寫約束文件并導(dǎo)入到綜合實(shí)現(xiàn)工具,在進(jìn)行

2023-09-21 07:45:57

RNN中支持的一些基本算子,如何對序列數(shù)據(jù)進(jìn)行組織

2022-08-31 10:01:30

DL之RNN:RNN算法相關(guān)論文、相關(guān)思路、關(guān)鍵步驟、配圖集合+TF代碼定義

2018-12-28 14:20:33

測試平臺,采用系統(tǒng)級指標(biāo)分析HDL實(shí)現(xiàn) 方案;通過FPGA在環(huán)仿真加速驗(yàn)證(圖1)。為什么在FPGA上建立原型?在FPGA上建立算法原型可以增強(qiáng)工程師的信心,使他們相信自己的算法在實(shí)際環(huán)境中的表現(xiàn)能夠

2020-05-04 07:00:00

嗨, 我正在尋找有關(guān)Virtex5-Q FPGA資格的信息。在Virtex5-Q FPGA上進(jìn)行了哪些資格測試?謝謝

2020-06-11 13:00:32

我對這部分記憶測試電路的分析把握不定,請各位大神幫我分析一下。

2020-11-09 14:50:46

網(wǎng)絡(luò)測試 NetWork 分析儀

2024-03-14 22:30:52

網(wǎng)絡(luò)測試 NetWork 分析儀

2024-03-14 22:30:52

現(xiàn)場測試 電源質(zhì)量和能量分析儀

2024-03-14 22:33:48

原文鏈接:http://tecdat.cn/?p=6585本文介紹了用于渦輪槳距角控制的永磁同步發(fā)電機(jī)(PMSG)和高性能在線訓(xùn)練遞歸神經(jīng)網(wǎng)絡(luò)(RNN)的混合模糊滑模損失最小化控制的設(shè)計(jì)。反向傳播學(xué)

2021-07-12 07:55:17

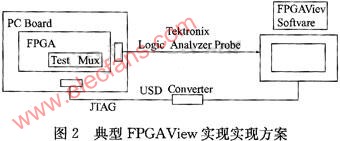

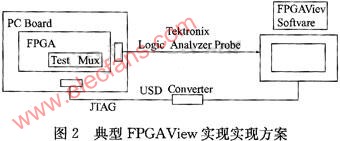

在設(shè)計(jì)基于FPGA的電子系統(tǒng)時,一般需要用示波器、邏輯分析儀等外部測試設(shè)備進(jìn)行輸入輸出信號的測試,借助測試探頭把信號送到測試設(shè)備上進(jìn)行觀察分析。當(dāng)然,前提是需要保留足夠多的引腳,以便能選擇信號來驅(qū)動

2019-08-19 08:03:56

本文根據(jù)當(dāng)前FPGA的高速總線測試和分析,提供了最新的方法和工具。

2021-05-11 06:24:02

FPGA可重復(fù)配置和測試系統(tǒng)結(jié)構(gòu)概述FPGA重復(fù)配置和測試的實(shí)現(xiàn)

2021-04-29 06:58:20

利用RNN進(jìn)行文章生成

2019-05-24 08:35:12

安捷倫公司數(shù)字測試資深技術(shù)/市場工程師 冀衛(wèi)東為滿足日益復(fù)雜的數(shù)字化系統(tǒng)的設(shè)計(jì)要求,FPGA的密度及復(fù)雜性也在急速增長,越來越多的系統(tǒng)或子系統(tǒng)功能在FPGA內(nèi)部實(shí)現(xiàn),其先進(jìn)的功能和高集成度使FPGA成為極具吸引力的解決方案,進(jìn)而也使得基于內(nèi)核的FPGA測試方案浮出水面。

2019-07-11 06:15:12

,不同的寄存器在時鐘脈沖的激勵下相互配合完成特定的功能,所以要保證不同的寄存器在同一時刻的時鐘脈沖激勵下協(xié)同工作,就需要進(jìn)行時序分析,通過分析得結(jié)果對FPGA進(jìn)行約束,以保證不同寄存器間的時序要求

2017-02-26 09:42:48

時不建議使用萬用表,建議使用示波器的平均值功能,并調(diào)節(jié)合適的檔位;B. 硬件設(shè)計(jì)中通常為了方便斷開電源,會在電源輸出進(jìn)FPGA之前添加磁珠或者電感,磁珠和電感會引入壓降,建議在磁珠和電感之后測試;如無

2022-09-27 08:00:00

信號處理功能在矢量信號分析儀上產(chǎn)生I和Q數(shù)據(jù)● 能夠在高速數(shù)字儀器上實(shí)時進(jìn)行圖案發(fā)生和矢量比較測試設(shè)備制造商現(xiàn)在開始向用戶開放FPGA以提供更多特殊應(yīng)用的優(yōu)化。為了幫助理解為何這是一個好的轉(zhuǎn)變,下面

2021-07-13 08:00:00

在測試應(yīng)用中使用FPGA的關(guān)鍵特性有哪些?開放式FPGA能否增加測試的靈活性?

2021-05-11 06:40:12

本文在分析OpenCores網(wǎng)站提供的一款OC8051IP核的基礎(chǔ)上,給出了一種仿真調(diào)試方案;利用該方案指出了其中若干邏輯錯誤并對其進(jìn)行修改,最終完成了修改后IP核的FPGA下載測試。

2021-05-08 06:22:32

本文選用FPGA實(shí)現(xiàn)數(shù)據(jù)處理、邏輯控制,充分利用PC機(jī),結(jié)合Labwindows圖形化上層應(yīng)用軟件界面生成的虛擬測試系統(tǒng)具有較強(qiáng)的競爭力。本系統(tǒng)在FPGA單板單片主控器件控制下,實(shí)現(xiàn)兩路獨(dú)立、幅值可控的信號發(fā)生器,一路虛擬存儲示波器,具有外部觸發(fā)信號和采樣時鐘的16路高速邏輯分析儀。

2021-05-12 06:58:02

本文提出了一種基于FPGA的誤碼率測試儀的方案,使用一片Altera公司的Cyclone系列的FPGA(EP1C6-144T)及相關(guān)的外圍電路,實(shí)現(xiàn)誤碼測試功能,主控計(jì)算機(jī)可以通過FPGA內(nèi)建的異步串行接口(UART)配置誤碼測試儀并讀取誤碼信息,由計(jì)算機(jī)完成誤碼分析。

2021-05-08 06:13:47

網(wǎng)絡(luò)分析儀在天線S參數(shù)測試方面有什么應(yīng)用?

2021-05-28 06:00:24

。DSP與FPGA孰優(yōu)孰劣的討論由來已久,筆者以智能交通視頻分析為主線,分析FPGA相較DSP方案,在攻克智能交通視頻分析難題中將發(fā)揮何種優(yōu)勢。基于FPGA的視頻分析解決方案打造智能交通“攻城利器

2013-12-16 19:15:49

本文介紹了用于渦輪槳距角控制的永磁同步發(fā)電機(jī)(PMSG)和高性能在線訓(xùn)練遞歸神經(jīng)網(wǎng)絡(luò)(RNN)的混合模糊滑模損失最小化控制的設(shè)計(jì)。反向傳播學(xué)習(xí)算法用于調(diào)節(jié)RNN控制器。PMSG速度使用低于額定速度

2021-07-12 06:46:57

概括了這個過程。圖6.4圖6.4演示了以下內(nèi)容:· RNN如何通過展開和圖像來工作;· 狀態(tài)如何以遞歸方式傳遞給同一模型。到現(xiàn)在為止,我們只是了解了RNN的功能,但并不知道它是如何工作的。在了解其

2022-07-20 09:27:59

了邏輯分析儀在EDA教學(xué)中的應(yīng)用,通過OLA2032B邏輯分析儀調(diào)試基于FPGA的LCD顯示控制設(shè)計(jì)方案的實(shí)驗(yàn)。在測試的過程中,我們可以發(fā)現(xiàn)邏輯分析儀在基礎(chǔ)教學(xué)中起著很重要的作用,比示波器更適合

2017-10-19 09:07:43

可大顯身手。 輻射發(fā)射測量 頻譜分析儀是測試設(shè)備輻射發(fā)射必不可少的工具,它與適當(dāng)?shù)慕涌谙噙B就可用于EMI自動測量。大多數(shù)情況下被測設(shè)備在第一次測試時都不能滿足人們的期望值,因此,診斷電磁干擾源并指出

2022-07-12 10:55:35

概述EasyGo FPGA Solver是EasyGo開發(fā)的專門部署在FPGA 硬件上的解算器軟件。根據(jù)不同的應(yīng)用需求,會有不同的FPGA Solver 選擇

2022-05-19 09:21:43

本文運(yùn)用黑盒測試的基本理論,提出了FPGA邏輯設(shè)計(jì)的測試模型,分析了FPGA邏輯設(shè)計(jì)的基本方法和步驟,最后結(jié)合一個實(shí)際項(xiàng)目說明了FPGA邏輯設(shè)計(jì)的測試驗(yàn)證過程。關(guān)鍵詞:黑盒

2009-08-19 09:12:41 9

9 本文介紹了基帶測試系統(tǒng)中,如何應(yīng)用FPGA實(shí)現(xiàn)后臺計(jì)算機(jī)與測試環(huán)境數(shù)據(jù)交互以及存儲的電路設(shè)計(jì)流程,并已在某基站測試系統(tǒng)中成功應(yīng)用。

2010-08-09 15:00:32 27

27 目錄•FPGA調(diào)試的挑戰(zhàn)•傳統(tǒng)的FPGA調(diào)試方案•Agilent FPGA動態(tài)探頭的調(diào)試方案•總結(jié)

2010-10-11 11:04:36 26

26 設(shè)計(jì)了一種基于FPGA的單板單片主控器件的低成本即插即用虛擬測試系統(tǒng)。系統(tǒng)包括兩路分立信號源、一路虛擬存儲示波器和16路高速虛擬邏輯分析儀,結(jié)合FPGA、高速DAC/ADC設(shè)計(jì)特點(diǎn),

2010-12-14 10:07:12 16

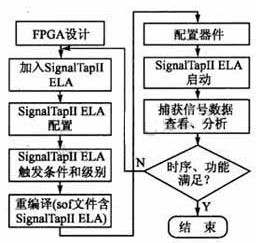

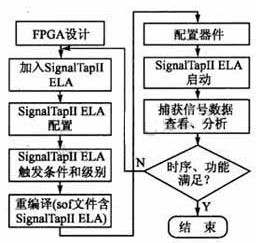

16 隨著FPGA設(shè)計(jì)復(fù)雜度的增加,傳統(tǒng)測試方法受到限制。在高速集成FPGA測試中,其內(nèi)部信號的實(shí)時獲取和分析比較困難。介紹了Quartus II中SingalTap II嵌入式邏輯分析器的使用,并給出一個

2010-12-17 15:25:17 16

16 虛擬FPGA邏輯驗(yàn)證分析儀的設(shè)計(jì)

隨著FPGA技術(shù)的廣泛使用,越來越需要一臺能夠測試驗(yàn)證FPGA芯片中所下載電路邏輯時序是否正確的儀器。目前,雖然Agilent、Tektronix 等大公司生

2008-10-15 08:56:31 575

575

邏輯分析儀測試在基于FPGA的LCD顯示控制中的應(yīng)用

摘要:邏輯分析儀作為基礎(chǔ)儀器,應(yīng)該在基礎(chǔ)數(shù)字電路教學(xué)中得到廣泛應(yīng)用。本文介紹了

2008-11-27 09:38:24 1031

1031

FPGA 重復(fù)配置和測試的實(shí)現(xiàn)

從制造的角度來講,FPGA測試是指對FPGA器件內(nèi)部的邏輯塊、可編程互聯(lián)線、輸入輸出塊等資源的檢測。完整的FPGA測試包括

2009-09-03 11:17:08 528

528

FPGA重復(fù)配置和測試的實(shí)現(xiàn)

從制造的角度來講,FPGA測試是指對FPGA器件內(nèi)部的邏輯塊、可編程互聯(lián)線、輸入輸出塊等資源的檢測。完整的FPGA測試包括兩步,一是配置FPGA

2010-01-26 09:39:56 544

544

現(xiàn)代科技對系統(tǒng)的可靠性提出了更高的要求,而FPGA技術(shù)在電子系統(tǒng)中應(yīng)用已經(jīng)非常廣泛,因此FPGA易測試性就變得很重要。要獲得的FPGA內(nèi)部信號十分有限、FPGA封裝和印刷電路板(PCB)

2010-08-04 17:35:45 600

600

邏輯分析儀自1973年問世以來,在短短幾十年的時間內(nèi)得到了迅速的發(fā)展。傳統(tǒng)邏輯分析儀利用芯片的引腳對信號采樣,并送到顯示部分對系統(tǒng)進(jìn)行分析,但對于無引腳的封裝類型,傳統(tǒng)邏輯分析儀很難有效的監(jiān)測系統(tǒng)內(nèi)部信號。而在FPGA測試中,嵌入式邏輯分析儀(ELA

2011-03-15 14:52:53 38

38 本文提出了一種基于SoPC的FPGA在線測試方法,是對現(xiàn)有FPGA在線測試方法的一種有效的補(bǔ)充。

2011-04-18 11:46:20 1145

1145

誤碼測試儀是檢測通信系統(tǒng)可靠性的重要設(shè)備。傳統(tǒng)的誤碼測試儀基于CPLD和CPU協(xié)同工作,不僅結(jié)構(gòu)復(fù)雜,價格昂貴,而且不方便攜帶。基于FPGA的高速誤碼測試儀,采用FPGA來完成控制和

2011-05-06 16:03:07 42

42 基于對FPGA系統(tǒng)失效機(jī)理的深入分析, 提出了軟件測試技術(shù)在FPGA測試中的應(yīng)用, 并分析了其可行性; 通過對比FPGA與軟件系統(tǒng)的異同, 歸納出FPGA特有的測試要求,從而在軟件測試技術(shù)的基礎(chǔ)

2011-09-29 17:41:21 65

65 本文核心提示: 隨著FPGA接口的速度提高,高速接口的測試、PCB板級的測試、EMI/EMC的測試等,這些測試的難度會越來越突出。想要實(shí)現(xiàn)FPGA的自動化測試的話,就需要提高軟件的可控性和

2012-08-27 10:09:08 972

972 基于FPGA的慣性平臺測試保護(hù)電路設(shè)計(jì)..

2016-01-04 17:03:55 7

7 基于FPGA的ADC指標(biāo)測量及測試系統(tǒng)。

2016-05-10 11:47:13 13

13 電子專業(yè)單片機(jī)相關(guān)知識學(xué)習(xí)教材資料——FPGA套件開箱測試篇

2016-08-23 15:55:35 0

0 基于反熔絲的FPGA的測試方法_馬金龍

2017-01-07 19:08:43 2

2 基于LabVIEW與FPGA的飛行訓(xùn)練彈測試系統(tǒng)設(shè)計(jì)_劉克軒

2017-02-07 18:22:06 6

6 基于FPGA和無線通信的密立根油滴測試系統(tǒng)設(shè)計(jì)_徐富新

2017-03-19 19:08:35 0

0 邏輯分析儀是利用時鐘從測試設(shè)備上采集和顯示數(shù)字信號的儀器,最主要作用在于時序判定。由于邏輯分析儀不像示波器那樣有許多電壓等級,通常只顯示兩個電壓(邏輯1和0),因此設(shè)定了參考電壓后,邏輯分析儀將被

2017-10-16 15:35:29 3

3 ,不利于硬件的開發(fā)進(jìn)度。面對這一難題,文章從FPGA 的軟硬件協(xié)同測試角度出發(fā),利用PC 機(jī)和測試硬件設(shè)備的特點(diǎn),進(jìn)行FPGA 的軟硬件協(xié)同測試的設(shè)計(jì),努力實(shí)現(xiàn)FPGA 的軟硬件協(xié)調(diào)測試系統(tǒng)在軟硬件的測試和分析中的應(yīng)用。

2017-11-18 05:46:28 1616

1616 中的開放式FPGA,就可以自己編寫儀器的測試功能。 儀器廠商早就認(rèn)識到FPGA的優(yōu)勢,而且也利用其獨(dú)特的處理能力來實(shí)現(xiàn)儀器的各種特性: * 在示波器上進(jìn)行預(yù)觸發(fā)采集 * 在矢量信號分析儀上通過信號處理生成I和Q數(shù)據(jù)。

2017-11-18 05:58:01 1558

1558

)等部分組成。對FPGA進(jìn)行測試要對FPGA內(nèi)部可能包含的資源進(jìn)行結(jié)構(gòu)分析,經(jīng)過一個測試配置(TC)和向量實(shí)施(TS)的過程,把FPGA配置為具有特定功能的電路,再從應(yīng)用級別上對電路進(jìn)行測試,完成電路的功能及參數(shù)測試。 2 FPGA的配置方法 對FPGA進(jìn)行配置有多種方法可以選擇,包括邊界掃描配置方法等。

2017-11-18 10:44:37 2001

2001

從制造的角度來講,FPGA測試是指對FPGA器件內(nèi)部的邏輯塊、可編程互聯(lián)線、輸入輸出塊等資源的檢測。完整的FPGA測試包括兩步,一是配置FPGA、然后是測試FPGA,配置FPGA是指將FPGA通過

2017-11-24 20:55:53 5922

5922

微軟數(shù)據(jù)科學(xué)家Ilia Karmanov最新測試的結(jié)果顯示,亞馬遜MXNet在CNN、RNN與NLP情感分析任務(wù)上性能強(qiáng)勁,而TensorFlow僅擅長于特征提取。

2017-12-06 16:04:40 8245

8245 摘要: 基于對FPGA系統(tǒng)失效機(jī)理的深入分析,提出了軟件測試技術(shù)在FPGA測試中的應(yīng)用,并分析了其可行性;通過對比FPGA與軟件系統(tǒng)的異同,歸納出FPGA特有的測試要求,從而在軟件測試技術(shù)的基礎(chǔ)上

2018-01-19 22:34:59 937

937 將神經(jīng)網(wǎng)絡(luò)模型訓(xùn)練好之后,在輸入層給定一個x,通過網(wǎng)絡(luò)之后就能夠在輸出層得到特定的y,那么既然有了這么強(qiáng)大的模型,為什么還需要RNN(循環(huán)神經(jīng)網(wǎng)絡(luò))呢?

2018-05-05 10:51:00 5037

5037

2014 年 RNN/LSTM 起死回生。自此,RNN/LSTM 及其變種逐漸被廣大用戶接受和認(rèn)可。起初,LSTM 和 RNN 只是一種解決序列學(xué)習(xí)和序列翻譯問題的方法(seq2seq),隨后被用于語音識別并有很好的效果。

2018-04-25 09:43:56 20289

20289 在循環(huán)神經(jīng)網(wǎng)絡(luò)可以用于文本生成、機(jī)器翻譯還有看圖描述等,在這些場景中很多都出現(xiàn)了RNN的身影。

2018-05-11 14:58:41 13295

13295

在設(shè)計(jì)基于FPGA的電子系統(tǒng)時,一般需要用示波器、邏輯分析儀等外部測試設(shè)備進(jìn)行輸入輸出信號的測試,借助測試探頭把信號送到測試設(shè)備上進(jìn)行觀察分析。當(dāng)然,前提是需要保留足夠多的引腳,以便能選擇信號來驅(qū)動

2019-01-08 08:29:00 1377

1377

由 mengqiqi 于 星期三, 2018-09-05 09:58 發(fā)表 一、前述 CNN和RNN幾乎占據(jù)著深度學(xué)習(xí)的半壁江山,所以本文將著重講解CNN+RNN的各種組合方式,以及CNN和RNN

2018-09-06 22:32:01 539

539 梯度爆炸/消失不僅僅是RNN存在的問題。由于鏈?zhǔn)椒▌t和非線性激活函數(shù),所有神經(jīng)網(wǎng)絡(luò)(包括前向和卷積神經(jīng)網(wǎng)絡(luò)),尤其是深度神經(jīng)網(wǎng)絡(luò),都會出現(xiàn)梯度消失/爆炸問題。這導(dǎo)致低層網(wǎng)絡(luò)訓(xùn)練非常緩慢。那么解決辦法就是在神經(jīng)網(wǎng)絡(luò)之間添加直接連接,使梯度傳播更順暢。

2019-05-05 16:05:26 15905

15905

MATLAB 和 Simulink 測試環(huán)境,并將其與運(yùn)行于 FPGA 開發(fā)板上的設(shè)計(jì)相連接。這有助于實(shí)現(xiàn)在實(shí)際硬件上運(yùn)行的 FPGA 設(shè)計(jì)的高逼真度協(xié)同仿真,同時復(fù)用開發(fā)階段使用的測試環(huán)境。

2019-08-02 23:18:07 2043

2043 基于FPGA的PCB測試機(jī)的硬件控制系統(tǒng),提高了PCB測試機(jī)的測試速度、簡化電路的設(shè)計(jì)。

2020-04-01 17:56:56 1688

1688 基于FPGA的PCB測試機(jī)的硬件控制系統(tǒng),提高了PCB測試機(jī)的測試速度、簡化電路的設(shè)計(jì)。

2019-10-23 15:15:45 1867

1867 遞歸神經(jīng)網(wǎng)絡(luò)(RNN)被提出用來處理80年代的輸入序列時間信息。1993年,神經(jīng)歷史壓縮器系統(tǒng)解決了“非常深度學(xué)習(xí)”任務(wù),該任務(wù)需要及時展開RNN中的1000多個后續(xù)層。

2020-03-22 10:23:00 6492

6492

FPGA概述FPGA調(diào)試介紹調(diào)試挑戰(zhàn)設(shè)計(jì)流程概述■FPGA調(diào)試方法概述嵌入式邏輯分析儀外部測試設(shè)備■使用 FPGAVIEW改善外部測試設(shè)備方法■FPGA中高速O的信號完整性測試和分析

2020-09-22 17:43:21 9

9 遠(yuǎn)控木馬作為一種高級形態(tài)的惡意代碼,不僅能收集用戶敏感信息,而且可以通過命令控制引發(fā)大規(guī)模的攻擊。為高效準(zhǔn)確地識別遠(yuǎn)控木馬,通過結(jié)合靜態(tài)分析和動態(tài)行為分析方法提取文件特征,利用深度學(xué)習(xí)對樣本特征

2021-03-30 09:21:44 15

15 神經(jīng)網(wǎng)絡(luò)是深度學(xué)習(xí)的載體,而神經(jīng)網(wǎng)絡(luò)模型中,最經(jīng)典非RNN模型所屬,盡管它不完美,但它具有學(xué)習(xí)歷史信息的能力。后面不管是encode-decode 框架,還是注意力模型,以及自注意力模型,以及更加

2021-05-10 10:22:45 10993

10993

神經(jīng)網(wǎng)絡(luò)是深度學(xué)習(xí)的載體,而神經(jīng)網(wǎng)絡(luò)模型中,最經(jīng)典非RNN模型所屬,盡管它不完美,但它具有學(xué)習(xí)歷史信息的能力。后面不管是encode-decode 框架,還是注意力模型,以及自注意力模型,以及更加

2021-05-13 10:47:46 22437

22437

基于RNN的GIS故障預(yù)測算法及系統(tǒng)設(shè)計(jì)

2021-07-01 15:38:37 30

30 循環(huán)神經(jīng)網(wǎng)絡(luò)(Recurrent Neural Network,RNN)是一種用于處理序列數(shù)據(jù)的神經(jīng)網(wǎng)絡(luò)。相比一般的神經(jīng)網(wǎng)絡(luò)來說,他能夠處理序列變化的數(shù)據(jù)。比如某個單詞的意思會因?yàn)樯衔奶岬降膬?nèi)容不同而有不同的含義,RNN就能夠很好地解決這類問題。

2022-03-15 10:44:42 1544

1544 時序分析時FPGA設(shè)計(jì)中永恒的話題,也是FPGA開發(fā)人員設(shè)計(jì)進(jìn)階的必由之路。慢慢來,先介紹時序分析中的一些基本概念。

2022-03-18 11:07:13 2096

2096 FPGA設(shè)計(jì)的主要驗(yàn)證手段之一,不需要設(shè)計(jì)者編寫測試向量,由軟件自動完成分析,驗(yàn)證時間大大縮短,測試覆蓋率可達(dá)100%。

2022-09-27 14:45:13 1809

1809 本次測試內(nèi)容為基于ARM+FPGA架構(gòu)的米爾MYD-JX8MMA7開發(fā)板其ARM端的測試例程pcie2screen并介紹一下FPGA端程序的修改。

2023-07-08 14:38:09 384

384

核、工具、庫、模型和示例設(shè)計(jì)組成。它們在設(shè)計(jì)時充分考慮了高效率和易用性,可在 Xilinx FPGA 和自適應(yīng)計(jì)算加速平臺 (ACAP) 上釋放 AI 加速的全部潛力。RNN 工具通過抽象底層 FPGA 和 ACAP 的復(fù)雜性,使開發(fā) RNN 推理應(yīng)用變得容易。

2023-09-13 17:32:53 0

0 點(diǎn)擊上方 藍(lán)字 關(guān)注我們 大容量、高速率和低功耗已成為FPGA的發(fā)展重點(diǎn)。 嵌入式邏輯分析工具無法滿足通用性要求,外部測試工具可以把FPGA內(nèi)部信號與實(shí)際電路聯(lián)合起來觀察系統(tǒng)真實(shí)運(yùn)行情況。 隨著

2023-10-23 15:20:01 460

460

本文來源:MomodelAI循環(huán)神經(jīng)網(wǎng)絡(luò)是一類人工神經(jīng)網(wǎng)絡(luò),其中節(jié)點(diǎn)之間的連接可以創(chuàng)建一個循環(huán),允許某些節(jié)點(diǎn)的輸出影響對相同節(jié)點(diǎn)的后續(xù)輸入。涉及序列的任務(wù),如自然語言處理、語音識別和時間序列分析

2023-12-15 08:28:11 217

217

電子發(fā)燒友App

電子發(fā)燒友App

評論