本帖最后由 maochengquan 于 2019-12-16 09:32 編輯

用示波器探針接A線,另一端接B線,觀察發送及接收的信號,接收信號呈差分信號波形,但是發送信號是非差分信號,why?電路圖中的二極管均未接。

2019-12-16 08:46:16

做數字電路設計的朋友對差分信號的定義應該都不會太陌生,在當前比較流行的高速串行總線上,基本都是使用的差分信號。比如USB,PCIE,SATA等等。大多數的FPGA也都支持差分信號,甚至某些新型

2018-09-03 11:08:41

該電路的目的是用3.3VFPGA芯片采集編碼器的光柵信號,而編碼器信號為5v電平故需要電平轉換:5V轉3.3V,采用的電平轉換芯片為SN74LVC4245A。編碼器發出的信號為四路差分信號,需將這四

2015-07-13 21:26:17

你好!我正在研究一個項目,我需要使用差分信號。我正在使用Artydevelopment平臺(圍繞Artix-7?FPGA設計),我在生成兩個差分信號(P和N)時遇到了一些問題。我使用示波器通過將其

2020-08-13 09:33:58

求大師請教,差分信號在PCB布線中應該注意什么?加什么保護措施?公司用的是DS8921做通信!

2012-08-18 10:20:27

什么是差分信號差分信號與單端信號的區別差分信號的優點差分信號在做pcb設計時的處理方法

2021-03-03 07:09:27

什么是差分信號差分信號與單端信號的區別差分信號的優點差分信號在做pcb設計時的處理方法

2021-01-28 06:01:01

AM26C31差分信號的輸出,需要在差分信號之間接電容嗎?

2018-04-18 09:08:42

的抗干擾能力。原始的輸入信號經過倒相器和緩沖器之后形成一對大小相等而極性相反的差分信號。對模擬信號,倒相器可以用運算放大器的反相比例放大電路來實現,緩沖器可以用運算放大器的同相跟隨電路來實現。對數字信號

2016-11-15 10:39:47

對差分信(VDS)號而言,對其影響最大的因素是它們的對地阻抗是否一致,也就是對地平衡度,它們之間相對的阻抗影響并不特別重要,之間分布電容大了只會衰落信號強度,不會引入噪聲和干擾,也就是對信噪比不會

2019-05-31 08:23:03

差分信號布線時信號完整性問題;影響SI的因素;解決問題的設計辦法;

2016-09-07 11:25:46

差分信號布線誤區

2015-08-27 22:09:50

AM26LS32 按照正常接法輸出端接示波器,按AUTO之后頻率在跳變,是不是說AM26LS32沒有工作,或者輸入不正常。我是按照datasheet說明接線的。看到別人都說能在示波器上看到方波,差分信號來源是松下伺服電機A相反饋,電機轉動的情況下測的

2013-03-01 16:45:15

以下部分來源野火教程、普中教程和百度的內容,后期有時間再整理。1.差分信號1.概述差分信號,又叫差模信號,通過兩根信號線上的電壓差值來表示邏輯0和邏輯1。表示邏輯時,這兩個信號線的振幅相等,相位

2021-08-19 08:11:10

差分信號是指使用兩根信號線傳輸一路信號,依靠信號間電壓差進行判決的電路,既可以是模擬信號,也可以是數字信號。實際的信號都是模擬信號,數字信號只是模擬信號用門限電平量化后的取樣結果。因此差分信號對于

2022-01-20 08:19:47

各種負載的電流 (I = CΔV/Δt)。因此,軌至軌信號(大 ΔV)的局限性就顯而易見了:需要更多的電源來實現更短的轉換時間(更小的 Δt)。那么我們應如何圍繞數字設計獲得高速信號,并避免單端信號的損耗呢?實施差分信號! 圖 1:單端信號拓撲(左)/差分信號拓撲(右)差分系統一般是三導線系統…

2022-11-22 06:07:48

之間的單端至差分信號轉換。SN65LVDS1 采用 2.4V 或更高電源電壓運行,理想適用于沒有 3.3V 電軌的低功耗應用。

2018-09-17 16:34:43

在高速 PCB 設計中,差分信號的應用越來越廣泛,這主要是因為和普通的單端信號走線相比,差分信號具有抗干擾能力強、能有效抑制EMI、時序定位精確的優勢。作為一名(準)PCB 設計工程師,我們當然需要充分理解差分信號!

2021-02-05 07:27:44

一個差分信號是用一個數值來表示兩個物理量之間的差異。從嚴格意義上來講,所有電壓信號都是差分的,因為一個電壓只能是相對于另一個電壓而言的。在 某些系統里,系統\'地\'被用作電壓基準點。當

2023-11-22 08:30:38

IP層次結構中以較低級別實例化。我在XPS中沒有遇到這樣的錯誤。是否可以選擇允許緩沖器處于較低電平,并將差分信號從頂部連接為差分,直到需要它們的電平并轉換為單端?或者如何在不對我的IP進行太多更改

2018-11-02 11:38:13

一個差分信號是用一個數值來表示兩個物理量之間的差異。從嚴格意義上來講,所有電壓信號都是差分的,因為一個電壓只能是相對于另一個電壓而言的。在某些系統里,系統'地'被用作電壓基準點。當'地'當作電壓測量

2015-01-07 14:22:17

如果接一路差分信號是不是用信號源雙路信號分別接差分的IQ端,然后剩下的黑線都接地線,并且信號源設置雙端信號輸出,并且信號反向?那如果接雙路差分信號呢?一個信號源夠用嗎?

2017-03-01 12:06:47

差分信號詳細介紹 一個差分信號是用一個數值來表示兩個物理量之間的差異。從嚴格意義上來講,所有電壓信號都是差分的,因為一個電壓只能是相對于另一個電壓而言的。在某些系統里,系統'地'被

2009-09-06 08:58:06

差分信號的讀寫數據問題時序圖高手幫我分析下怎么傳數據的 萬分感謝!

2014-08-04 18:56:49

在我的vhfl文件中使用ibufds和obufds與使用make_diff_pair_port命令在Xdc約束文件中聲明它們相同嗎?它們是產生相同的結果還是它們不同?以上來自于谷歌翻譯以下為原文

2018-11-01 16:10:19

LTC2400,簡單的軌到軌電路將差分信號轉換為單端信號,可在單電源或雙電源上工作,其中分辨率比精度更重要

2019-08-23 08:38:00

差分信號,什么是差分信號一個差分信號是用一個數值來表示兩個物理量之間的差異。從嚴格意義上來講,所有電壓信號都是差分的,因為一個電壓只能是相對于另一個電壓而言的。在某些系統里,系統’地’被用作電壓

2019-05-31 08:01:24

想問一下該電路的差分信號轉為單端信號最好的芯片跟電路接法要怎么接?

2020-11-15 14:28:47

差分信號差分傳輸是一種信號傳輸的技術,區別于傳統的一根信號線一根地線的做法(單端信號),差分傳輸在這兩根線上都傳輸信號,這兩個信號的振幅相等,相位相反。在這兩根線上傳輸的信號就是差分信號。

2019-05-29 06:52:45

請教各位,請問SPWM波是差分信號還是單端信號?

2015-06-10 11:43:14

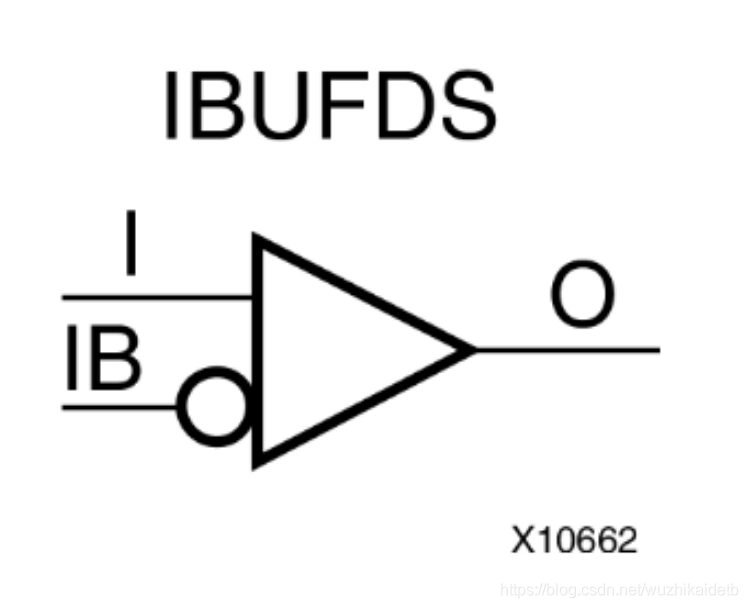

OBUFDS:將標準單端信號轉換成差分信號,輸出端口需要直接對應到頂層模塊的輸出信號,和IBUFDS為一對互逆操作。 源碼 仿真結果

2020-12-23 17:17:47

我想用ad620放大微小電阻上的電壓信號,但經其輸出電壓為單端信號。我得將其轉換為差分信號,求助各位大神,如果能有電路圖就更好了

2020-05-07 05:23:19

什么是差分信號?為什么要用差分信號?差分放大電路的基本結構和作用差分放大電路的應用電路

2021-03-11 08:21:01

一個差分信號是用一個數值來表示兩個物理量之間的差異。從嚴格意義上來講,所有電壓信號都是差分的,因為一個電壓只能是相對于另一個電壓而言的。在某些系統里,系統'地'被用作電壓基準點。當'地'當作電壓測量

2016-07-14 14:56:43

一個差分信號是用一個數值來表示兩個物理量之間的差異。從嚴格意義上來講,所有電壓信號都是差分的,因為一個電壓只能是相對于另一個電壓而言的。在某些系統里,系統'地'被用作電壓基準點。當'地'當作電壓測量

2016-07-14 09:48:32

你知道什么是差分信號嗎?一個差分信號是用一個數值來表示兩個物理量之間的差異。從嚴格意義上來講,所有電壓信號都是差分的,因為一個電壓只能是相對于另一個電壓而言的。在某些系統里,系統'地'被用作電壓

2016-08-19 11:35:46

旋轉變壓器能夠檢測電機轉子的轉速和位置,而且輸出的信號是差分信號,現在這個旋轉變壓器有3路信號接口,而要和它連接的帶有模數轉換功能的芯片有6路信號接口,那么它們應該怎么連接呢?為什么?!!希望各路大神能夠指導,謝謝!

2016-07-28 17:59:28

各位大神,小弟求助:如何實現SPI與差分信號的互相轉換?

2013-03-29 09:26:40

(1)單端信號 以共同的地線為基準。適用于傳感器有共同地線,信號幅值大,傳輸距離近,不易受干擾的場合。 (2)差分信號 每路信號有自己的基準地線,兩根信號極性相反,共模噪聲被抑制。適用于小幅值

2019-01-12 12:18:12

差分轉單端芯片可以把5V的差分輸入信號轉為3.3V或者3V單端信號么?用哪個芯片3.3V的單端輸入給到差分轉換芯片 輸出的差分信號又是幾V的呢?求大神解答~~!

2016-06-07 13:51:04

如圖中所示,前級運放輸出一對差分信號,經過處理器切換到二階低通濾波器上,最后傳輸到串行AD進行數據轉換。這里不太明白濾波器前對差分信號的切換如何處理,切換頻率是多大?理論上說AD轉換周期一定需要小于切換周期,對嗎?

2017-03-03 10:53:27

你好,我正在使用Virtex 5和INPUTS和OUTPUTS的一些高速差分信號。我知道我必須使用緩沖區,但我不太確定如何在Verilog中編寫代碼。因此,我有兩個問題:1.我在哪里實例化

2020-06-19 09:53:50

我們可以將LvCmos 2.5 i / o轉換為Fpga內的差分信令(Lvds)嗎?因為我想使用GTx收發器,收發器只接受差分信號..我可以這樣做嗎?你可以幫忙嗎?/

2020-06-16 14:27:26

正在做一個電壓采集的項目,輸入信號的共模信號,而28377S,16位ADC需要輸入差分信號,我利用下圖的方式將共模信號轉換成差分信號,請教TI工程師,能否這樣做。輸入的共模信號是0—2.5V的直流信號,在輸入之前已經做了濾波處理。ADC的采樣時間是320ns,ADC時鐘頻率是40M。

2020-07-24 12:21:54

本帖最后由 Clair_ 于 2019-10-12 09:27 編輯

A+和A-是差分信號,能否用圖中辦法把信號轉換成單端信號?其中A+A-是5V的差分信號

2019-10-11 15:22:51

來源:互聯網在高速PCB設計中,差分信號的應用越來越廣泛,這主要原因是和普通的單端信號走線相比,差分信號具有抗干擾能力強、能有效抑制EMI、時序定位精確的優勢。作為一名(準)PCB設計工程師,我們必須搞定差分信號,接下來我們了解下相關內容吧!

2020-10-23 08:36:50

如題,需要一個差分信號輸入仿真,不知道怎么產生差分信號。。。。

2012-11-28 14:48:55

分對組成。我選擇其中一個并在AB7引腳上設置輸出。我收到的信號不是差分信號,而是單端信號。我該怎么做才能產生差分信號?

2020-08-07 06:27:32

時鐘信號從普通IO管腳輸入怎么進行處理,時鐘從普通IO管腳進入FPGA后能進入全局時鐘網絡嗎?因為只有全局時鐘管腳后面連接有IBUFG/IBUFGDS緩沖單元,如果差分時鐘信號從普通IO管腳進入后

2012-10-11 09:56:33

資料上說OBUFDS能將單端信號轉換為差分信號,Post_route simulation的仿真結果發現輸出的波形并不是互補的信號。程序中我是這樣用的:clkout_buf : OBUFDS

2017-03-07 11:25:55

“原始的輸入信號經過倒相器和緩沖器之后形成一對大小相等而極性相反的差分信號。對模擬信號,倒相器可以用運算放大器的反相比例放大電路來實現,緩沖器可以用運算放大器的同相跟隨電路來實現。對數字信號,可以

2012-11-16 19:59:22

單端信號單端信號是相對于差分信號而言的,單端輸入指信號有一個參考端和一個信號端構成,參考端一般為地端。差分信號差分傳輸是一種信號傳輸的技術,區別于傳統的一根信號線一根地線的做法(單端信號),差分傳輸

2017-03-02 10:58:00

描述全差分運算放大器(Rev. A for TEST!)用于測試差分信號的CMRR。PCB

2022-08-08 07:30:58

的信號能夠對外部干擾能夠起到很強的抗干擾能力。 原始的輸入信號經過倒相器和緩沖器之后形成一對大小相等而極性相反的差分信號。對模擬信號,倒相器可以用運算放大器的反相比例放大電路來實現,緩沖器可以用

2019-05-29 07:19:25

單端信號:單端信號是相對于差分信號而言的,單端輸入指信號有一個參考端和一個信號端構成,參考端一般為地端。差分信號:差分傳輸是一種信號傳輸的技術,區別于傳統的一根信號線一根地線的做法(單端信號),差分

2017-11-19 13:45:25

您好Xilinx社區,我想用兩個時鐘驅動我的系統。一個時鐘用于多個組件,與主時鐘一起運行并由IBUFGDS生成。另一個應該驅動IBUFDS_GTE2原語,因為實現了PCI Express。我有兩個

2018-11-09 11:41:50

性能轉換器和高帶寬FPGA或ASICI/O中常用的高速接口。差分信號傳輸對于外部電磁干擾(EMI)具有很強的抑制能力(因為反相與同相信號之間的互相耦合所致),同時也相應地可以將任何因為LVDS信號傳輸

2019-07-23 07:27:54

嗨,我使用IBUFDS將差分時鐘信號轉換為單時鐘信號,這個轉換后的單個clokc信號將用于多個PLL_ADV。那么,我應該為每個PLL_ADV的clk_in添加BUFG嗎?或者我只需要在IBUFDS

2020-07-23 10:57:17

由于差分信號在一組特定電源電壓下使用較大信號,提高了對共模噪聲的抑制能力,降低了二次諧波失真,因而實現了更高的信噪比。由于這一需求,我們需要可將大多數信號鏈中的單端信號轉換為差分信號的電路模塊。

2021-04-09 06:56:19

AD7606能支持差分信號輸入嗎?差分信號的P和N都在0-5V左右,能直接接入AD7606的那兩個輸入端嗎?

2018-08-15 06:38:59

你好,我們目前有一設計ADC轉換的設計,想在同一個通道兼容單端模擬量和差分模擬量的轉換,請問AD7616芯片的單一通道是否可以做到此兼容方式?例如下面的接法是否可行?單端信號時:PIN1(V4B)接

2019-01-17 10:31:08

我們目前有一設計ADC轉換的設計,想在同一個通道兼容單端模擬量和差分模擬量的轉換,請問ad7616 ad7616芯片的單一通道是否可以做到此兼容方式?例如下面的接法是否可行?

單端信號時:平平1

2023-12-13 09:33:36

請問,ad7626數據手冊顯示,只有cnv信號支持單端,而clk不支持單端工作?因為目前fpga配置出現問題,不能提供clk、cnv的差分信號。

2018-09-10 11:02:55

做成差分信號了,兩根SMA線纜各0.4米長,

發送端用了這個原語

--OBUFDS_inst0 : OBUFDS

--generic map (

--IOSTANDARD =>

2024-02-02 16:23:05

怎樣將單端信號轉換成差分信號呢?變壓器有哪些最優匹配方法?如何改善ADC的增益平坦度并保持它的動態性能呢?

2021-04-22 06:35:25

你知道什么是差分信號嗎?一個差分信號是用一個數值來表示兩個物理量之間的差異。從嚴格意義上來講,所有電壓信號都是差分的,因為一個電壓只能是相對于另一個電壓而言的。在某些系統里,系統'地'被用作電壓

2016-08-19 12:35:47

嗨....我正在使用XC7A200T***g484板來研究。當我使用OBUFDS緩沖功能生成差分信號時,Vivado有一個警告:警告:[Labtools 27-3123]在用戶掃描鏈1或3處未檢測

2020-08-21 10:14:28

為了節約PCB板空間,充分靈活利用FPGA內部資源,對FPGA內置差分信號匹配終端進行研究。根據差分信號阻抗匹配的基礎理論,在自制的PCB電路板上利用差分信號線傳遞時鐘和圖像數據

2011-01-04 17:07:13 40

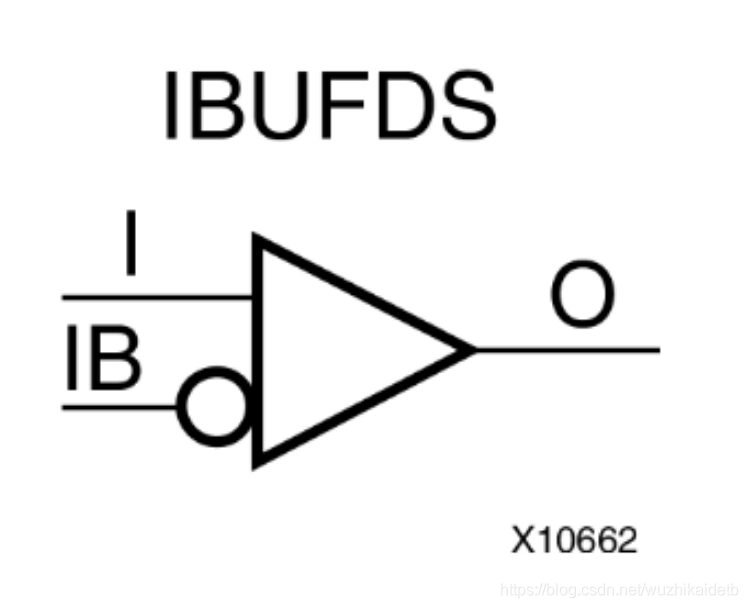

40 IBUFDS、和OBUFDS都是差分信號緩沖器,用于不同電平接口之間的緩沖和轉換。IBUFDS 用于差分輸入,OBUFDS用于差分輸出。

2022-02-16 16:21:27 3157

3157

差分信號如何轉換成單端信號? 差分信號和單端信號是電子信號傳輸中非常常見的兩種形式。差分信號由兩個互相反向的信號組成,單端信號只有一個信號。差分信號由于可以減少電磁干擾和提高傳輸距離,常被用于高速

2023-09-19 17:22:55 6009

6009

電子發燒友App

電子發燒友App

評論