摘 要: 多片FPGA組成的星形系統可解決跳頻和直接序列混合擴頻(FHDS)衛星測控信號大時延差高動態條件下的快速捕獲問題。捕獲搜索時采用1“主”+N“副”形式的Multi-FPGA組分時進行多普勒搜索,主FPGA實現捕獲控制和快速解跳解擴,其余N片FPGA實現碼片以下時間差的精細搜索和相干累積。針對信號體制和捕獲性能需求,所有芯片均采用Xilinx公司的基于RAM的XQR4VFX系列。本設計解決了單片宇航級FPGA資源受限條件下復雜捕獲問題,具有FPGA配置文件數目少、成本低、功耗低的優點。

?

0 引言

現場可編程門陣列(FPGA)具有可重復編程、開發周期短、運算能力強等特點,與外圍電路、ADC芯片以及程序存儲器(PROM)等配合能夠實現復雜的通信和信號處理功能。隨著微電子技術的發展,宇航級FPGA的硬件體系從問世時的1 200門發展到當今的數百萬門甚至千萬門級,為航天領域實時信號處理問題提供了解決平臺[1]。

我國陸基衛星測控網和中繼衛星測控均以直接序列擴頻測控體制為主,具有抗干擾、測距精度較高、一站對多星測控等優點[2]。跳頻和直接序列(FHDS)混合擴頻測控信號綜合了跳頻擴頻和直接序列擴頻的優點,測控信號抗截獲、抗干擾能力得到有效提升。與直擴信號相比,FHDS信號帶寬更寬,相應的自相關函數峰也更窄,捕獲時間搜索精度要求也隨之提高。因此在設計跳擴測控信號接收機時捕獲計算復雜度增加,在高等級宇航級芯片來源受控時,單片宇航級芯片單獨工作無法保證捕獲時間,需要采用多片FPGA設計方案[3]。

1 捕獲模型與算法設計

1.1 捕獲運算模型

首先分析捕獲運算模型,以便劃分各FPGA的數字信號處理功能。本地產生的中頻跳擴頻信號可表示為:

其中A為接收信號功率,τ表示收發信號之間時間差。若收發信機之間相對的徑向運動速度為v,則跳頻點fi處的多普勒頻率滿足:

跳擴信號參數設置如表1所示。

捕獲運算的運算復雜度主要在于跳擴信號與跳擴信號取共軛后的滑動搜索-相關運算:

1.2 FPGA捕獲分工與算法描述

為了解決高處理性能的宇航級FPGA貨源不足條件下的捕獲,需要設計適用于多片低處理性能FPGA的軟件[8],將相關運算化解為:

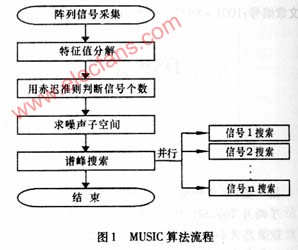

捕獲模型確定后,對捕獲算法進行描述。多普勒并行搜索是分時進行的,每次搜索增加Δv,時域搜索通過多片FPGA并行完成。基于多片FPGA的捕獲算法流程設計如下:

(1)將多普勒值和時延范圍劃分為若干個搜索單元,搜索粒度為:。

(2)主FPGA完成跳頻載波剝離。在搜索控制邏輯控制之下,解跳采用雙路下變頻器交替解跳。下變頻器分為M個,每個下變頻器負責Nhop/M個跳頻點內信號的解跳,解跳總時長均為NhopTh。下變頻器解跳輸出下抽到2倍碼片速率后,每個頻點上的解跳結果補零到2L個數據點,L為2的整數次冪。將L個數據點存入FPGA中的RAM,進入步驟(3)。

(3)主FPGA完成碼剝離。讀取RAM中解跳結果,按照經典的FFT-IFFT碼相關算法,進行Nhop次2L點FFT-IFFT運算,取出Nhop組L點相關結果,送入N片副FPGA中保存。

2 多片FPGA解決方案

2.1 硬件架構

Xilinx提供的宇航級芯片V4芯片具有豐富的邏輯資源和布線資源,能夠完成乘法、存儲、通信任務,其I/O資源也能滿足多FPGA之間的通信需求。

基于多片FPGA的測控信號捕獲的典型平臺如圖1所示,捕獲硬件結構由模擬數字轉換(ADC)、程序存儲ROM(PROM)、跳擴碼模塊、時鐘電路以及FPGA芯片組構成。FPGA芯片組采用的是“主從”星形結構,即主FPGA控制副FPGA進行工作,PROM共提供兩套FPGA軟件分別用于主FPGA和副FPGA。架構中各器件功能簡介如下:

(1)雙路ADC:將射頻下變頻到中頻的跳擴信號進行模擬-數字轉換,送入主FPGA。

(2)時鐘單元:產生FPGA工作時鐘。

(3)FPGA:完成基帶數字信號處理功能。經過對芯片面積、邏輯資源、I/O資源分析,將FPGA功能劃分為:主FPGA負責跳擴信號的解跳、捕獲流程控制、多片FPGA之間通信控制;副FPGA在主FPGA控制下完成跳擴信號并行捕獲;所有1+N片FPGA同步工作,工作時鐘鎖相到主FPGA工作時鐘。

(4)PROM:用于存儲FPGA配置信息,捕獲系統加電時完成對FPGA的加載。PROM1連接到主FPGA的SelectMAP模式配置引腳,PROM2連接到副FPGA的配置引腳[9]。

2.2 主FPGA軟件設計

主FPGA完成捕獲控制、多FPGA通信和解跳解擴功能。模塊間信號流圖如圖2所示,由于篇幅所限未標明時鐘clk和復位rst信號。模塊命名和功能如下:

(1)AcqCtrl:捕獲總控制

捕獲啟動和停止,捕獲流程控制,多FPGA極大值之間比較大小。

(2)Dehop:并行解跳

采用M個乘法器,實現時延范圍為(M-1)Th的并行解跳,將解跳結果送入解擴模塊。

(3)Despread:快速解直擴

完成直擴碼剝離,進行碼相關時長為1個跳頻時段的直擴碼滑動相關,將滑動相關運算的結果以Nhop為一組送到輸出接口。

(4)FPGACom:片間通信

單跳相關峰輸出,副FPGA控制接口,相關運算數據交換接口。

2.3 副FPGA軟件設計

副FPGA的任務是完成碼片以內的時間精細搜索和相關運算,比較得到該FPGA負責的時段內的極大值和捕獲結果并送給主FPGA。邏輯功能劃分如圖3所示。

副FPGA子模塊功能分別為:

(1)ScanCtrl:時延搜索控制

當主FPGA發出搜索指令,開始搜索。每次相乘累加比較大小后,時延搜索單元前進一格,搜索完成后退出。

(2)Dem:相乘累加

此模塊中包含相位映射模塊、復數乘法器(Multiply)和累加模塊。

相位映射模塊根據精細時延值計算出相位,查正弦表后得到正弦和余弦值。與接收的復數信號進行復數相乘和Nhop次累加運算后得到時長為ThNhop的相干累積結果。

(3)Compare:比較大小

按Dem輸出的值和使能信號進行逐個比較,保留極大值及其對應精確時延,比較結束后輸出最大值(Rmax,τn)送往主FPGA。

2.4 FPGA間通信設計

如圖4所示,主FPGA與副FPGA之間的引腳連接須完成副FPGA捕獲控制解決信號交互問題。信號交互接口分為兩類,一類是主FPGA輸出,包含搜索控制和預處理數據,在主FPGA內合路同時送往各個副FPGA。另一類是各副FPGA輸出,將捕獲搜索得到的極大值和捕獲結果并行輸入主FPGA。

3 實現情況

3.1 時鐘與芯片資源使用

時鐘速率可達200 MHz。面積占用:主FPGA占用60%,副FPGA占用78%。I/O資源占用:主FPGA占用70%,副FPGA占用50%。

3.2 試驗結果

在以FPGA為處理核心的基帶板上進行了實物驗證,試驗環境包括安捷倫E4438C信號源2臺、XX型衛星應答機射頻通道、基于單片Xilinx Virtex3的基帶板一副、基于多片Virtex4的基帶板一副,以及電源、連接線若干。V3基帶板完成發送中頻跳擴測控信號的功能,信號源負責信號上變頻和射頻加噪,應答機射頻通道用于下變頻,V4基帶板實現跳擴測控信號的解跳解擴和捕獲功能。

4 結束語

多FPGA設計可用于快速信號處理、軍事目標匹配等方面。在FPGA芯片來源受限時,多FPGA能解決航天測控信號的捕獲問題,其中FPGA之間的通信設計和捕獲算法的邏輯分割是FPGA設計的關鍵。

電子發燒友App

電子發燒友App

評論