早前,多家客戶已經收到全新英特爾 Stratix 10 GX 10M FPGA樣片,該產品是全球密度最高的FPGA,擁有1020 萬個邏輯單元,現已量產。該款元件密度極高的FPGA,是基于現有

2019-11-06 12:13:28 5510

5510 非晶硅反熔絲FPGA技術尤其有用,它可以提供一種高電路密度與低功耗,以及非易失性編程和高可靠性的組合。為了充分發揮其可靠性,FPGA廠商需要考慮反熔絲的崩潰(wear-out)機制,并通過一種

2011-05-27 09:55:42 1968

1968 電子發燒友網核心提示 :目前在高可靠領域應用的FPGA器件大約可占整個FPGA市場份額的10%~15%。對FPGA企業而言,高安全性或許不失為一條差異化的發展路徑。 目前FPGA的應用不斷擴展,

2012-10-17 09:43:44 1058

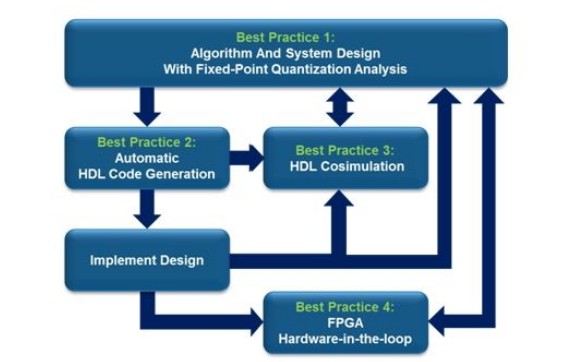

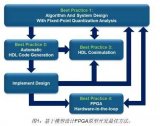

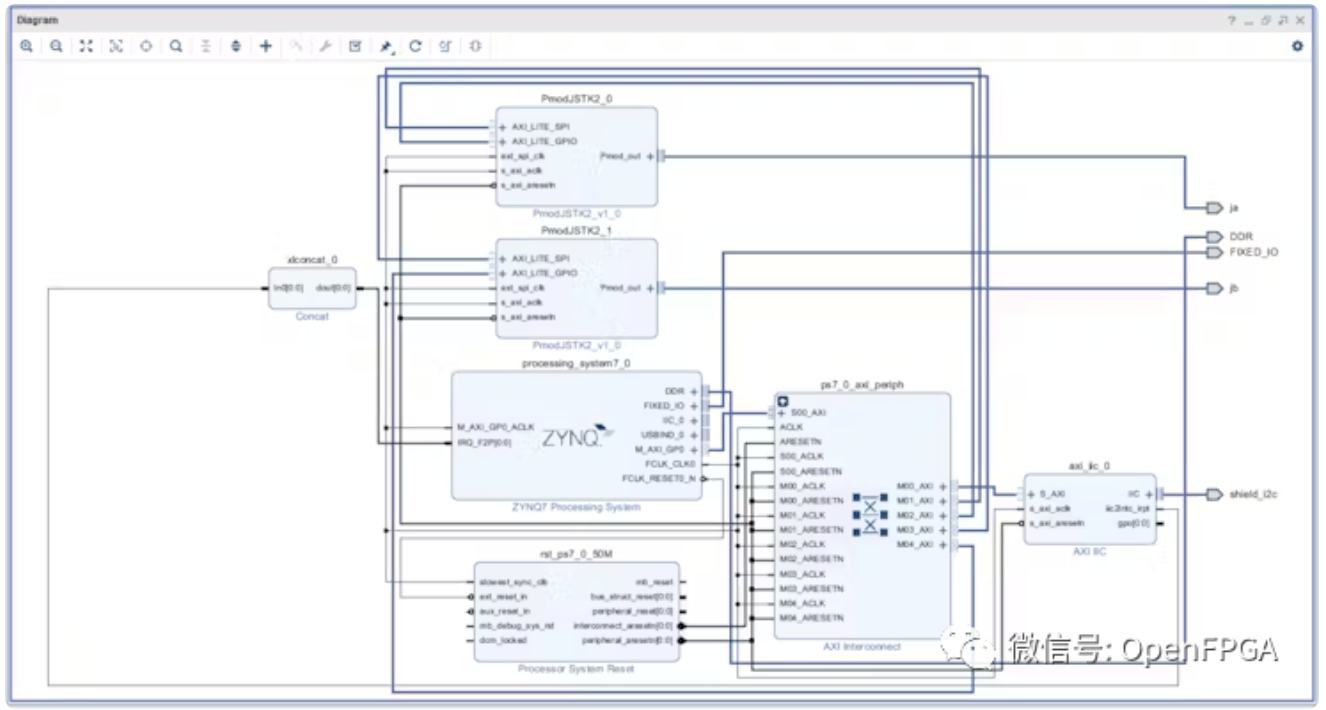

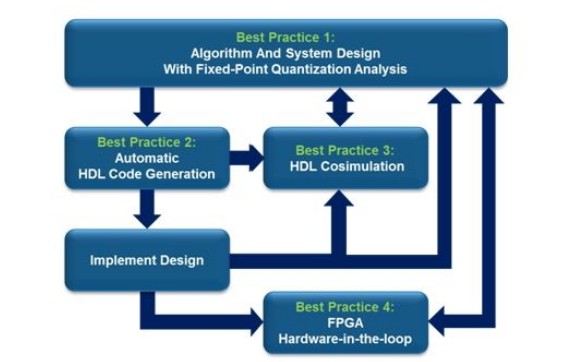

1058 本文將介紹使用MATLAB和Simulink創建FPGA原型的最佳方法。這些最佳方法包括:在設計過程初期分析定點量化的效應并優化字長,產生更小、更高效的實現方案;利用自動HDL代碼生成功能,

2013-01-28 11:08:08 16036

16036

對FPGA設計中常用的復位設計方法進行了分類、分析和比較。針對FPGA在復位過程中存在不可靠復位的現象,提出了提高復位設計可靠性的4種方法,包括清除復位信號上的毛刺、異步復位同步釋放、采用專用全局

2014-08-28 17:10:03 8153

8153 使用Vivado 2018.1 第二篇:mig IP的創建 1 DDR3 Digilent的Arty Artix-35T FPGA開發板板載MT41K128M16JT-125 DDR3基本信息如下表所示

2020-12-16 15:47:59 1692

1692

本文列出了FPGA設計中常見的十個錯誤。我們收集了 FPGA 工程師在其設計中犯的 10 個最常見錯誤,并提供了解決方案的建議和替代方案。本文假定讀者已經具備 RTL 設計和數字電路方面的基礎。接下來讓我們深入探討在FPGA 設計中要避免的 10 大錯誤。

2023-05-31 15:57:28 529

529

FPGA 非常適合精密電機控制,在這個項目中,我們將創建一個簡單的電機控制程序,在此基礎上可以構建更復雜的應用。

2023-08-11 09:06:33 753

753

國微思爾芯發布3億門原型驗證系統,采用業界最高容量的 Intel? Stratix? 10 GX 10M FPGAs。

2020-09-08 10:56:20 883

883 本帖最后由 lee_st 于 2017-10-31 09:00 編輯

10分鐘學會FPGA設計

2017-10-21 20:23:56

10分鐘學會FPGA設計

2017-09-27 10:57:47

文檔創建既然是ROM,那么我們就必須實現給它準備好數據,然后在FPGA實際運行時,我們直接使用這些預存儲好的數據就行。Xilinx FPGA的片內ROM支持初始化數據配置。如圖所示,我們可以創建一個名為

2019-04-08 09:34:43

1. 概要本篇文章主要介紹在FPGA設計中如何使用本GXFPGA驅動創建一個中斷事件/請求。2. 簡介中斷作為硬件與軟件握手和同步的手段而被廣泛使用,可用于表示硬件進程的完成或軟件執行過程中的請求

2018-08-31 15:12:06

了3款足夠“有料”的FPGA及SoC系列:Arria 10、Stratix 10以及MAX 10,它們都是Altera在創新大潮中重磅推出的“第10代”(Generation 10)產品,也為

2019-07-01 08:14:44

請問各位大神,在沒有終端的情況下,如何創建一個帶有FPGA終端(NI PXLe-5840)的Labview項目?

2018-03-20 17:30:34

本帖最后由 一只耳朵怪 于 2018-6-7 10:23 編輯

該裝的驅動都裝了,但是就是沒辦法創建FPGA項目。在MAX理可以看到NI PCI 7833R可以看到 RTFPGANI RIO

2018-06-06 20:22:17

NetFPGA-10G是什么?它有什么功能?

2021-05-25 06:13:28

在英特爾? Stratix? 10 FPGA 上的實施方案。對于大批量任務,該方案能以每瓦 每秒 70 幅圖像的速度每秒處理 14,000 幅圖像;對于批量大小為 1 的任務,該方案能 以每瓦每秒

2019-07-17 06:34:16

請問一下Stratix 10 MX FPGA是什么?Stratix 10 MX FPGA有哪些功能?

2021-07-09 08:08:06

TINYFPGA AX1

2024-03-14 22:18:36

TINYFPGA AX2

2024-03-14 22:18:36

TINYFPGA BX

2024-03-14 22:18:36

`Xilinx FPGA入門連載8:Verilog源碼文件創建與編輯特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s/1jGjAhEm 1 Verilog

2015-09-21 11:18:07

The Artix-7 is part of the 7-Sseries of FPGA's from Xilinx. Containing 1,156 pins, creating

2014-02-13 09:24:15

。但如果你是新的FPGA技術,記住這一點,這不是最簡單的設計,以了解關于這個站點。HDL設計或如何創建示波器在FPGA內部邏輯。一部分1 -設計FIFO為主。第2部分 -基于RAM的設計。3部分 -觸發

2012-04-09 14:55:29

項目名稱:FPGA+c8051高可靠性通用核心板卡試用計劃:基于max10系列fpga和c8051設計一款2*3cm大小核心板 提供40個gpio 雙路uart。mcu的io通過fpga橋接 另外提供u***轉uart功能。板載epprom

2018-10-24 17:20:21

本文以星載測控系統為背景,提出了一種基于 Actel Flash FPGA的高可靠設計方案。采用不易發生單粒子翻轉的 flash FPGA芯片,結合 FPGA內部的改進型三模冗余、分區設計和降級重構,實現了高實時、高可靠的系統。

2021-05-10 06:58:47

`勇敢的芯伴你玩轉Altera FPGA連載79:FPGA片內ROM實例之ROM初始化文檔創建特權同學,版權所有配套例程和更多資料下載鏈接:http://pan.baidu.com/s

2018-06-20 22:04:28

本文詳細討論了基于FPGA的mif文件創建與使用,對于mif文件創建與使用均給出了兩種可行性的方法。mif文件具有固定格式,而對mif文件使用主要就是對mif。文件begin與end之間的內容進行修改。本文以四位二進制加法查找表的實現為例,給出了m(Matlab)語言源程序。

2021-05-06 06:04:19

完成數據采樣,并添加SDRAM和EEPROM模塊來擴展FPGA芯片的存儲資源、降低數據丟失的風險。在完成設計之后,本文針對性地設計了可靠性評估方法,確定本文所設計實現的可靠性等級為0.625,具有較高

2018-05-03 12:25:32

基于Multisim 10的電子電路可靠性研究利用Multisim 10平臺進行電子電路設計的可靠性研究,可以有效地解決傳統分析方法難以對電子電路設計進行容差精確分析的技術問題。方法為統計取樣法,其

2012-07-20 09:39:18

請問如何使用LabVIEW和FPGA來創建一個自動化的微控制器測試系統?

2021-04-09 06:08:00

為了FPGA保證設計可靠性, 需要重點關注哪些方面?

2019-08-20 05:55:13

目前,汽車中使用的復雜電子系統越來越多,而汽車系統的任何故障都會置乘客于險境,這就要求設計出具有“高度可靠性”的系統。同時,由于FPGA能夠集成和實現復雜的功能,因而系統設計人員往往傾向于在這些系統中采用FPGA。

2019-09-27 07:45:33

我安裝了FPGA Module 但按照幫助里說的總是創建不了 各位幫幫 最好能把關鍵步驟截個圖

2010-12-05 20:31:23

請幫幫我。我無法在FPGA中創建可用信號。(引腳FPGA中的網關輸出)顯示錯誤。焊盤位置的數量必須與驅動該網關輸出的信號的位數相匹配。格式必須指定為單元格數組,例如{'MSB',...,'LSB

2019-09-10 12:44:58

缺陷成團對FPGA片內冗余容錯電路可靠性的影響是什么?缺陷成團對冗余容錯電路可靠性的影響是什么?

2021-04-08 06:50:18

如何創建一個可靠、低成本、簡單的電感測試儀?

2021-04-14 06:05:52

概述EasyGo FPGA Coder Block是嵌入Matlab/Simulink里面的FPGA 仿真工具包軟件。提供了一些基礎的函數庫以及常用的控制函數模塊,配合

2022-05-19 09:16:05

概述EasyGo FPGA Solver是EasyGo開發的專門部署在FPGA 硬件上的解算器軟件。根據不同的應用需求,會有不同的FPGA Solver 選擇

2022-05-19 09:21:43

EP4CE10F17C8N,Cyclone IV FPGA設備,INTEL/ALTERAEP4CE10F17C8N,Cyclone IV FPGA設備,INTEL

2023-02-20 17:00:57

EP4CE10F17I7N,Cyclone IV FPGA設備,INTEL/ALTERAEP4CE10F17I7N,Cyclone IV FPGA設備,INTEL

2023-02-20 17:03:19

本文以星載測控系統為背景,提出了一種基于Actel Flash FPGA 的高可靠設計方案。采用不易發生單粒子翻轉的Flash FPGA 芯片,結合FPGA 內部的改進型三模冗余、分區設計和降級重構,

2010-01-20 14:35:53 21

21 mif文件的創建與使用是在基于FPGA的系統設計中引入ROM的關鍵環節。對mif文件的創建與使用展開詳細討論,給出兩種可行性方法,并引入實例在MAX+PLUS Ⅱ環境下做了詳細的仿真

2010-12-13 17:47:29 42

42 OrCAD FPGA系統規劃

創新的FPGA - PCB協同設計

該Cadence ®的OrCAD ® FPGA系統提供了一個完整的策劃,為FPGA - PCB協同設計,使用戶能夠創建可擴展解決方案的

2010-08-30 17:49:26 1748

1748

摘要:為提高8B/10B編解碼的工作速度和簡化邏輯方法,提出一種基于FPGA的8B/10B編解碼系統設計方案。與現有的8B/10B編解碼方案相比,該方案是一種利用FPGA實現8B/lOB編解碼的模塊方

2011-05-26 11:08:20 3364

3364

Altera于6月11日在北京宣布,全球同步推出10代FPGA和SoC。先行發布的包括高端Stratix10和中端Arria10系列。目標是替代傳統的ASSP和ASIC。

2013-06-13 14:26:14 2150

2150 在Altera的MAX?10現場可編程門陣列(FPGA)系列發布之際,艾睿電子公司(NYSE:ARW)推出了BeMicro Max 10FPGA評估板。

2014-10-08 09:58:21 2451

2451 ADC_Convertor_Using_MAX_10_FPGA_Development_Kit

2015-12-07 18:20:15 9

9 QNX程序創建指南

2017-01-03 17:40:48 0

0 通過在FPGA設計流程引入功率分析改善PCB的可靠性

2017-01-14 12:36:29 7

7 Flash 和反熔絲架構FPGA為汽車應用提供靈活、可靠和安全的平臺

2017-01-18 20:35:09 13

13 參加 ?FPGA? 功率優化班,將幫助您創建更高電源效率的 ?FPGA? 設計。通過本課程的學習,將有助于您的設計滿足更小型化的 ?FPGA? 器件,降低 ?FPGA? 功耗,或在更低的溫度下運行

2017-02-09 06:24:11 167

167 編譯FPGA VI至FPGA應用前必須創建一個程序生成規范。

2017-11-18 02:46:52 706

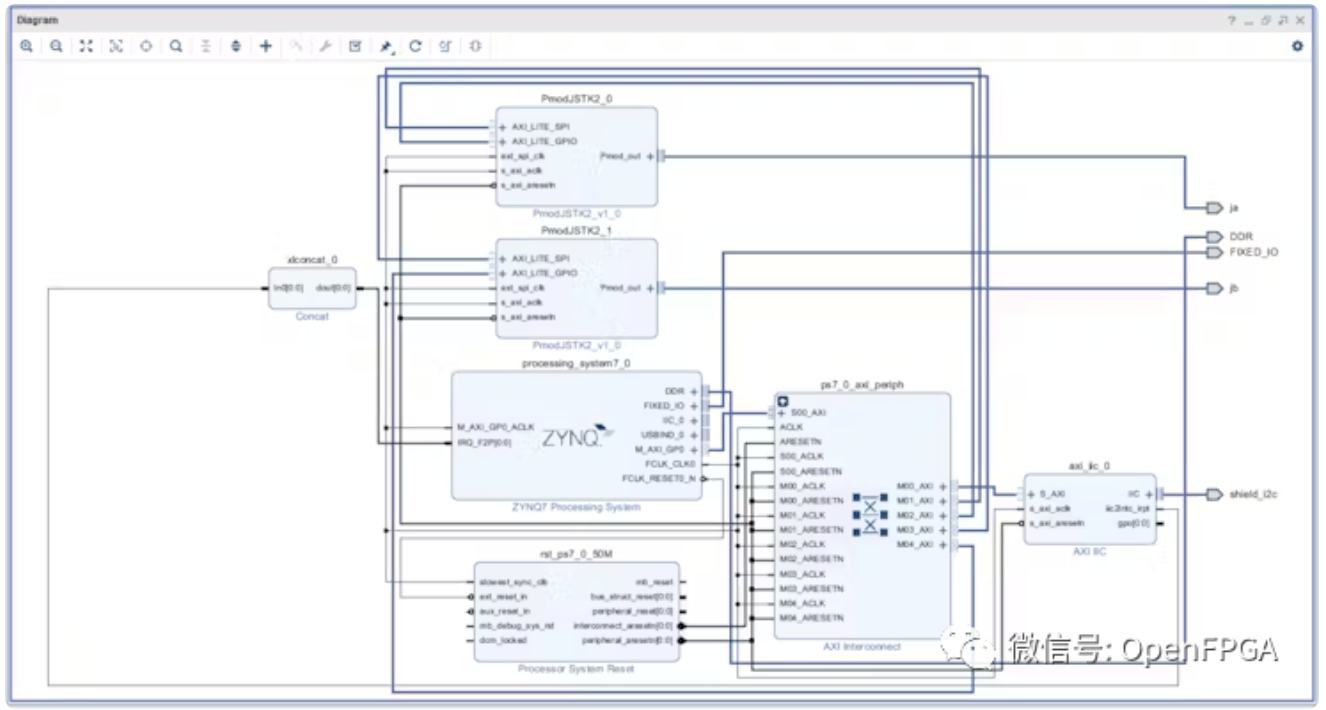

706 使用FPGA終端創建應用程序前,必須創建一個LabVIEW項目。然后添加FPGA終端至該項目并創建FPGA VI。

2017-11-18 02:47:23 2228

2228 可靠傳輸方面實現了MAC 層的流控以及錯誤包檢測功能。仿真以及實際平臺測試表明,該通信協議能夠實現FPGA 片間萬兆的線速通信。 云計算服務目前在互聯網上急速增長,其通過互聯網來提供動態易擴展的資源。

2017-11-18 08:13:01 15054

15054

針對空間輻照效應影響的高可靠性設計,將越來越成為FPGA軟硬件設計的難點和重點。根據飛行器空間軌道的不同、輻射總劑量的差異,從硬件上,可以通過加厚屏蔽層、元器件加固等方式,盡可能地降低SEU發生

2017-11-24 15:30:01 2294

2294 Intel 再次隆重介紹了自家的 Stratix 10 TX FPGA芯片 。 這是地球上最快的FPGA芯片,浮點性能達到10TFLOPS(每秒10萬億次),簡單來說,可以在1秒內處理420張藍光

2018-04-23 05:55:00 7830

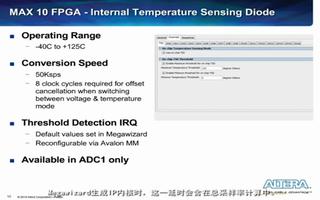

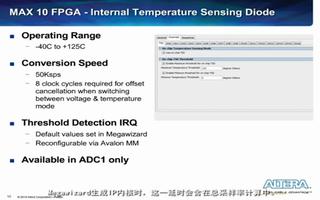

7830 MAX 10 FPGA模擬模塊培訓,此次培訓介紹MAX 10 FPGA中的ADC是怎樣工作的,怎樣對其進行配置,怎樣在硬件中測量其性能。

2018-06-20 12:00:00 4044

4044

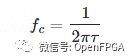

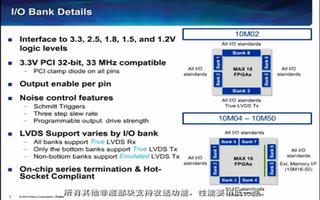

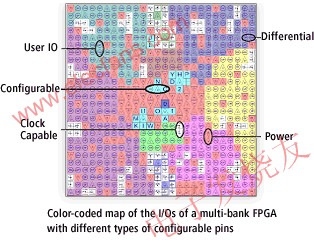

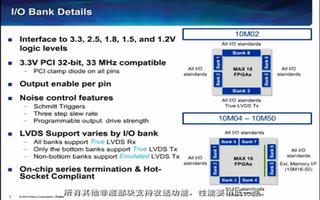

MAX 10 FPGA GPIO培訓,可編程邏輯一般用作膠合邏輯,連接電路板上的大量數字邏輯器件,這些器件通常有不同的I/O標準、電壓電平和協議。這里列出了我們I/O特性的很多優勢。MAX 10 FPGA支持多種I/O標準和特性,因此,與其他可編程邏輯方案相比,Altera是最佳選擇。

2018-06-20 05:00:00 2371

2371

此次培訓涉及到MAX 10 FPGA所支持的配置方法,介紹非易失集成、瞬時接通配置和雙配置鏡像的價值所在。

2018-06-20 08:00:00 2248

2248 如何創建英特爾 Stratix 10 后配置BSDL 文件

2018-06-22 10:09:00 2922

2922 本篇文章主要介紹在FPGA設計中如何使用本GXFPGA驅動創建一個中斷事件/請求。

中斷作為硬件與軟件握手和同步的手段而被廣泛使用,可用于表示硬件進程的完成或軟件執行過程中的請求。Gx3500

2018-09-07 14:34:18 6

6 FPGA的I / O優化提供了一個自動化的FPGA符號生成過程集成的原理圖和PCB設計,節省天的PCB設計創建時間的整體質量和準確性,同時增加你的原理圖符號。

2019-10-16 07:06:00 2292

2292 根據Tom's Hardware的報道,今天,英特爾推出了世界上最大的FPGA芯片Stratix 10 GX 10M,搭載433億個晶體管,擁有1020萬個邏輯元件,使用EMIB將兩個FPGA芯片和四個收發芯片連接在一起。

2019-11-07 14:32:19 4049

4049 在北京舉辦的 IntelFPGA 技術大會上,Intel 發布全球最大容量的全新 Stratix 10 GX 10M FPGA。這是全球密度最高的 FPGA,擁有 1020 萬個邏輯單元,433 億顆晶體管,現已量產,即日出貨。

2019-11-20 17:11:21 1026

1026 Microsoft將全力投入Windows 10,最終實現了擁有可跨平臺運行的應用程序的夢想。結合對Arduino的官方支持,您可以使用一個功能強大的新工具:能夠輕松創建具有與現實世界硬件連接的通用Windows應用程序的功能。

2019-12-03 08:53:13 2365

2365 本文檔的主要內容詳細介紹的是FPGA 10K10單片機配置的PCB原理圖免費下載。

2020-10-14 14:52:00 20

20 為實現高效可靠的網絡傳輸協議,依據RUDP草案并引人TCP可靠機制,設計一種基于消息包、面向連接的高速可靠網絡傳輸協議 ORUDP。通過創建確認機制、重傳機制、流量控制機制和雙隊列加速機制等實現

2021-03-31 15:47:18 16

16 中,小編為大家分別總結了英特爾 Cyclone FPGA和英特爾 Stratix 10 FPGA的應用之路,今天就輪到咱們的英特爾 Arria 10 FPGA了~ ? ? 英特爾 Arria 器件家族

2021-05-31 09:42:42 2704

2704 AGM FPGA之AG10K 系列的開發建議(連載二)

2021-12-05 17:21:14 25

25 (10)FPGA跨時鐘域處理1.1 目錄1)目錄2)FPGA簡介3)Verilog HDL簡介4)FPGA跨時鐘域處理5)結語1.2 FPGA簡介FPGA(Field Programmable

2021-12-29 19:40:35 7

7 BASIC 10 Liner Contest 的目標是用 10 行 BASIC 語言創建一個完整的電腦游戲。

2022-07-30 17:21:42 1555

1555

LiteX 框架為創建 FPGA 內核/SoC、探索各種數字設計架構和創建完整的基于 FPGA 的系統提供了方便高效的基礎架構。

2022-09-13 09:04:14 1179

1179 電子發燒友網站提供《安路科技SALEAGLES10 FPGA數據手冊.pdf》資料免費下載

2022-09-27 10:39:10 1

1 要求:創建10個普通用戶,并給它們設置隨機密碼,將密碼記錄到一個文檔里,用戶名為user_01 — user_10,密碼要求包含大小寫字母以及數字,密碼長度15位。

2022-10-31 09:14:51 1150

1150 電子發燒友網站提供《使用FPGA創建RISC V系統.zip》資料免費下載

2022-11-08 10:26:45 1

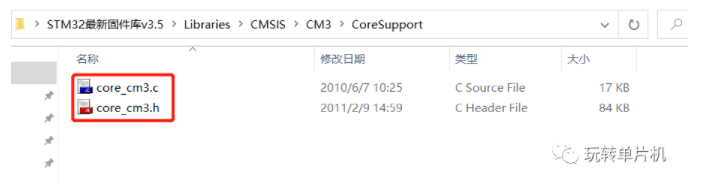

1 ?創建一個工程文件夾,并且在文件夾里創建三個文件夾并分別以CORE、STM32F10X_LIB、USER命名。

2023-02-10 14:38:55 841

841

proFPGA 四模塊英特爾 Stratix 10 GX 10M FPGA 原型設計系統采用 4 個基于英特爾 Stratix 10 GX 10M FPGA 的可插拔 FPGA 模塊。

2023-03-17 11:22:30 470

470 點擊藍字,關注我們購置了貴司E103-W10Wi-Fi模塊,不會創建UDP通信,怎么辦?不用擔心,E103-W10UDP使用示例教程附上。前期配置設置E103-W10的WiFi模式,連接到路由器

2022-05-27 10:52:00 1416

1416

LiteX 框架為創建 FPGA 內核/SoC、探索各種數字設計架構和創建完整的基于 FPGA 的系統提供了方便高效的基礎架構。

2023-06-28 09:08:05 425

425

FPGA 設計工程師需要對如何創建系統以及使用行業軟件和工具有深入的了解。在軟件方面,設計工程師必須知道如何建模自己的設計,并通過一系列測試保證正確的運行。業界有許多這種高級建模程序,包括Matlab,Simulink,Octave,Verdi等等。

2023-08-01 09:20:51 414

414 芯片設計和驗證工程師通常要為在硅片上實現的每一行RTL代碼寫出多達10行測試平臺代碼。驗證任務在設計周期內可能會占用50%或更多的時間。盡管如此辛 苦,仍有接近60%的芯片存在功能瑕疵,需要返工。由于HDL仿真不足以發現系統級錯誤,芯片設計人員正利用FPGA來加速算法創建和原型設計。

2023-08-06 10:49:09 977

977

本文開源一個FPGA高速串行通信項目:Aurora 8b10b光通信。7 Series FPGAs Transceivers Wizard IP是Xilinx官方7系列FPGA的高速串行收發器,本工程主要是圍繞該IP核采用Vivado提供的例程創建。

2023-10-01 09:48:00 2604

2604

機器人技術處于工業 4.0、人工智能和邊緣革命的前沿。讓我們看看如何創建 FPGA 控制的機器人手臂。

2023-10-24 17:15:33 456

456

機器人技術處于工業 4.0、人工智能和邊緣革命的前沿。讓我們看看如何創建 FPGA 控制的機器人手臂。

2023-10-24 17:26:20 935

935

如何創建二維數組在Python中是一個常見的問題。在Python中,我們可以使用嵌套的列表(list of lists)或者使用NumPy庫來創建二維數組。在本文中,我們將詳細介紹這兩種方法,以及

2023-11-21 15:10:43 830

830

電子發燒友App

電子發燒友App

評論