基于DSP+FPGA的實(shí)時(shí)視頻采集系統(tǒng)設(shè)計(jì)

0 引言

圖像是自然生物或人造物理的觀測(cè)系統(tǒng)對(duì)世界的記錄,是以物理為載體,以介質(zhì)來

2010-01-11 10:15:46 535

535 DSP+FPGA架構(gòu)的最大特點(diǎn)是結(jié)構(gòu)靈活、有較強(qiáng)的通用性、適合于模塊化設(shè)計(jì),從而能夠提高算法效率,同時(shí)其開發(fā)周期短、系統(tǒng)易于維護(hù)和升級(jí),適合于實(shí)時(shí)視頻圖像處理。

2015-02-03 15:20:47 1166

1166

基于DSP+FPGA的20路 50Msps AD 數(shù)據(jù)處理平臺(tái)1、板卡概述 該DSP+FPGA高速信號(hào)采集處理板由我公司自主研發(fā),包含一片TI DSP TMS320C6455和一片Xilinx

2014-06-24 14:01:53

本帖最后由 mr.pengyongche 于 2013-4-30 03:09 編輯

DSP+FPGA在高速高精運(yùn)動(dòng)控制器中的應(yīng)用 摘要:數(shù)字信號(hào)處理器具有高效的數(shù)值運(yùn)算能

2012-12-28 11:20:34

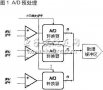

DSP+FPGA+AD控制系統(tǒng),FPGA負(fù)責(zé)AD7606的采集,將電機(jī)參數(shù)采集后,傳輸至DSP ,DSP將數(shù)據(jù)進(jìn)行變換后輸出PWM進(jìn)而控制電機(jī)的轉(zhuǎn)速。DSP采用TI公司的TMS320F28335

2016-07-18 16:59:22

DSP+FPGA架構(gòu)的最大特點(diǎn)是結(jié)構(gòu)靈活、有較強(qiáng)的通用性、適合于模塊化設(shè)計(jì),從而能夠提高算法效率,同時(shí)其開發(fā)周期短、系統(tǒng)易于維護(hù)和升級(jí),適合于實(shí)時(shí)視頻圖像處理,電機(jī)控制,數(shù)據(jù)采集。單DSP核心的系統(tǒng)

2016-09-24 10:41:18

`DSP+FPGA架構(gòu)的最大特點(diǎn)是結(jié)構(gòu)靈活、有較強(qiáng)的通用性、適合于模塊化設(shè)計(jì),從而能夠提高算法效率,同時(shí)其開發(fā)周期短、系統(tǒng)易于維護(hù)和升級(jí),適合于實(shí)時(shí)視頻圖像處理,電機(jī)控制,數(shù)據(jù)采集。單DSP核心

2016-09-01 15:41:48

`產(chǎn)品特點(diǎn)基于ZYNQ+并行DSP處理架構(gòu)處理架構(gòu)十分靈活,能夠滿足各類并行加速需求支持OpenCL編程,方便算法移植系統(tǒng)處理靈活:FPGA或DSP可選尺寸小巧,方便集成擴(kuò)展能力強(qiáng) 應(yīng)用領(lǐng)域并行控制

2017-06-08 10:33:07

DSP并行處理的方法摘 要:TI公司的TMS320C6x和AD公司的ADSP2106x是目前業(yè)界使用廣泛的數(shù)字信號(hào)處理器(DSP)。

2009-11-03 15:16:47

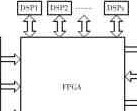

充當(dāng),利用DSP的HPI接口組成一個(gè)多DSP互 連并行系統(tǒng),一般是一個(gè)主處理器和一個(gè)從處理器,此種方法的一個(gè)應(yīng)用實(shí)例是在雷達(dá)中的應(yīng)用。滑窗算法是數(shù)字信號(hào)處理中一種常用的基本算法,但滑窗算法一般

2019-04-08 09:36:19

.FPGA+DSP的導(dǎo)引頭信號(hào)處理結(jié)構(gòu)成為當(dāng)前以及未來一段時(shí)間的主流。FPGA和DSP處理器具有截然不同的架構(gòu),在一種器件上非常有效的算法.在另一種器件上可能效率會(huì)非常低。如果目標(biāo)要求大量的并行處理或者最大

2019-08-30 06:31:29

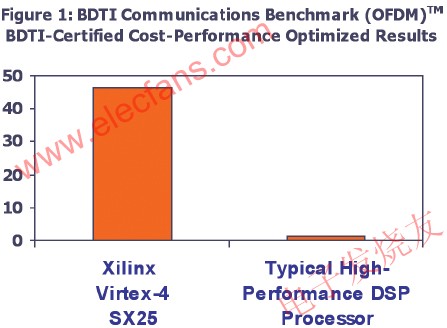

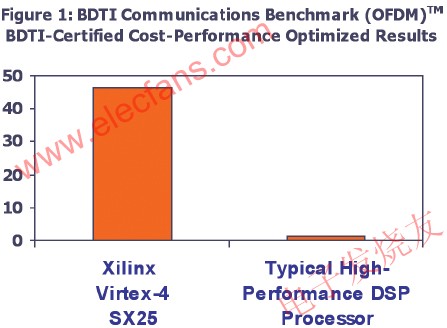

FPGA在高性能數(shù)字信號(hào)處理領(lǐng)域越來越受關(guān)注,如無線基站。在這些應(yīng)用中, FPGAs通常被用來和DSP處理器并行工作。有更多的選擇當(dāng)然是好的,但這也意味著系統(tǒng)設(shè)計(jì)師需要一個(gè)確切的FPGAs及高端DSP信號(hào)處理器性能參數(shù)圖。不幸的是,常用的參數(shù)圖在這種情況下都是不可靠的。

2019-09-25 08:17:27

FPGA在高性能數(shù)字信號(hào)處理領(lǐng)域越來越受關(guān)注,如無線基站。在這些應(yīng)用中, FPGAs通常被用來和DSP處理器并行工作。有更多的選擇當(dāng)然是好的,但這也意味著系統(tǒng)設(shè)計(jì)師需要一個(gè)確切的FPGAs及高端DSP信號(hào)處理器性能參數(shù)圖。不幸的是,常用的參數(shù)圖在這種情況下都是不可靠的。

2019-08-23 06:40:44

設(shè)計(jì),所以設(shè)計(jì)者應(yīng)該處理好工具的掌握和具體設(shè)計(jì)的區(qū)別。但是不可忽視的是,DSP+FPGA處理系統(tǒng)正廣泛應(yīng)用于復(fù)雜的信號(hào)處理領(lǐng)域。在雷達(dá)信號(hào)處理、數(shù)字圖像處理等領(lǐng)域中,信號(hào)處理的實(shí)時(shí)性至關(guān)重要。由于

2014-01-09 17:52:31

FPGA的并行多通道激勵(lì)信號(hào)產(chǎn)生模塊FPGA的并行多通道激勵(lì)信號(hào)產(chǎn)生模塊.docx

2012-08-11 10:35:50

相位、多抽樣率處理、級(jí)聯(lián)、易于存儲(chǔ)等;可用于頻率非常低的信號(hào)。項(xiàng)目描述:在借鑒和吸收國(guó)內(nèi)外示波器技術(shù)的基礎(chǔ)上,設(shè)計(jì)了基于DSP的50MHz的數(shù)字示波器。本系統(tǒng)采用了DSP+FPGA的結(jié)構(gòu),充分利用

2015-09-10 11:15:17

和處理系統(tǒng)。該系統(tǒng)以DSP+FPGA 為核心,實(shí)現(xiàn)信號(hào)處理系統(tǒng)的功能,解決系統(tǒng)遇到的問題。項(xiàng)目描述:隨著海洋開發(fā)利用的發(fā)展以及中國(guó)海洋安全情況的日益嚴(yán)峻,對(duì)海洋環(huán)境的探測(cè)得到越來越多的關(guān)注。多波束測(cè)深

2015-11-06 09:55:43

飛控計(jì)算機(jī)平臺(tái)尤為重要。傳統(tǒng)的單處理器核心飛控計(jì)算機(jī)難以在多通道異步數(shù)據(jù)收發(fā)的同時(shí)保證數(shù)據(jù)處理速度,難以滿足現(xiàn)代導(dǎo)彈的要求。本文提出了一種基于DSP+FPGA結(jié)構(gòu),對(duì)外接口為422的通用數(shù)字飛控計(jì)算機(jī)

2019-06-26 07:29:55

FPGA進(jìn)行硬件實(shí)現(xiàn),這樣能兼顧速度及靈活性。高層的處理算法結(jié)構(gòu)復(fù)雜,適用于運(yùn)算速度高、尋址方式靈活、通信機(jī)制強(qiáng)的DSP芯片宋實(shí)現(xiàn)。DSP+FPGA架構(gòu)的最大特點(diǎn)是結(jié)構(gòu)靈活、有較強(qiáng)的通用性、適合于模塊

2019-07-01 07:38:06

FPGA一般用來控制整個(gè)系統(tǒng)的時(shí)序,本設(shè)計(jì)采用集成微處理器的FPGA,同時(shí)完成信號(hào)模擬和時(shí)序控制的功能,改變了以往信號(hào)處理DSP+FPGA中FPGA作為協(xié)處理器的模式[1-3]。整個(gè)設(shè)計(jì)僅需要具有嵌入

2019-07-10 07:30:35

本帖最后由 mr.pengyongche 于 2013-4-30 03:00 編輯

這是華中科技大學(xué)一篇關(guān)于dsp+fpga直線電機(jī)伺服驅(qū)動(dòng)的論文。希望對(duì)這方面科研的同學(xué)有幫

2013-03-22 17:21:46

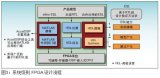

SEED-HPS6678(HPS6678)是北京艾睿合眾科技有限公司新推出的新一代高端DSP+FPGA應(yīng)用方案。DSP采用TI公司首顆最高主頻為10GHz的8核浮點(diǎn)DSP芯片TMS320C6678

2019-09-24 08:29:12

DSP技術(shù)廣泛應(yīng)用于各個(gè)領(lǐng)域,但傳統(tǒng)的數(shù)字信號(hào)處理器由于以順序方式工作使得數(shù)據(jù)處理速度較低,且在功能重構(gòu)及應(yīng)用目標(biāo)的修改方面缺乏靈活性。而使用具有并行處理特性的FPGA實(shí)現(xiàn)數(shù)字信號(hào)處理系統(tǒng),具有很強(qiáng)的實(shí)時(shí)性和靈活性,因此利用FPGA實(shí)現(xiàn)數(shù)字信號(hào)處理成為數(shù)字信號(hào)處理領(lǐng)域的一種新的趨勢(shì)。

2019-10-17 08:12:27

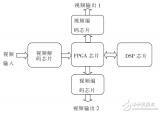

有限的不足,而且提高了監(jiān)控資源的利用率,降低了監(jiān)控成本。 1 系統(tǒng)硬件結(jié)構(gòu) 采用DSP+FPGA的硬件結(jié)構(gòu)方案,利用DSP和FPGA控制MAX4312選通所需要的視頻通道,從而達(dá)到在多路視頻通道間進(jìn)行切換的目的。系統(tǒng)結(jié)構(gòu)框圖如

2012-12-12 17:00:21

會(huì)受一定的影響。?本文所提出的基于DSP+FPGA的控制系統(tǒng)方案,利用FPGA的容量大、可編程實(shí)現(xiàn)很多功能,結(jié)合DSP具有高速的信息處理能力的特點(diǎn),使得本控制系統(tǒng)非常簡(jiǎn)潔,結(jié)構(gòu)靈活,通用性強(qiáng),系統(tǒng)也易于維護(hù)和擴(kuò)展。該方案基于軟件無線電的思想,是采用通用平臺(tái)的設(shè)計(jì)。?

2019-07-29 06:08:47

ASIC不夠靈活的缺點(diǎn)。與其他中小規(guī)模集成電路相比,其優(yōu)點(diǎn)主要在于它有很強(qiáng)的靈活性,即其內(nèi)部的具體邏輯功能可以根據(jù)需要配置,對(duì)電路的修改和維護(hù)很方便。DSP+FPGA結(jié)構(gòu)最大的特點(diǎn)是結(jié)構(gòu)靈活,有較強(qiáng)

2019-09-19 08:21:16

的重點(diǎn)是以DSP+FPGA為核心的視頻處理模塊的設(shè)計(jì)與實(shí)現(xiàn),可以完成多路視頻的切換選擇輸出控制和視頻縮放顯示的功能,同時(shí)具備通信控制等功能。

2019-06-20 06:34:25

FPGA一般用來控制整個(gè)系統(tǒng)的時(shí)序,本設(shè)計(jì)采用集成微處理器的FPGA,同時(shí)完成信號(hào)模擬和時(shí)序控制的功能,改變了以往信號(hào)處理DSP+FPGA中FPGA作為協(xié)處理器的模式[1-3]。整個(gè)設(shè)計(jì)僅需要具有嵌入

2019-07-15 06:48:33

)的FIFO模塊設(shè)計(jì),容量為負(fù)責(zé)存儲(chǔ)高速A/D轉(zhuǎn)換器轉(zhuǎn)換過來的并行12位數(shù)據(jù),供DSP進(jìn)行數(shù)據(jù)處理。系統(tǒng)的工作時(shí)鐘是65 MHz,在實(shí)現(xiàn)該模塊時(shí),調(diào)用COREGenerator來天生FIFO,通過

2018-08-15 09:43:14

隨著信息技術(shù)和芯片技術(shù)的發(fā)展,DSP技術(shù)在航空、通信、醫(yī)療和消費(fèi)類電子設(shè)備中得到廣泛應(yīng)用。伴隨主頻不斷提升及多核并行工作,DSP芯片的運(yùn)算能力快速增強(qiáng)。運(yùn)用DSP芯片快速設(shè)計(jì)多類信號(hào)多路并行處理

2012-09-03 17:18:51

用FPGA進(jìn)行硬件實(shí)現(xiàn),這樣能兼顧速度及靈活性。高層的處理算法結(jié)構(gòu)復(fù)雜,適用于運(yùn)算速度高、尋址方式靈活、通信機(jī)制強(qiáng)的DSP芯片宋實(shí)現(xiàn)。 DSP+FPGA架構(gòu)的最大特點(diǎn)是結(jié)構(gòu)靈活、有較強(qiáng)的通用性

2019-06-28 08:10:26

用FPGA進(jìn)行硬件實(shí)現(xiàn),這樣能兼顧速度及靈活性。高層的處理算法結(jié)構(gòu)復(fù)雜,適用于運(yùn)算速度高、尋址方式靈活、通信機(jī)制強(qiáng)的DSP芯片宋實(shí)現(xiàn)。 DSP+FPGA架構(gòu)的最大特點(diǎn)是結(jié)構(gòu)靈活、有較強(qiáng)的通用性

2019-06-19 06:12:05

后給并行DSP輸出中斷。當(dāng)并行DSP采樣到中斷后,從數(shù)據(jù)緩存區(qū)讀取數(shù)據(jù),完成處理后,將數(shù)據(jù)傳輸?shù)骄彺?區(qū),FPGA再通過相同的處理方式經(jīng)CPCI接口的J1口和J2口將數(shù)據(jù)傳輸?shù)嚼走_(dá)系統(tǒng)的其他功能模塊

2019-05-21 05:00:19

FPGA在高性能數(shù)字信號(hào)處理領(lǐng)域越來越受關(guān)注,如無線基站。在這些應(yīng)用中, FPGAs通常被用來和DSP處理器并行工作。有更多的選擇當(dāng)然是好的,但這也意味著系統(tǒng)設(shè)計(jì)師需要一個(gè)確切的FPGAs及高端DSP信號(hào)處理器性能參數(shù)圖。不幸的是,常用的參數(shù)圖在這種情況下都是不可靠的。

2019-10-12 06:40:30

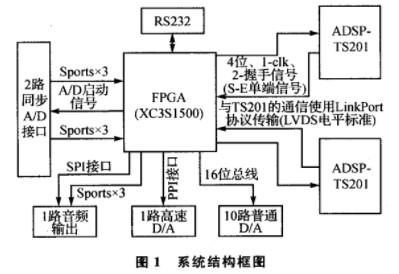

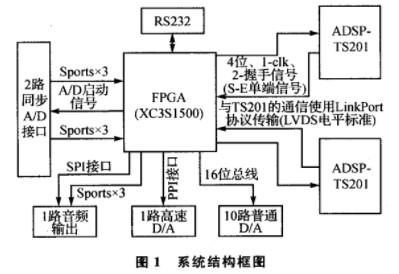

在雷達(dá)信號(hào)處理、數(shù)字圖像處理等領(lǐng)域中,信號(hào)處理的實(shí)時(shí)性至關(guān)重要。由于FPGA芯片在大數(shù)據(jù)量的底層算法處理上的優(yōu)勢(shì)及DSP芯片在復(fù)雜算法處理上的優(yōu)勢(shì),DSP+FPGA的實(shí)時(shí)信號(hào)處理系統(tǒng)的應(yīng)用越來越廣泛。那么,我們?cè)撛趺蠢?b class="flag-6" style="color: red">FPGA與ADSP TS201設(shè)計(jì)總線接口呢?

2019-08-09 06:56:11

您可以顯著提高無線系統(tǒng)中信號(hào)處理功能的性能。怎樣提高呢?有效方法是利用FPGA結(jié)構(gòu)的靈活性和目前受益于并行處理的FPGA架構(gòu)中的嵌入式DSP模塊。

2019-10-23 07:04:22

、成本上的優(yōu)勢(shì)是巨大的。 除了上述兩種方案,還有DSP+FPGA方案,以及選擇內(nèi)部嵌入DSP模塊的FPGA實(shí)現(xiàn)系統(tǒng)的方案。

2019-06-19 08:02:03

本文以并行多通道信號(hào)產(chǎn)生模型為依據(jù),設(shè)計(jì)并實(shí)現(xiàn)了以FPGA為核心器件的并行多通道信號(hào)產(chǎn)生模塊,主要包括FPGA系統(tǒng)設(shè)計(jì)和多通道波形產(chǎn)生模塊設(shè)計(jì)。通過模塊測(cè)試后發(fā)現(xiàn),該模塊具備產(chǎn)生高質(zhì)量并行多通道激勵(lì)信號(hào)的能力。

2021-04-29 06:17:38

您可以顯著提高無線系統(tǒng)中信號(hào)處理功能的性能。怎樣提高呢?有效方法是利用FPGA結(jié)構(gòu)的靈活性和目前受益于并行處理的FPGA架構(gòu)中的嵌入式DSP模塊。

2019-09-19 07:50:50

;nbsp; 在有限的空間內(nèi)集成了ADC技術(shù)和基于FPGA與DSP數(shù)字信號(hào)處理器技術(shù)的功能模塊,ADC控制、FPGA和DSP信號(hào)處理等均可對(duì)應(yīng)用開放,通過擴(kuò)充外圍子卡增加濾波、增益等信號(hào)

2010-02-05 15:04:28

請(qǐng)教電力電子方向里dsp+FPGA架構(gòu)的案例

2018-12-10 18:32:58

=transparent]一、板卡概述 該DSP+FPGA高速信號(hào)采集處理板由我公司自主研發(fā),包含一片TI DSP TMS320C6657和一片Xilinx K7 FPGA

2018-06-01 17:48:37

您可以顯著提高無線系統(tǒng)中信號(hào)處理功能的性能。怎樣提高呢?有效方法是利用FPGA結(jié)構(gòu)的靈活性和目前受益于并行處理的FPGA架構(gòu)中的嵌入式DSP模塊。常見于無線應(yīng)用中這類處理包括有限沖激響應(yīng)(FIR

2019-07-15 06:18:56

基于VxWorks的多DSP并行處理系統(tǒng)的實(shí)現(xiàn)

2009-03-29 12:31:18 17

17 InterWiser RFSOC+TMS320C6678 DSP數(shù)模混和信號(hào)處理模塊設(shè)計(jì)用于集成到需要小尺寸,低功耗和實(shí)時(shí)處理的已部署RF系統(tǒng)中,Xilinx ZYNQ UltraScale

2022-09-28 17:34:19

設(shè)計(jì)了一種基于FPGA 和DSP 的光纖信號(hào)實(shí)時(shí)處理系統(tǒng),介紹了系統(tǒng)的硬件組成和工作原理。該系統(tǒng)采用FPGA 實(shí)現(xiàn)數(shù)據(jù)的高速采集和邏輯控制,用DSP 實(shí)現(xiàn)傳感信號(hào)的全數(shù)字解調(diào),分析了載

2009-06-19 11:17:43 24

24 簡(jiǎn)要分析了DSP+FPGA系統(tǒng)的特點(diǎn)和優(yōu)越性,并且結(jié)合一個(gè)實(shí)時(shí)信號(hào)處理板的開發(fā),提出在此類系統(tǒng)中,FPGA設(shè)計(jì)的幾個(gè)關(guān)鍵問題,并且給出了詳實(shí)的分析和解決方案。

2009-09-02 17:44:44 24

24 簡(jiǎn)要分析了DSP+FPGA 系統(tǒng)的特點(diǎn)和優(yōu)越性,結(jié)合導(dǎo)引頭信號(hào)處理板的開發(fā),提出了在此系統(tǒng)中,FPGA 設(shè)計(jì)的幾個(gè)關(guān)鍵技術(shù),并且給出了詳實(shí)的分析和解決方案。

2009-12-23 14:53:54 20

20 為了在梳棉機(jī)上實(shí)現(xiàn)在線檢測(cè)監(jiān)控棉網(wǎng)中的棉結(jié)雜質(zhì),提出了一種基于DSP+FPGA架構(gòu)的硬件圖像處理在線檢測(cè)裝置,取代傳統(tǒng)的PC-Base檢測(cè)模式;采用符合梳棉機(jī)機(jī)械結(jié)構(gòu)的光源設(shè)計(jì)和控制

2010-02-24 14:06:05 18

18 對(duì)于嵌入式折反射全景視頻處理系統(tǒng),由于計(jì)算量大,一般采用多處理器協(xié)同的結(jié)構(gòu),但在該結(jié)構(gòu)下多個(gè)處理器之間需要進(jìn)行高速的數(shù)據(jù)通信。該文提出一種基于DSP+FPGA 架構(gòu)的雙核

2010-03-06 11:03:46 10

10 為了在梳棉機(jī)上實(shí)現(xiàn)在線檢測(cè)監(jiān)控棉網(wǎng)中的棉結(jié)雜質(zhì),提出了一種基于DSP+FPGA架構(gòu)的硬件圖像處理在線檢測(cè)裝置,取代傳統(tǒng)的PC-Base檢測(cè)模式;采用符合梳棉機(jī)機(jī)械結(jié)構(gòu)的光源設(shè)計(jì)和控制

2010-07-17 17:25:09 10

10 簡(jiǎn)要分析了DSP+FPGA系統(tǒng)的特點(diǎn)和優(yōu)越性,結(jié)合導(dǎo)引頭信號(hào)處理板的開發(fā),提出了在此系統(tǒng)中,FPGA設(shè)計(jì)的幾個(gè)關(guān)鍵技術(shù),并且給出了詳實(shí)的分析和解決方案。

2010-07-21 17:28:04 18

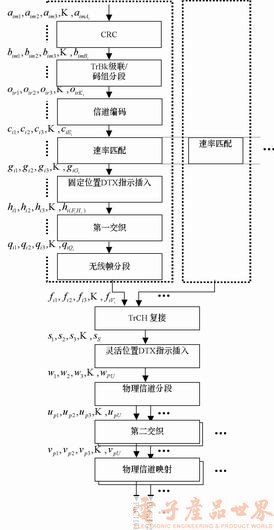

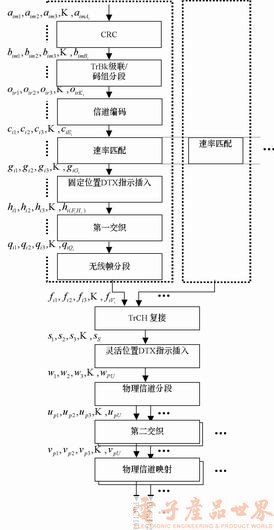

18 摘? 要: 本文在分析WCDMA系統(tǒng)基帶處理方案的基礎(chǔ)上,結(jié)合DSP和FPGA性能的比較,提出了一種在性能、靈活性和性價(jià)比上都比較理想的DSP+FPGA基帶發(fā)送的實(shí)現(xiàn)方案。 引言 隨

2006-03-11 13:29:42 670

670

基于DSP+FPGA的實(shí)時(shí)視頻采集系統(tǒng)設(shè)計(jì)

0 引言

圖像是自然生物或人造物理的觀測(cè)系統(tǒng)對(duì)世界的記錄,是以物理為載體,以介質(zhì)來記錄信息的

2009-12-16 10:20:55 576

576

一種基于DSP+FPGA的控制系統(tǒng)方案設(shè)計(jì)

一、前言 ?

本文提到的控制系統(tǒng)控制通信設(shè)備的正常工作,是整個(gè)通信設(shè)備的重要組成部分。該控制系統(tǒng)要實(shí)現(xiàn)的功能

2009-12-22 17:44:41 870

870

基于DSP與FPGA的光柵地震檢波器的信號(hào)處理

0 引 言

在石油地震勘探中,地震儀通過地震檢波器采集信號(hào)。地震檢波器是為了接收和記錄地

2010-01-20 11:26:15 719

719

信號(hào)處理器(DSP),信號(hào)處理器(DSP)是什么意思

DSP是(digital signal processor)的簡(jiǎn)稱,是一種專門用來實(shí)現(xiàn)信號(hào)處理算法的微處理器芯片

2010-03-26 14:53:54 15467

15467 FPGA在高性能數(shù)字信號(hào)處理領(lǐng)域越來越受關(guān)注,如無線基站。在這些應(yīng)用中, FPGAs通常被用來和DSP處理器并行工作。有更多的選擇當(dāng)然

2010-10-09 16:36:07 3284

3284

目前的衛(wèi)星遙感圖像壓縮系統(tǒng)硬件方案大多基于高性能可編程邏輯器件FPGA[2-4]。但這種方案整系統(tǒng)成本居高不下,且FPGA存在單粒子翻轉(zhuǎn)效應(yīng)。因此,筆者提出一種多DSP+FPGA的

2010-11-27 10:35:05 1386

1386

摘要:針對(duì)激光回波脈沖窄、弱等缺點(diǎn),提出數(shù)字信號(hào)處理技術(shù)檢測(cè)目標(biāo)的方法;該方法首先采用小波闡值去噪方法對(duì)激光回波弱信號(hào)進(jìn)行濾波,然后利用激光回波信號(hào)之間的相關(guān)性,對(duì)濾波后的潛在目標(biāo)進(jìn)行目標(biāo)匹配,檢測(cè)出目標(biāo),整個(gè)系統(tǒng)采用高速數(shù)字信號(hào)處理器(DSP)

2011-02-25 12:30:12 68

68 應(yīng)用領(lǐng)域: 6U VME TigerSHARC201FPGA信號(hào)處理機(jī)主要面向雷達(dá)、聲納、通信、圖象處理等高速信號(hào)處理領(lǐng)域。采用專用DSP與FPGA可編程邏輯器組成陣列化并行處理機(jī),已經(jīng)越來越成為當(dāng)前數(shù)字信號(hào)處理發(fā)展的趨勢(shì)。 雷航科技的6U VME TigerSHARC201FPGA信號(hào)處理機(jī)就

2011-02-28 12:05:32 64

64 摘要:本文在分析TD-SCDMA系統(tǒng)基帶處理方案的基礎(chǔ)上,提出了一種在性能、靈活性和性價(jià)比方面都比較理想的DSP+FPGA基帶發(fā)送的實(shí)現(xiàn)方案。 關(guān)鍵詞:TD-SCDMA;基帶處理;DSP;FPGA

2011-03-02 01:38:41 60

60 提出了~種基于StarFabric互聯(lián)的并行雷達(dá)信號(hào)處理機(jī)構(gòu)架,并對(duì)其進(jìn)行了建模,分析了StarFabric網(wǎng)絡(luò)傳輸性能,設(shè)計(jì)了其中的數(shù)字信號(hào)處理(DSP)模塊和其它模塊.DSP模塊集成8片C64x DSP和2

2011-08-26 14:30:13 17

17 DSP+FPGA混用設(shè)計(jì) 為了提高算法效率,實(shí)時(shí)處理圖像信息,本處理系統(tǒng)是基于DSP+FPGA混用結(jié)構(gòu)設(shè)計(jì)的。本系統(tǒng)要求DSP可以滿足算法控制結(jié)構(gòu)復(fù)雜、運(yùn)算速度高、尋址靈活、通信能力強(qiáng)大的

2011-09-08 11:55:37 1550

1550

在雷達(dá)信號(hào)處理、數(shù)字圖像處理等領(lǐng)域中,信號(hào)處理的實(shí)時(shí)性至關(guān)重要。由于FPGA芯片在大數(shù)據(jù)量的底層算法處理上的優(yōu)勢(shì)及DSP芯片在復(fù)雜算法處理上的優(yōu)勢(shì),DSP+FPGA的實(shí)時(shí)信號(hào)處理系統(tǒng)

2012-07-05 15:01:40 7272

7272

介紹了一種基于DSP和FPGA的磁鐵電源控制器的設(shè)計(jì)方案,闡述了該控制器硬件系統(tǒng)的組成,包括信號(hào)調(diào)理電路、中間數(shù)據(jù)處理部分、后端的驅(qū)動(dòng)電路。同時(shí)給出了DSP和FPGA之間通過SPI接口

2012-07-27 16:20:31 36

36 本文提出一種基于DSP/BIOS的軟件架構(gòu),可提高軟件的可維護(hù)性和可重用性,方便算法的裁減添加及程序的跨平臺(tái)移植,實(shí)現(xiàn)多類信號(hào)多路并行處理的軟件快速開發(fā)設(shè)計(jì)。

2012-09-03 16:59:44 1544

1544

為了提高算法效率,實(shí)時(shí)處理圖像信息,本處理系統(tǒng)是基于DSP+FPGA混用結(jié)構(gòu)設(shè)計(jì)的。業(yè)務(wù)板以FPGA為處理核心,實(shí)現(xiàn)數(shù)字視頻信號(hào)的實(shí)時(shí)圖像處理,DSP實(shí)現(xiàn)了部分的圖像處理算法和FPGA的控

2012-10-16 11:02:47 2706

2706

為了實(shí)現(xiàn)電控噴油霧化檢測(cè)快速測(cè)量和處理大量的數(shù)據(jù)的要求,設(shè)計(jì)一種基于DSP和FPGA信號(hào)控制與實(shí)時(shí)數(shù)據(jù)處理系統(tǒng)的通信模塊。該通信模塊硬件部分主要用來實(shí)現(xiàn)開發(fā)板GN0204中DSP與FP

2013-08-07 19:26:49 35

35 基于DSP_FPGA的LFMCW雷達(dá)測(cè)距信號(hào)處理系統(tǒng)設(shè)計(jì)_陳林軍

2017-03-19 19:07:17 4

4 本文介紹了基于DSP和FPGA的編碼器信號(hào)測(cè)量及處理的通用模塊,對(duì)海德漢編碼器進(jìn)行了概述等。

2017-10-13 18:17:29 19

19 基于FPGA和多DSP的多總線并行處理器設(shè)計(jì)

2017-10-19 13:40:31 4

4 光纖陀螺信號(hào)處理電路中FPGA與DSP的接口方法研究

2017-10-20 08:40:25 2

2 基于DSP和FPGA的模塊化實(shí)時(shí)圖像處理系統(tǒng)設(shè)計(jì)

2017-10-23 14:09:42 9

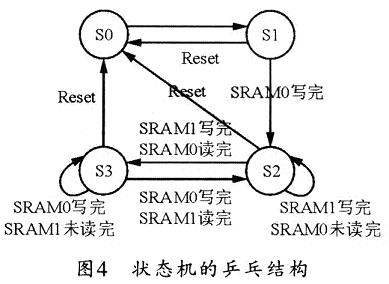

9 要求,因此,需采用專用的數(shù)字信號(hào)處理器(DSP)來進(jìn)行高速運(yùn)算。盡管當(dāng)前的數(shù)字信號(hào)處理器已達(dá)到較高水平, 但單片DSP芯片的處理能力還是不能滿足寬帶雷達(dá)的性能要求,需要引入并行處理技術(shù),在本設(shè)計(jì)中使用4片DSP芯片組成并行處理

2017-10-31 09:58:04 0

0 等突出優(yōu)點(diǎn),特別是在夜間、霧天及能見度不良、通視度較差的情況或者復(fù)雜電磁環(huán)境下,是戰(zhàn)場(chǎng)信息感知不可缺少的重要手段之一。 并行DSP處理的目的是采用多個(gè)處理單元(DSP)同時(shí)對(duì)任務(wù)處理以減少任務(wù)的執(zhí)行時(shí)間。多DSP并行處

2017-10-31 11:50:02 0

0 共享與鏈路口混合耦合的多DSP并行處理系統(tǒng)方案。在設(shè)計(jì)中,利用FPGA實(shí)現(xiàn)數(shù)據(jù)傳輸和CPCI接口的邏輯控制。經(jīng)驗(yàn)證,該系統(tǒng)具有運(yùn)算能力強(qiáng)、片間通信靈活、并行處理效率高等優(yōu)點(diǎn)。 關(guān)鍵詞:多DSP并行系統(tǒng);ADSP-TS201S;FPGA;CPCI接口 0 引言 在寬帶雷達(dá)信號(hào)處理中,存在諸如回波

2017-10-31 16:41:04 0

0 您可以顯著提高無線系統(tǒng)中信號(hào)處理功能的性能。怎樣提高呢?有效方法是利用FPGA結(jié)構(gòu)的靈活性和目前受益于并行處理的FPGA架構(gòu)中的嵌入式DSP模塊。

2018-07-17 11:48:00 710

710

本文主要介紹了一種基于DSP+FPGA的實(shí)時(shí)圖像去霧增強(qiáng)系統(tǒng)設(shè)計(jì),FPGA通常作為一種調(diào)度使用,圖像處理算法實(shí)現(xiàn)主要靠高速處理信號(hào)處理芯片DSP完成,在跟蹤等領(lǐng)域圖像數(shù)據(jù)只需單向進(jìn)入DSP,處理后輸出相應(yīng)參數(shù)即可,在實(shí)時(shí)視頻圖像處理中大量圖像數(shù)據(jù)只需通過EMIF輸入,且輸出數(shù)據(jù)量較小可以實(shí)時(shí)完成。

2017-12-25 10:24:21 3380

3380

本文主要介紹了一種基于DSP+FPGA視頻圖像采集處理系統(tǒng)的設(shè)計(jì)與實(shí)現(xiàn),DSP-BF561作為主處理器,負(fù)責(zé)整個(gè)算法的調(diào)度和數(shù)據(jù)流的控制,完成圖像數(shù)據(jù)的采集與顯示及核心算法的實(shí)現(xiàn),FPGA作為DSP的協(xié)處理器,依托其高度的并行處理能力,完成圖像預(yù)處理中大量的累乘加運(yùn)算。實(shí)驗(yàn)證明系統(tǒng)達(dá)到了實(shí)時(shí)性要求。

2017-12-25 10:39:47 4504

4504

本系統(tǒng)以FPGA作為高性能實(shí)時(shí)信號(hào)處理系統(tǒng)的數(shù)據(jù)采集和控制中心,2片DSP為數(shù)據(jù)處理中心,主要包括4個(gè)功能模塊——數(shù)據(jù)采集模塊、FPGA數(shù)據(jù)控制模塊、DSP處理模塊和通信模塊,系統(tǒng)結(jié)構(gòu)框圖如圖1所示。

2019-04-23 08:29:00 3426

3426

設(shè)計(jì)了一種基于 TI DSP TMS320C6713B 和ALtera Cyclone 系列FPGA 的數(shù)據(jù)采集模塊,使用FPGA 做多路串行AD 器件的信號(hào)采集控制和數(shù)據(jù)緩沖,同時(shí)利用DSP

2019-03-05 16:30:29 16

16 CPCI6U-2DSP-C6678 信號(hào)處理板基于 6U CPCI 規(guī)范,并且具有一個(gè)基于FMC 規(guī)范的 HPC 接口。信號(hào)處理板采用雙 DSP+FPGA 的處理架構(gòu),DSP 采用 TI 公司

2019-03-19 08:00:00 17

17 創(chuàng)龍結(jié)合TI KeyStone系列多核架構(gòu)TMS320C6678及Xilinx Kintex-7系列FPGA設(shè)計(jì)的TL6678F-EasyEVM開發(fā)板是一款DSP+FPGA高速大數(shù)據(jù)采集處理平臺(tái)

2020-02-12 13:42:30 3657

3657 基于FPGA+DSP彈載SAR信號(hào)處理系統(tǒng)設(shè)計(jì)

2021-12-27 18:58:51 21

21

正在加载...

電子發(fā)燒友App

電子發(fā)燒友App

評(píng)論