摘 要:介紹了基于可編程邏輯門陣列(FPGA)的能量倍增器(SLED)相位翻轉系統。該系統主要由微波IQ調制器、FPGA 和高速DAC 組成。在FPGA 的控制下,DAC 輸出兩路雙極性脈沖電平信號,加載于調制器的IQ 端,將微波連續波輸入信號轉變為4μs脈沖輸出信號,并且在3μs時刻微波相位發生180°跳變。經測試,相位翻轉精度為180°±2°,翻轉相位的長期穩定度優于±0.5°;相位翻轉系統驅動的6臺SLED 的輸出功率增益均超過7dB,最高達到7.54dB,增益的長期穩定度達到±0.1dB。

?

在合肥光源(HLS)重大升級改造工程中,為了實現儲存環滿能量注入,直線加速器的能量從200MeV 升級到800MeV。速調管功率源從5個增加到8個,其中80 MW 速調管2個(1#,8#),50 MW 速調管6個(2#~7#)。每個速調管驅動2根3m 等梯度加速管,構成一個加速段。2#~7# 微波系統中安裝了能量倍增器(SLED),全部啟用可將電子能量提高到1GeV。能量倍增器是一種RF脈沖能量壓縮裝置,可將RF長脈沖壓縮為高峰值的短脈沖。能量倍增器工作時,輸入微波信號需要在脈沖內進行快速相位翻轉,為此我們研制了基于FPGA 和IQ調制器的相位翻轉系統。

1 能量倍增系統的總體參數設計

HLS的SLED是由中國科學院高能物理研究所研制,主要技術指標見表1。6臺SLED和低電平相位翻轉系統的布局如圖1所示。

圖1 800 MeV 直線加速器布局圖

HLS SLED設計為將4μs功率脈沖壓縮為1μs,即速調管輸出3μs脈沖功率后,微波相位立即跳變180°,并持續1μs。在兩個儲能腔調諧一致和微波相位翻轉180°的理想狀態下,SLED的理論設計增益可達到7.8dB。依據800MeV 直線加速器的總體設計方案,SLED的增益指標為不低于7dB,增益設計值與實際工作值之間有較大余量,因此可適當放寬相位翻轉系統的絕對精度要求。但為了保證脈沖間直線加速器電子束能量的一致性和穩定性,相位翻轉必須在脈沖間保持高度的一致。相位翻轉系統的基本設計指標為:相位翻轉精度為180°±2°,翻轉相位的長期穩定度為±0.5°。整個能量倍增系統的考核指標為:峰值能量增益大于7dB,增益的長期穩定度達到±0.1dB。

2 相位翻轉系統結構設計

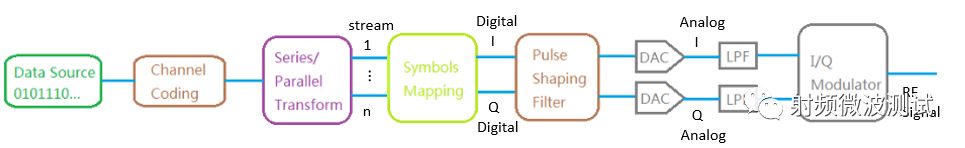

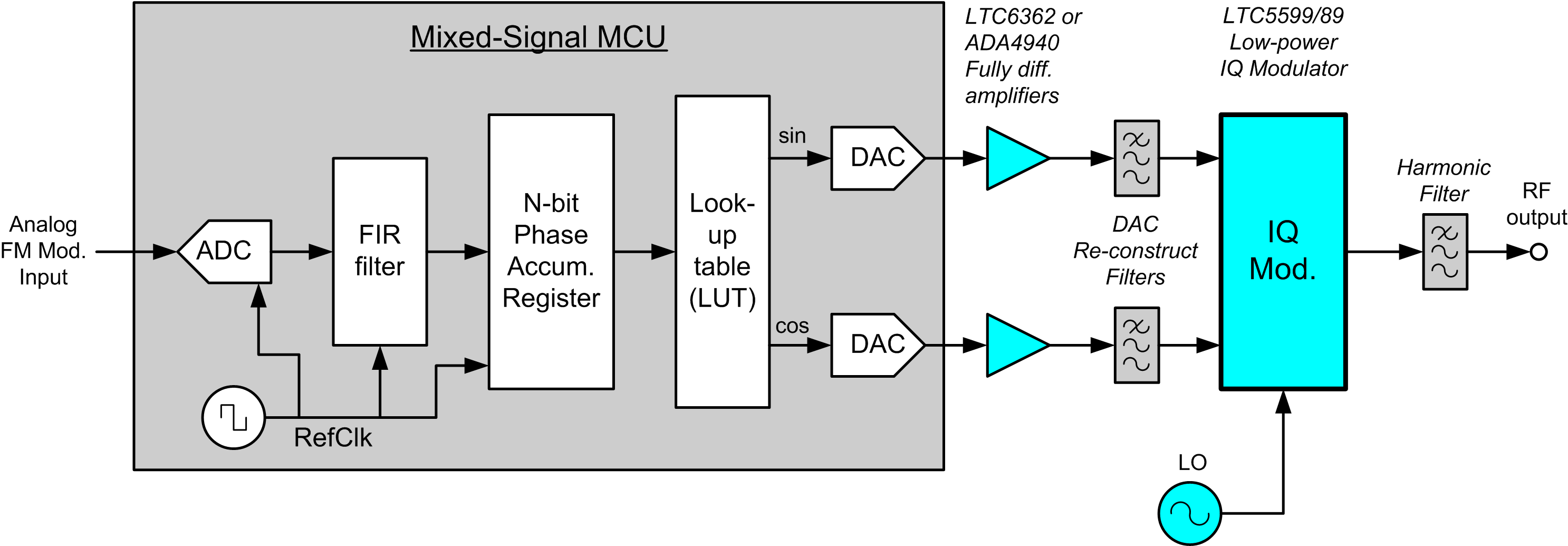

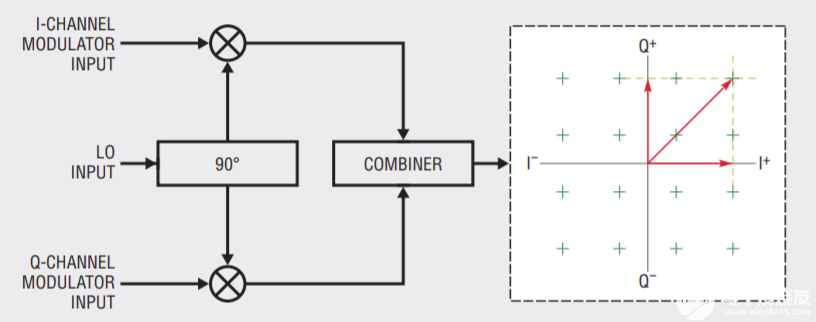

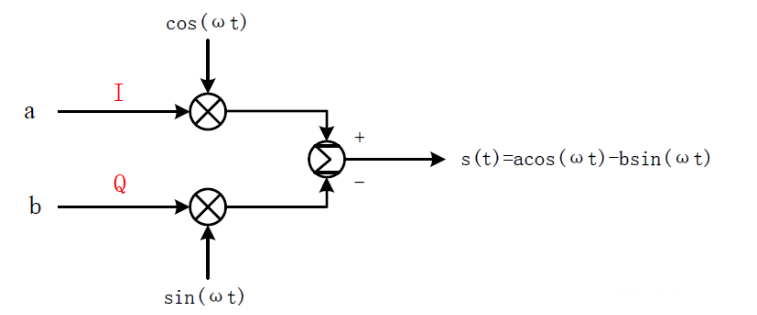

相位翻轉系統主要由IQ 調制器、FPGA 功能板和光電轉換模塊組成,如圖2~3所示。

圖2 相位翻轉系統原理圖

圖3 相位翻轉系統實物圖

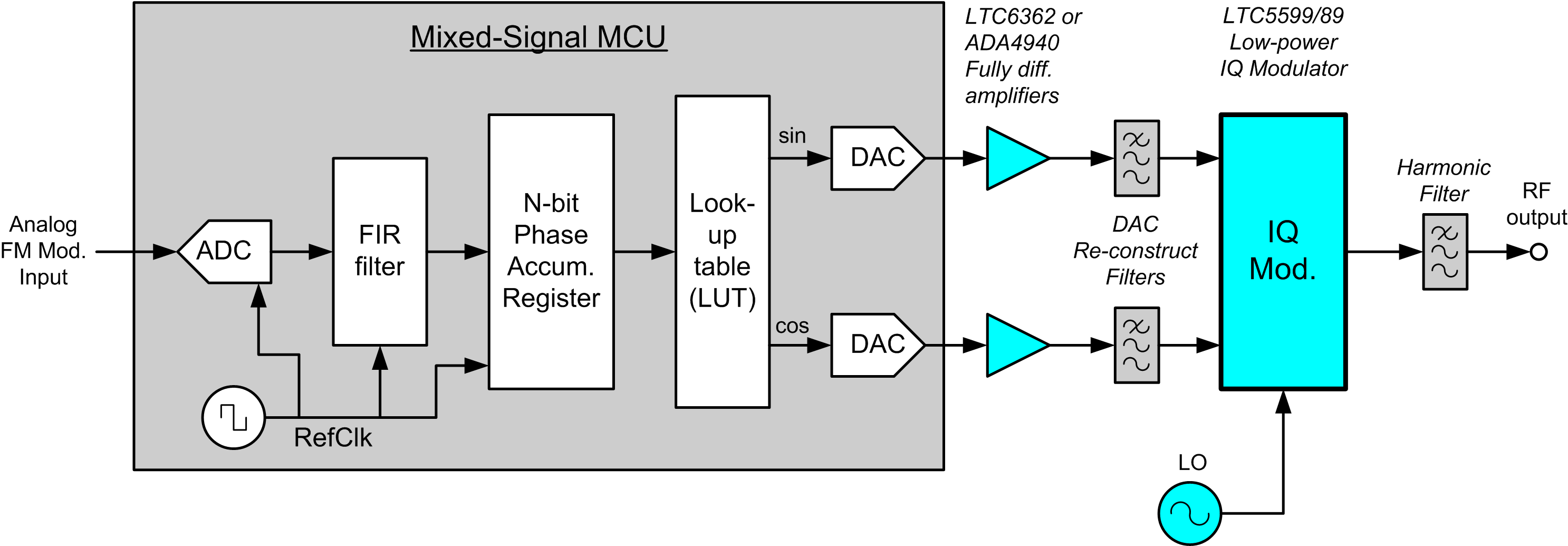

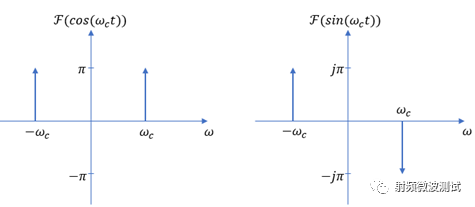

國內外相關實驗室的相位翻轉系統普遍采用PSK(phaseshiftkeying)開關或跳相控制電路作為跳相執行器件[7-9],我們選擇IQ 調制器,主要原因是它有同相(I)和正交(Q)兩個控制信號,有生成復雜幅相調制模式的潛力;其次,當IQ 信號幅度為零時,調制器的射頻輸出是截止的,可用于整個直線加速器裝置的快速聯鎖保護[10]。IQ 調制器采用了Pulsar Microwave公司的IDOH-01-45,其LO 載波頻率為2~4GHz,通道帶寬為100MHz,IQ 幅度、相位穩定度分別優于為1dB和8°,通道隔離度為30dB,駐波比小于1.5。光電轉換模塊接收來自于加速器時序系統的光脈沖信號,轉換為電信號輸入FPGA 單元,作為觸發信號。FPGA 系統采用一塊Xilinx-Vertex5的FPGA 開發板搭配高速可擴展ADDA 板。FPGA 內部鎖相環倍頻模塊(PLL)最高可產生200MHz的時鐘信號,為保證FPGA 時序穩定性,將內部時鐘設定為100MHz。高速ADDA 擴展板在Vertex5FPGA 平臺上可實現14位的模數、數模轉換。圖4為FPGA 和DAC的功能框圖。

圖4 FPGA和DAC功能框圖

利用硬件描述語言(VerilogHDL語言)在ISE軟件開發環境下,調用FPGA 內的相關模塊如PLL模塊、DAC模塊、BUFER模塊等編寫了相位翻轉信號的邏輯控制程序。DAC脈沖輸出信號的生成采用了FPGA的狀態機模式。無觸發信號時,FPGA 狀態機處于0狀態,寫入高速DAC板的值保持為0;受到高電平觸發后,FPGA 開始執行內部時鐘為100MHz的狀態機,以100MHz的數據刷新率將編輯好的賦值表寫入DAC板,輸出兩路脈沖電平信號,賦值表寫完后狀態機回歸0狀態。

3 IQ 控制信號的調試

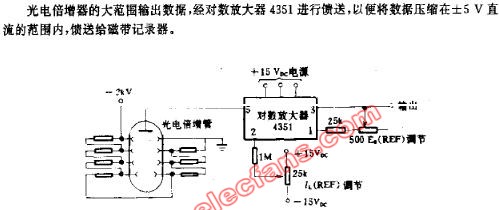

高速DAC板采用了隔離變壓器將DAC芯片的差分輸出轉變為單端輸出,就時間積分而言,輸出信號中無直流分量,這給脈沖直流電平信號的生成帶來一定的困難。為此構建了如圖5所示的IQ 控制信號調試系統,依據相位翻轉系統輸出信號的幅相監測結果,調整DAC賦值表。功率幅值監測采用Agilent8990B峰值功率計,相位監測采用IQ 解調器和示波器。經過反復調試,最終得到如圖6所示的DAC賦值表(兩路DAC相同),其對應的DAC板模擬輸出即IQ 控制信號如圖7所示,相位翻轉系統輸出RF信號的幅相特性如圖8~9所示。

圖5 IQ控制信號調試系統

圖6 DAC賦值表

圖7 DAC輸出的IQ控制信號

從圖8可以看出,功率幅值在4μs脈沖內保持一致,說明相位跳變后信號的功率未發生變化。調整移相器,使IQ 解調器的LO 和RF信號在脈沖的前3μs保持同相,Q 輸出為零,I 為正極值(圖9(a)),后1μs的Q值依然為零,而I 信號跳變為負極值,說明相位變化了180°。將移相器相移90°,得到圖9(b)的IQ 波形,I 信號在相位跳變前后均為零值,而Q 信號的極性發生了改變。由于相位翻轉的絕對精度不是系統關鍵性指標,未對翻轉相位進行精確測量,但依據以上測量結果,可基本確定翻轉相位在180°±2°范圍內。對調制器IQ 脈沖電平信號進行了長期監測,其穩定度達到±0.1%,對應的翻轉相位的穩定度優于±0.5°。

圖8 翻轉系統RF輸出信號的幅度包絡

圖9 解調器輸出的IQ信號波形

由于DAC輸出電路的隔直特性,IQ 控制電平的負脈沖有較長的下降過程(總時間積分為零),導致RF脈沖拖尾。對此我們調整了相位翻轉系統后的固態放大器(SSA)的時序和脈沖長度,將拖尾部分予以截斷,其實現過程如圖10所示。

圖10 相位翻轉系統和SSA的時序以及輸出信號波形

從以上IQ 控制信號的調試過程可以得出,DAC板的交流輸出方式對FPGA 的功能發揮產生了極大的限制,數字信號波形(賦值表)與實際模擬輸出信號完全不同,給控制信號的邏輯編程過程帶來了較大的困難,而且某些比較復雜的信號可能無法生成。

4 在線測試結果

直線加速器全系統安裝結束后,開啟相位翻轉系統和速調管,對能量倍增器進行了在線調諧,并用峰值功率計測量能量倍增器輸出功率波形和增益。經測試,6臺能量倍增器的增益均超過7dB,最高達到7.54dB(圖11)。經長期運行監測,能量倍增器功率增益的穩定度為±0.1dB,這說明能量倍增器和相位翻轉系統都達到了設計指標。

圖11 SLED輸出功率波形圖

5 結 論

基于FPGA 和IQ 調制器的相位翻轉系統產生了SLED 工作所需的4 μs 相位翻轉RF 脈沖信號,相位翻轉精度約180°±2°,穩定度達到±0.5°,SLED的能量增益最高達到7.54dB,增益的長期穩定性達到±0.1dB,整個能量倍增系統的各項指標滿足設計要求。

通過相位翻轉系統的研制,證明了FPGA 可以產生微波系統控制所需的高速幅相調制信號,因此即將開展研制的800MeV 直線加速器微波數字低電平反饋控制系統擬采用FPGA 方案。同時我們也意識到DAC板的交流輸出方式不利于高速復雜控制信號的產生。但目前市場上尚無合適的高速高精度、直流輸出的DAC板。對此我們已和相關FPGA 研發單位聯合開展了高速直流FPGA 專用DAC擴展板的研制工作。

電子發燒友App

電子發燒友App

評論