摘要:針對機械設備運行中的振動監控,設計振動信號采集系統,提出了一種基于FPGA的振動信號采集系統的設計方案。重點闡述了系統硬件結構組成、信號調理電路和數據采集模塊的設計,同時對A/D采樣的控制邏輯進行了討論。經試驗驗證表明,該系統可達到采樣率10 K每秒、采集精度16位,能夠滿足實時性和精度要求。

隨著生產機械、運輸機械或工程結構向著高速、高效、高精度和大型化發展,機械設備的任何部件出現故障都可能降低加工精度,帶來較大的經濟損失,甚至危及人身安全。機械部件的振動狀態監測已成為生產中的一個必不可少的環節,并對相應機械部件進行早期的故障預測。文中采用FPGA為核心開發振動信號采集系統,對數據采集模塊及通訊模塊進行了同步設計。

1 總體設計

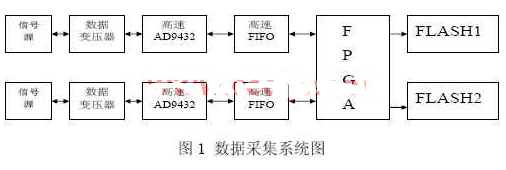

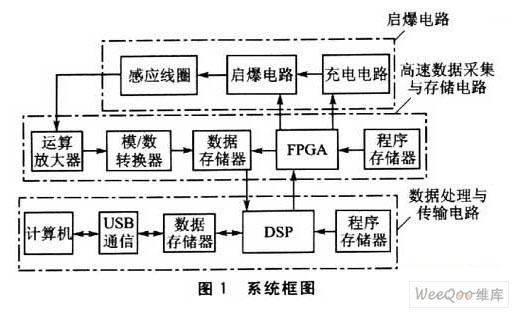

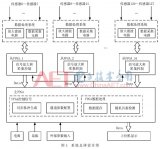

振動信號采集系統以FPGA芯片為核心,通過A/D轉換芯片采集振動信號,然后通過RS-422串行總線接口將采集的數據傳輸給上位機,在故障診斷軟件以作出相應的診斷處理。振動信號采集系統的硬件按照功能模塊可以劃分為信號調理電路、A/D轉換電路、FPGA控制邏輯和RS-422接口轉換電路,系統硬件結構如圖1所示。

系統硬件各個功能模塊的作用如下:

1)信號調理電路:信號調理電路主要對由集成電路壓

電式(Integrated Circuit Piezoelectricity,ICP)加速度傳感器采集到的振動信號進行調理驅動、放大和抗混疊濾波處理,使模數轉換器(Analog to Digital Converter ADC)芯片能夠獲取該振動信號,并作出進一步處理工作。

2)A/D轉換電路:A/D轉換電路將經過信號調理的信號進行模/數轉換,并將轉換結果傳送至FPGA進行數據采集,此功能電路決定了整個系統的分辨率和采集精度。

3)FPGA控制邏輯:FPGA芯片是該主控模塊的核心部分,控制振動信號的采集和數據傳輸,此功能電路控制著系統的采樣周期。

4)RS422接口轉換電路:將A/D轉換后的數字信號,通過RS422總線傳輸到上位機。

2 硬件電路設計

2.1 恒流源電路

系統采用ICP集成電路壓電式加速度傳感器檢測被測設備的振動信號,它將傳統壓電加速度傳感器和放大器集于一體,供電和信號輸出共用同一根電纜,通過恒流源為其供電,輸出信號經過信號調理電路后連接單片機進行測試,使采集系統得到了簡化,減少電纜的數量,同時省去了電荷放大器,降低了成本。

ICP傳感器所需的供電電源必須能夠提供18~30 V的直流電壓以及2~20 mA的恒定電流。由于傳感器共用電源線與信號輸出線,所以它的輸出信號會包含一個8~14 V的直流偏置電壓,通過去耦電容濾除信號中的直流分量。

本系統采用TI公司的三端可調恒流源器件LM334芯片。LM334為單片三端可調恒流源,實際應用中,改變連接電阻就可構成不用獨立電源的兩端理想電流浮置源,改變R可以改變恒流源的電流值,其公式為:

系統中設置為LM334的工作電壓28 V,電阻R標稱值33 Ω,輸出電流為2 mA。

2.2 信號調理模塊的設計

2.2.1 隔離、放大電路設計

ICP加速度傳感器輸出信號包含有直流偏置電壓,電路設計隔直電容C1和C2濾除此直流分量,然后采用精密儀表運算放大器芯片實現對模擬信號的放大處理,通過調節外部比例電阻可完成增益從1至10 000之間的任意選擇。 隔離、放大電路的原理圖如圖2所示。

N1為精密儀表運算放大器,其增益值依據下式可計算得出:

式中:G為電壓放大增益;Rref為比例參考電阻,單位Ω。

現階段取Rref開路,即Rref=∞,計算可知G=1。

R1、R2為輸入端匹配電阻,標稱值4.7 kΩ。

R3、R4為開路接地電阻,標稱值1 MΩ。

C1、C2為輸入端隔直電容,標稱值0.1μF,額定電壓值50 V。通過C1,C2和R3,R4構成的高通電路,-3 dB截至頻點是15.92 Hz,對信號進行隔直處理,同時不影響采集信號。

C3、C4、C5為精密儀表運算放大器輸入端的濾波電容,標稱值為0.001μF、0.01μF、0.001μF,與R1、R2構成低通電路,對共模信號的-3 dB截至頻點是33.87 kHz,對于差模信號的-3 dB截至頻點是1 610 Hz,有效的濾除進入采集電路的干擾信號。

2.2.2 抗混濾波電路設計

經過放大處理后的振動信號會混雜有高頻干擾信號,這些高頻信號就會產生頻率混疊現象,造成采集系統的精度下降。

抗混濾波電路采用二階壓控電壓源低通濾波電路,濾波器的截止頻率則由電阻R1、R2和電容C1、C2控制。二階低通濾波電路的原理圖如圖3所示。

濾波電路設計參數如下:

R1=R2=15 kΩ,R3=R4=10 kΩ,C1=C2=10nF;

二階低通濾波電路的傳遞函數為:

式中:A(s)為開環增益;Q為等效品質因數;ωn為電路的特征角頻率s。

其中Avf=1+R3/R4=2,Q=1/(3-Avf)=1>0,故A(s)的極點全部位于左半s平面,電路不會產生自激震蕩。

另一方面,由濾波電路傳遞函數可得幅頻響應表達式為:

可以計算出,其在ω/ωn=10時,幅頻特性曲線有-40 dB的衰減,電路的幅頻響應具有較好的低通特性,濾波器截止頻率f=1/2πRC≈1 062 Hz。

2.3 數據采集模塊的設計

數據采集模塊主要圍繞A/D轉換芯片展開設計,系統選用單通道的16位A/D轉換芯片進行采樣,采樣頻率最高分別可達100 ksps。目標采樣的振動信號的頻率一般為低頻信號,設計采集系統的檢測5 kHz頻率范圍內的振動信號,按照香農采樣定理,A/D轉換芯片的采集速率應不小于10 k每秒,100 ksps的A/D轉換芯片完全可以滿足本系統需求。

由于A/D轉換芯片輸出電平為5 V的TTL電平,需要配置電平轉換芯片,將5 V電平轉換為3.3 V電平,再送入現場可編程門陣列(Field Programmable Gate Arrays,FPGA),完成對采集電路中A/D轉換芯片的時序控制。

A/D轉換公式:A/D芯片采集到的數值為0~0xFFFF的16位二進制數,對應-10 V~+10 V的電壓,電壓轉換計算公式如下:

2.4 通訊模塊的設計

RS-422驅動電路由UART協議、電平轉換和接口電路組成,其中協議轉換由可編程邏輯實現。串行接口數據格式為:1個起始位,8個數據位,奇校驗位,1個停止位,工作頻率設計在115 200 bps。FPGA芯片將采集到的AD轉換后數據轉發到RS-422總線。由于AD采集芯片為16 bit,所以在設置先發數據的高8 bit,再發送數據的低8 bit。

3 可編程邏輯設計

3.1 可編程邏輯功能設計

系統選用Xilinx公司的Spartan系列芯片,此系列具有性能優良、性價比高、非易失性等特點,擴展了片上flash存儲器,用于FPGA的配置和非易失性數據的存儲,具有充足的資源滿足采集系統的邏輯功能需求。可編程邏輯采用模塊化的設計思想,設計AD采集模塊和UART協議模塊。

3.1.1 AD采集模塊

FPGA芯片控制A/D轉換芯片RC信號為低電平,AD芯片啟動轉換工作,同時BUSY信號輸出低電平,轉換完成后AD芯片BUSY信號重置高電平,AD芯片數據輸出端口輸出有效數據。FPGA檢測到BUSY信號,將AD芯片轉換后的數據存入UART發送寄存器中。

3.1.2 UART協議模塊

UART協議模塊采用的是串口通訊協議軟核,其設計特點是:

1)波特率為9 600 bps~115.2 kbps可通過軟件編程;

2)內建128字節接收FIFO和128字節發送FIFO;

3)數據長度、停止位長度、奇偶校驗可通過軟件進行編程;

4)計算公式:波特率=外部時鐘(14.745 6 MHz)/(16×分頻因子)。

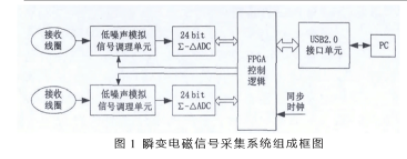

3.2 系統功能邏輯設計

采集系統的控制設計為周期自動采集,一次采樣過程如下:首先啟動A/D轉換器,然后判斷BUSY信號轉換是否結束,A/D轉換結束后FPGA讀取A/D轉換結果,并直接存入UART發送寄存器,然后等待延時到下一周期,并開始第二次采集,自動完成振動信號的采集。FPGA的自動控制流程如圖4所示。

?

系統設計采樣周期為200 us,遠大于A/D轉換芯片的轉換時間,決定了系統的采樣速率5 kHz,可滿足大多數機械部件振動信號的采集要求。采樣周期控制由FPGA使用的時鐘計數決定,此系統使用的時鐘為10 MHz,系統的周期誤差來源于晶振本身的誤差,系統使用的晶振初始頻率一溫度誤差為50 PPM,具有極小的時鐘誤差。

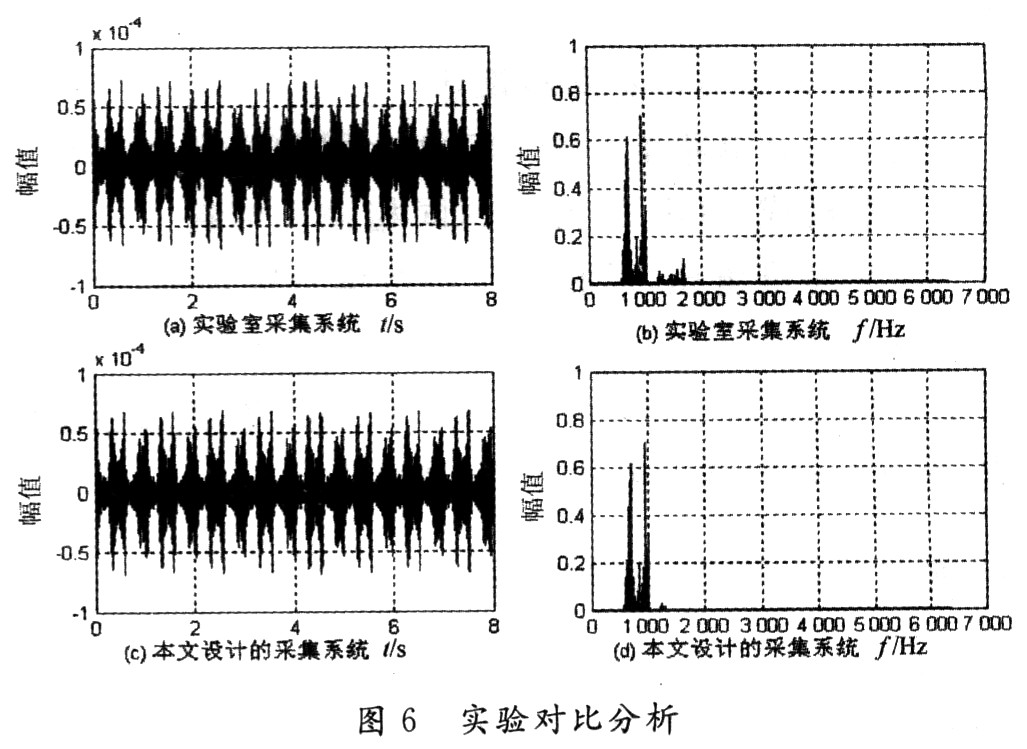

4 系統功能驗證

為了驗證振動信號采集系統的各項功能,本研究采用由振動臺輸出的正弦信號作為系統的輸入激勵,由本文設計的采集系統對該振動信號進行采集,從而檢驗系統采集功能的準確性。試驗中用到的設備情況如下:使用隨機振動臺,施加21.5 Hz正弦振動激勵信號,幅值分別為1 g和2 g兩種激勵,使用振動傳感器精度為104 mV/g,測量結果為圖5和圖6所示。

?

由圖可以看出,信號的幅值接近激勵值,與輸入的正弦激勵信號基本一致,進行頻率分析,進行FFT轉換后頻率為21.5 Hz,與輸入激勵信號的頻率一致。實驗結果表明,該振動信號采集功能正確。

5 結論

本文提出的FPGA的振動信號采集系統具有硬件組成少,可在不需要中央處理器即可完成數據的自動采集,且具備并行可擴展性,功能移植性好,同時具有較高的采樣周期和精度,可以滿足大多數工業與航空領域中振動采集的要求。

電子發燒友App

電子發燒友App

評論