先給大家簡單快速地介紹一下 Vivado 集成設計環境,即 IDE。當打開 Vivado 工程后,會有一個工程概要,向您介紹工程的設置、警告和錯誤信息以及工程的一般狀態。

2012-04-25 09:00:43 6408

6408 本在生產力方面進行了兩大改進。Vivado設計套件2013.1版本新增了一款以IP為中心的設計環境,用以加速系統集成;而其提供的一套完整數據庫,則可加速C/C++系統級設計和高層次綜合(HLS)。

2013-04-08 15:08:54 902

902 跨時鐘域路徑分析報告分析從一個時鐘域(源時鐘)跨越到另一個時鐘域(目標時鐘)的時序路徑。

2020-11-27 11:11:39 5449

5449

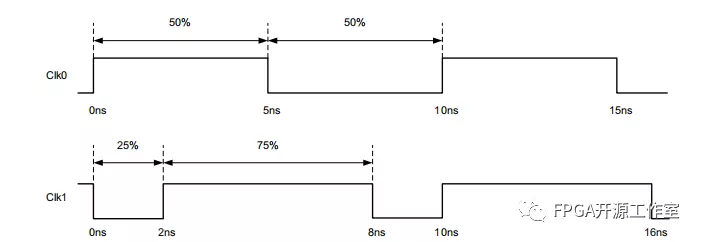

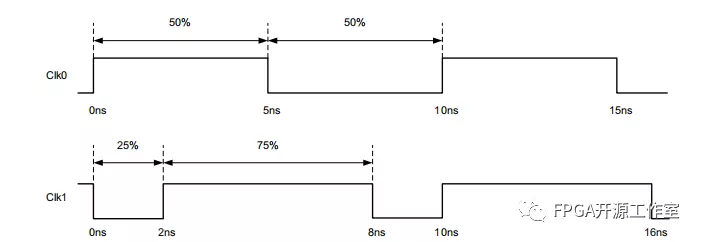

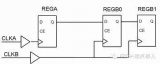

1. 時鐘介紹 在數字設計中,時鐘代表從寄存器(register)到寄存器可靠傳輸數據的時間基準。Xilinx Vivado集成設計環境(IDE)時序引擎使用ClocK特征計算時序路徑要求,并通過

2020-11-29 10:51:45 5359

5359

作者:Mculover666 1.實驗目的 通過例程探索Vivado HLS設計流 用圖形用戶界面和TCL腳本兩種方式創建Vivado HLS項目 用各種HLS指令綜合接口 優化Vivado HLS

2020-12-21 16:27:21 3153

3153 Xilinx的新一代設計套件Vivado相比上一代產品ISE,在運行速度、算法優化和功能整合等很多方面都有了顯著地改進。但是對初學者來說,新的約束語言XDC以及腳本語言Tcl的引入則成為了快速掌握Vivado使用技巧的最大障礙,以至于兩年多后的今天,仍有很多用戶缺乏升級到Vivado的信心。

2022-09-14 09:09:56 1526

1526 FPGA中的BUFGCE_DIV/BUFG_GT以及Versal中的MBUFG/BUFG_GT等。對于這類時鐘,Vivado會自動創建時鐘,并不需要用戶手工通過create_generated_clock創建。

2024-01-11 09:50:09 400

400

,只有在時鐘的支持下,電子產品才能正常工作。 ? 那么時鐘產品有哪些種類,它們分別有什么特性,工程師在選用的時候需要注意些什么呢,我們今天就來一起聊一聊。 ? 時鐘產品的分類 時鐘產品主要分為兩大類,一類是異步時鐘產品,

2021-09-06 07:18:00 6088

6088 Vivado概述 / 251.3.1 Vivado下的FPGA設計流程 / 251.3.2 Vivado的兩種工作模式 / 261.3.3 Vivado的5個特征 / 30參考文獻 / 31第2章

2020-10-21 18:24:48

1.實驗目的通過例程探索Vivado HLS設計流用圖形用戶界面和TCL腳本兩種方式創建Vivado HLS項目用各種HLS指令綜合接口優化Vivado HLS設計來滿足各種約束用不用的指令來探索

2021-11-11 07:09:49

Vivado下set_multicycle_path該怎樣去使用呢?在兩個不同時鐘主頻的情況下使用set_multicycle_path的情況是怎樣的?

2022-02-16 08:00:49

和Vivado的綜合性能,管腳位置與電平約束完全一致。PS:若時鐘和管腳約束直接敲命令,兩者除了語法,沒有明顯區別。6、綜合實現——點評:Vivado默認策略情況下從綜合到生成bit共計23分50秒。而

2021-01-08 17:07:20

)無法通過放置階段,會產生大量的放置錯誤,如下所示。基本上,Vivado不能放置與時鐘相關的任何原語 -BUFG,BUFH,PLLE2_ADV,GTHE2_COMMON等。設計針對xc7vx690t

2018-11-02 11:32:44

Vivado綜合可以理解多種多樣的RAM編寫方式,將其映射到分布式RAM或塊RAM中。兩種實現方法在向RAM寫入數據時都是采取同步方式,區別在于從RAM讀取數據時,分布式RAM采用異步方式,塊RAM

2020-09-29 09:40:40

Vivado 設計分為 Project Mode 和 Non-project Mode 兩種模式,一般簡單設計中,我們常用的是 Project Mode。在本手冊中,我們將以一個簡單的實驗案例,一步一步的完成 Vivado的整個設計流程。

2023-09-20 07:37:39

圖所示:接下來的頁面是選擇用于采樣待測信號的時鐘域,Vivado會自動識別出各個待測信號所屬的時鐘域并將其自動設定為其采樣時鐘,例如,我們剛剛添加的這“led_OBUF”和“cnt”兩個信號就屬于

2023-04-17 16:33:55

你好,我在Win10中使用vivado 2016.2 for zynq7020。我的時鐘方案是zynq PS FCLK_CLK0-->時鐘向導IP輸入(Primitive PLL)的輸入。合成

2018-11-05 11:40:53

想到要寫這一系列關于工具和方法學的小文章是在半年多前,那時候Vivado?已經推出兩年,陸續也接觸了不少客戶和他們的設計。我所在的部門叫做“Tools & Methodology

2023-09-20 06:31:14

使用的是18.1版本的VIVADO。 這次的練習選擇的是ZYNQ的芯片,原本工程是工作在100MHz的時鐘,但是作為練習,我們可以把時鐘調到一個極限的程度來進行優化。 首先,打開一個工程,更改一下時鐘頻率,使得工程

2018-08-22 11:45:54

距離2016智能硬件開發者創客大會召開的日子越來越近了,作為本次亮點之一的第十九屆電路保護與電磁兼容技術工作坊將會給我們帶來什么樣的驚喜了,據小編了解此次工作坊將會分為兩大會場,前有各大知名公司老總

2016-03-29 14:00:52

VIVADO DEBUG FLOATING LICENSE

2023-03-30 12:04:13

VIVADO DEBUG NODE-LOCKED LICENSE

2023-03-30 12:04:13

VIVADO DEBUG FLOATING LICENSE

2023-03-30 12:04:13

VIVADO DEBUG NODE-LOCKED LICENSE

2023-03-30 12:04:13

現代高級雷達系統正在受到多方面的挑戰——頻率分配上的最新變化導致許多雷達系統的工作頻率非常接近通信基礎設施和其他頻譜要求極高的系統。

2019-07-22 07:50:19

RTC時鐘具有哪些特性應用?

2021-10-13 06:09:16

RTC時鐘具有哪些特性? RTC正常工作的一般配置步驟是怎樣的?

2021-11-23 06:52:26

STM32F407之時鐘、頻率、存儲概述文章目錄STM32F407之時鐘、頻率、存儲概述1.整體特性1.1存儲器組織架構1.2 內嵌SRAM1.3Flash和自舉程序2.電源3.時鐘介紹3.1系統

2021-08-02 07:24:37

為什么要使用thumb模式,與ARM相比較,Thumb代碼的兩大優勢是什么?

2022-11-02 14:17:55

問候!我正在使用Virtex7 / XC7V2000T / ***1925。我有兩個clcoks,pipe3_clk和ulpi_clk,連接到同一時鐘區域的兩個CCIO,X1Y7。但Vivado在

2020-07-16 14:18:54

伺服電機分為交流伺服和直流伺服兩大類。交流伺服電機的基本構造與交流感應電動機(異步電機)相似。在定子上有兩個相空間位移90°電角度的勵磁繞組Wf和控制繞組WcoWf,接恒定交流電壓,利用施加到Wc上

2021-06-28 09:45:02

,設置的主時鐘頻率是250M,實際送給cpu的也是這個頻率,但是看了一下nuclei studio里面的system_hbirdv2.c文件里面的時鐘頻率確是80M,這倆已經不匹配了,但是在vivado

2023-08-11 11:18:54

單片機最小系統電路包括哪兩大類

2023-10-31 07:28:49

我在vivado 2016.3中看到了以下地方的錯誤錯誤:[放置30-675]支持全局時鐘的IO引腳和BUFG對的次優放置。如果此子設計可接受此子優化條件,則可以使用.xdc文件中

2018-11-09 11:37:33

如果我有兩個設計項目,讓我調用項目A和B.現在我需要做的是將這兩個項目組合成一個項目C,如何在Vivado中進行這種組合?提前致謝。以上來自于谷歌翻譯以下為原文If I have two

2019-02-28 09:26:27

秒(100 Mhz)關閉和打開一個LED,我這樣做是為了驗證如何更改ZYNQ的時鐘頻率使用vivado的約束。這是我放在.xdc文件中生成不同的時鐘頻率set_property PACKAGE_PIN

2020-04-01 08:46:16

完整的小車控制程序,包括上位機和下位機兩大部分attach://147399.rar

2013-07-20 09:31:30

。標準的嵌入式系統架構有兩大體系,RISC處理器和CISC處理器體系。嵌入式主板分為比較常見的兩大類:1、基于X86的嵌入式主板,Intel的X86 處理器就屬于CISC體系,(一般使用INTEL、AMD、威盛、或其他產家的...

2021-12-16 06:41:20

邏輯門控無法映射到Vivado中的一個時鐘區域時,BUFHCTRL能夠復制自身并將邏輯映射到多個時鐘區域嗎?謝謝,雨翔

2020-07-27 14:26:34

大家好,據我了解,Vivado僅在合成過程的地點和路線部分使用多線程。那么,真正改變vivado性能的方法(性能=從頭開始合成項目的速度+在vivado合成時在計算機上執行其他工作的能力)主要是核心

2019-04-25 06:33:01

嗨,我想創建一個設計,我需要2Mhz clk,我想用16Mhz輸入時鐘的vivado套裝中的“時鐘向導”IP核生成它。根據Xilinx手冊(下面的鏈接),這可以通過CLKOUT4_CASCADE選項

2020-07-27 06:32:48

量級。如要對晶振老化漂移優化,需要得到晶振在上級時鐘良好、時鐘板處于鎖定狀態下的漂移,通過讀取鎖定電壓值即可。 需要特別注意的是,這個鎖定值會在晶振老化漂移的基礎上疊加晶振溫度特性的影響,如果晶振溫度

2013-12-17 16:10:55

你好,有沒有辦法在新的vivado IDE中使用時鐘向導(v3.5)實現“舊”生成的IP?特別是我遇到了問題,當我自動升級時,有一些輸出缺失。例如,是否在較新版本的時鐘向導(v5.1)中實現了一個輸出,它具有與向導生成的CLK_VALID輸出相同的功能(v3.5)?謝謝!

2020-07-29 10:52:20

本帖最后由 iioloii 于 2022-4-24 10:44 編輯

分析A、B兩個信號(由同一個時鐘驅動)之間的時序時發現源時鐘和目的時鐘經過相同的元件或走線的延時是不一樣的,不知道為甚會是

2022-04-24 10:32:49

誰來闡述一下電感式傳感器可分為哪兩大類?

2019-11-18 15:14:40

癌細胞生長速度比一般人快24倍;我國每年出生的2000萬兒童中,有35萬為缺陷兒,其中25萬為智力殘缺,有專家認為,電磁輻射是影響因素之一因此,電磁輻射問題越來越受到世界各國的普遍重視。高爾生教授在他的《空調使用對***質量的影響》中指出,電磁輻射對人體的危害,表現為熱效應和非熱效應兩大方面。

2019-05-31 06:45:55

`錯誤提示截圖放在二樓,用vivado14.4寫了個1×8和8×8矩陣相乘的程序,調用了64個ip核乘法器,IO口用的有些多。綜合和實現網表都能成功,就是仿真總是提示這兩個錯誤,仔細檢查了幾遍程序

2020-04-26 19:21:25

vivado自己設置的工程目錄本身比較深,而文件路徑太深會導致某些奇怪的錯誤。這是windows系統本身的特性決定的,windows的路徑名不能超過260字節,所以大家設計的時候一定注意路徑名長度

2019-09-11 11:52:42

親愛的大家,我現在正在使用Vivado 2013.3。我試圖將PL結構時鐘從1 MHZ更改為500KHZ。 (1 MHZ下沒問題)但是,Vivado在運行綜合時崩潰了。對我來說減少PL結構時鐘非常重要,因為我打算在一個時鐘周期內收集更多的XADC數據。我該怎么辦?謝謝!

2020-03-25 08:40:07

在Vivado中通過set_clock_groups來約束不同的時鐘組,它有三個選項分別是-asynchronous,-logically_exclusive

2017-02-08 08:39:49 919

919

Suite? 和 ?UltraFast?? 設計方法加速設計生產力: .????????? 查看 UltraFast? 設計方法指南 ·????????? 觀看? Vivado? 快速入門視頻 ,深入了解 ?Vivado Design Suite? 的各種工具與特性,視

2017-02-09 09:06:11 295

295 搭載“部分重配置技術”的 Vivado 2017.1 的 HLx 版本軟件現在可以下載了!

2018-07-08 06:23:00 4534

4534 此篇文章里,我們將通過使用InTime來檢驗Vivado 2017.1和Vivado2016.4之間的性能對比。 概要:分別進行了3個Vivado 2017.1對Vivado2016.4的性能測試

2018-07-04 11:23:00 9674

9674

無論此刻你是一個需要安裝Xilinx Vivado工具鏈的入門菜鳥,還是已有license過期的Vivado老鐵,今兒咱就借著這篇文章,把學習「Vivado如何獲取License」這檔子事兒給說通透咯~ 手把手教程,分三部分講述。

2018-07-03 09:54:00 58889

58889

vivado設計套件資料

2017-10-31 09:49:03 43

43 Xilinx的新一代設計套件Vivado相比上一代產品ISE,在運行速度、算法優化和功能整合等很多方面都有了顯著地改進。但是對初學者來說,新的約束語言XDC以及腳本語言Tcl的引入則成為了快速掌握

2017-11-18 03:52:01 4675

4675

時鐘擴展對使用賽靈思Vivado設計套件的工程師來說是一個很大的挑戰,但不是一個不可逾越的障礙。隨著越來越多的賽靈思用戶開始使用Vivado?設計套件,部分用戶對未擴展時鐘表示困惑。那么什么是未擴展

2017-11-18 13:28:01 761

761 1 Vivado HLS簡介 2創建一個Vivado-HLS工程 2.1打開Vivado HLS GUI 2.2創建新工程 在 Welcome Page, 選擇Create New Project

2017-12-04 10:07:17 0

0 現在的硬件設計中,大量的時鐘之間彼此相互連接是很典型的現象。為了保證Vivado優化到關鍵路徑,我們必須要理解時鐘之間是如何相互作用,也就是同步和異步時鐘之間是如何聯系。 同步時鐘是彼此聯系的時鐘。

2018-05-12 10:15:00 19563

19563 時序分析在FPGA設計中是分析工程很重要的手段,時序分析的原理和相關的公式小編在這里不再介紹,這篇文章是小編在練習Vivado軟件時序分析的筆記,小編這里使用的是18.1版本的Vivado。 這次

2019-09-15 16:38:00 5787

5787

本視頻將指您介紹如何使用Vivado設計套件中的交互式“IO Pin Planning”和“Device Exploration”功能。具體來說,IO規劃包括:在設計中創建,配置,分配和管理IO端口以及時鐘邏輯

對象。該視頻教程描述了在設計流程的不同階段如何執行IO規劃的步驟。

2018-11-20 06:36:00 4709

4709 2015年Club Vivado開發者大會的預覽。

2018-11-20 11:51:25 992

992 該視頻演示了如何使用Vivado IP Integrator組裝具有多個時鐘域的設計。

它顯示了Vivado中的設計規則檢查和功能如何幫助用戶自動執行此流程。

2018-11-27 07:40:00 3539

3539 了解report_design_analysis,這是一個新的Vivado報告命令,可以獨特地了解時序和復雜性特征,這些特性對于分析時序收斂問題很有價值。

2018-11-26 07:01:00 3314

3314 了解如何使用2014.1中引入的新激活許可為Vivado工具生成許可證。

另外,了解Vivado 2014.1中的許可更改如何影響您,以及如何在激活客戶端中使用新的Vivado License Manager

2018-11-22 07:10:00 2614

2614 在Vivado Design Suite中,Vivado綜合能夠合成多種類型的屬性。在大多數情況下,這些屬性具有相同的語法和相同的行為。

2019-05-02 10:13:00 3750

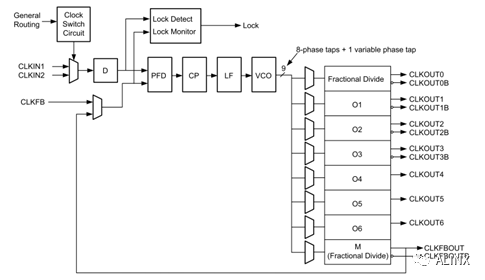

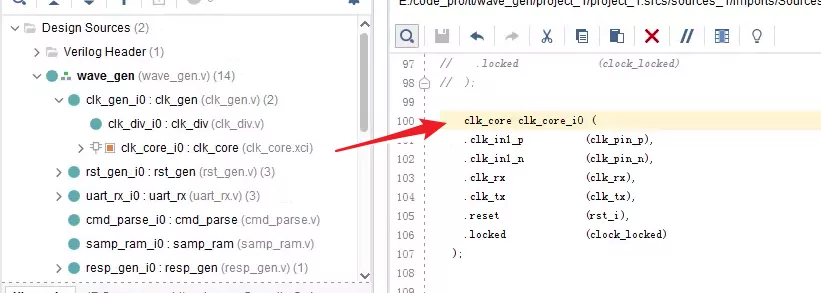

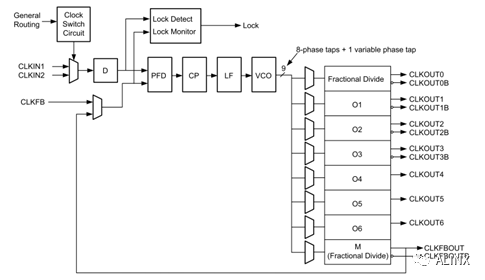

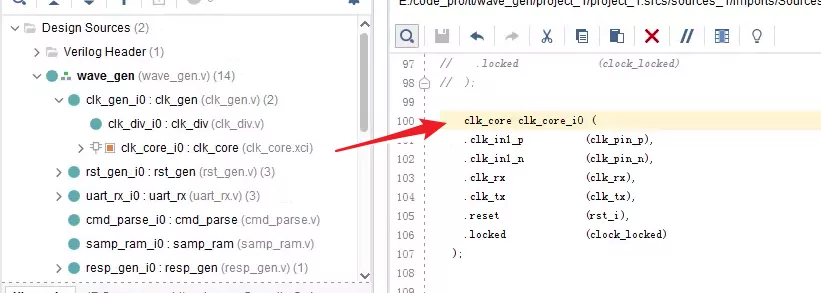

3750 在開發PL時一般都會用到分頻或倍頻,對晶振產生的時鐘進行分頻或倍頻處理,產生系統時鐘和復位信號,下面就介紹一下在vivado2017.3中進行PL開發時調用IP的方法。

2018-12-22 14:26:38 4468

4468 在開發PL時一般都會用到分頻或倍頻,對晶振產生的時鐘進行分頻或倍頻處理,產生系統時鐘和復位信號,這是同步時序電路的關鍵,這時就需要使用到時鐘向導IP,下面就介紹一下在vivado中進行PL開發時調用IP的方法。

2018-12-22 15:14:38 10069

10069 關于Vivado Dashboard的功能可閱讀這篇文章(Vivado 2018.3這個Gadget你用了嗎)Vivado 2019.1的Dashboard功能進一步增強。

2019-06-12 14:49:24 7677

7677

交互式時鐘域的交叉分析:該功能支持設計人員在設計早期階段調試CDC問題。結合Vivado設計套件的交互式時序分析和交叉探測特性,CDC分析功能可提供強大的時序分析和調試功能,并加速產品上市進程。

2019-08-01 09:14:54 1862

1862 ,但是也有類似的功能模塊,通過PLL可以倍頻分頻,產生其他很多時鐘。本實驗通過調用PLL IP core來學習PLL的使用、vivado的IP core使用方法。

2022-02-08 15:13:17 3306

3306

Vivado 的XDC設置輸出延時 Vivado 的XDC設置輸出延時,用于輸出伴隨時鐘和數據的,數據是由系統時鐘125M驅動,伴隨時鐘是由125M經過Pll相位移動-90度。 設置輸出時鐘

2021-06-09 17:28:01 3888

3888

,只有在時鐘的支持下,電子產品才能正常工作。 那么時鐘產品有哪些種類,它們分別有什么特性,工程師在選用的時候需要注意些什么呢,我們今天就來一起聊一聊。 時鐘產品的分類 時鐘產品主要分為兩大類,一類是異步時鐘產品,它的

2021-09-08 14:23:44 4940

4940 Vivado License Manager在使用Vivado License Manager時,如果通過如下圖所示方式指定license的路徑時,要保證路徑僅包含ASCII字符而沒有中文字

2021-09-12 15:15:19 5055

5055 和FPGA設計進行連接。由于VIO核與被監視和驅動的設計同步,因此應用于設計的時鐘約束也適用于VIO核內的元件。當使用這個核進行實時交互時,需要使用Vivado邏輯分析特性。 接下來將介紹VIO的原理及應用,內容主要包括設計原理、添加VIO核、生成比特流文件和下載并調試設計。 設計原理

2021-09-23 16:11:23 6841

6841

【流水燈樣例】基于 FPGA Vivado 的數字鐘設計前言模擬前言Vivado 設計流程指導手冊——2013.4密碼:5txi模擬

2021-12-04 13:21:08 26

26 Vivado下set_multicycle_path的使用說明 vivado下多周期路徑約束(set_multicycle_path)的使用,set_multicycle_path一般...

2021-12-20 19:12:17 1

1 對于7系列FPGA,需要對GT的這兩個時鐘手工約束:對于UltraScale FPGA,只需對GT的輸入時鐘約束即可,Vivado會自動對這兩個時鐘約束。

2022-02-16 16:21:36 1229

1229

數字設計中,“時鐘”表示在寄存器間可靠地傳輸數據所需的參考時間。Vivado的時序引擎通過時鐘特征來計算時序路徑需求,通過計算裕量(Slack)的方法報告設計時序空余。時鐘必須有合適的定義,包含如下特性:

2022-04-20 10:40:48 7882

7882 Vivado 2022.1已正式發布,今天我們就來看看其中的一個新特性。

2022-07-03 17:00:25 1785

1785 Vivado可以導出腳本,保存創建工程的相關命令和配置,并可以在需要的時候使用腳本重建Vivado工程。腳本通常只有KB級別大小,遠遠小于工程打包文件的大小,因此便于備份和版本管理。下面把前述腳本升級到Vivado 2020.2為例,討論如何升級Vivado工程腳本。

2022-08-02 10:10:17 1542

1542 今天介紹的是vivado的三種常用IP核:時鐘倍頻(Clocking Wizard),實時仿真(ILA),ROM調用(Block Memory)。

2023-02-02 10:14:01 2529

2529 Xilinx的新一代設計套件Vivado相比上一代產品 ISE,在運行速度、算法優化和功能整合等很多方面都有了顯著地改進。但是對初學者來說,新的約束語言 XDC 以及腳本語言 Tcl 的引入則成為

2023-04-15 09:43:09 958

958 今天推出Xilinx已發布的《Vivado使用誤區與進階》系列:用TCL定制Vivado設計實現流程。

2023-05-05 09:44:46 674

674

使用“時鐘校準去歪斜”時,在 Vivado 中會顯示下列消息以指明是否啟用該功能特性

2023-07-07 14:14:50 347

347

vivado開發軟件自帶了仿真工具,下面將介紹vivado的仿真流程,方便初學者進行仿真實驗。

2023-07-18 09:06:59 2137

2137

電子發燒友網站提供《Vivado設計套件用戶:使用Vivado IDE的指南.pdf》資料免費下載

2023-09-13 15:25:36 3

3 電子發燒友網站提供《Vivado Design Suite用戶指南:I/O和時鐘規劃.pdf》資料免費下載

2023-09-13 15:10:58 0

0 在Vivado中禁止自動生成BUFG(Buffered Clock Gate)可以通過以下步驟實現。 首先,讓我們簡要了解一下什么是BUFG。BUFG是一個時鐘緩沖器,用于緩沖輸入時鐘信號,使其更穩

2024-01-05 14:31:06 454

454

正在加载...

電子發燒友App

電子發燒友App

評論